113

Изобретение относится к вычислительной технике, а именно к цифровым устройствам для вычисления синуса числа с плавающей запятой, и может быть использовано в составе арифметико-логических устройств цифровых вычислительных машин, а также в виде самостоятельного вычислительного устройства.

Цель изобретения - расширение диапазона входных чисел.

Сущность изобретения заклк чается в том, что расширение динамического диапазона происходит за счет того, что синус числа А р а вычисляется в форме с плавающей запятой, т.е. S inA р b,

где р - основание системы счислени

(р 2 k 1,2,3,4)-; oi|(5 - порядок, представленный

двоичными разрядами, а,Ь - мантисса, представленная

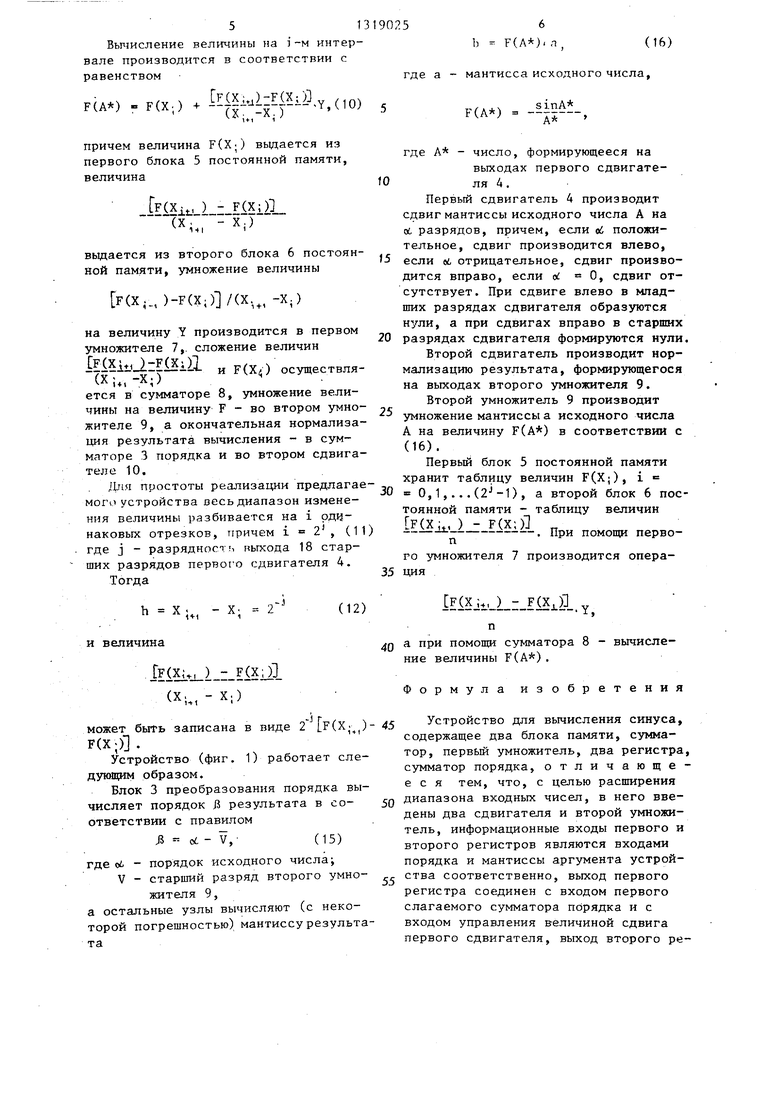

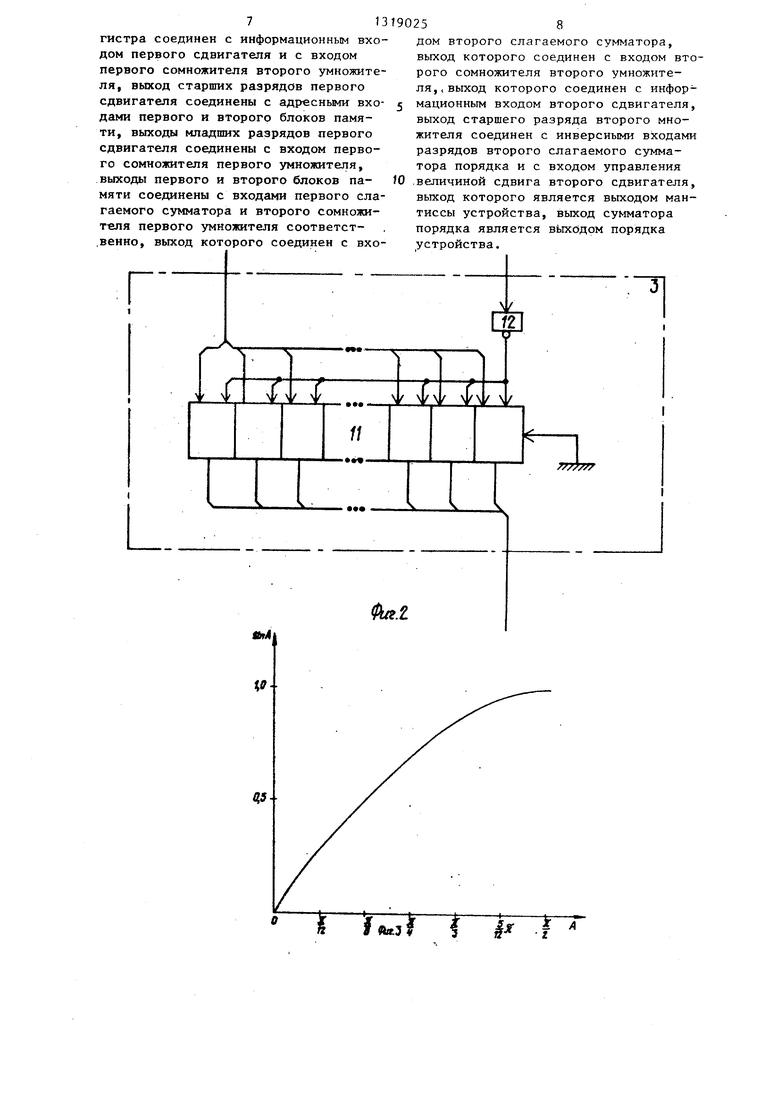

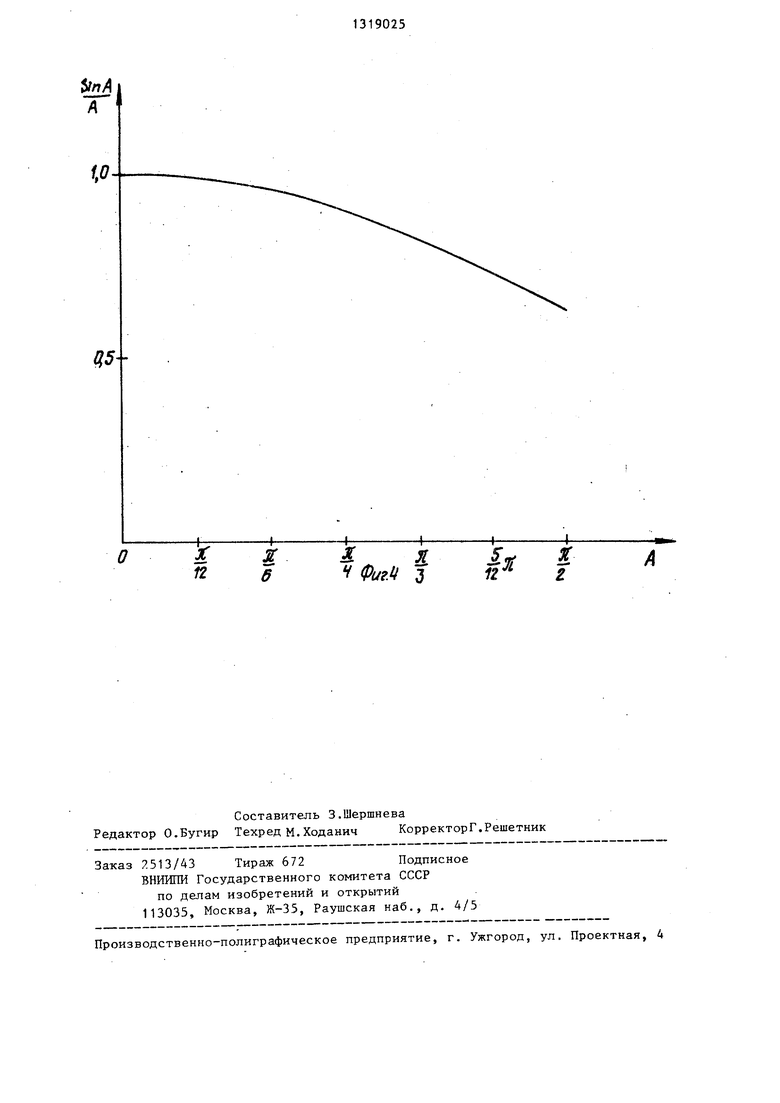

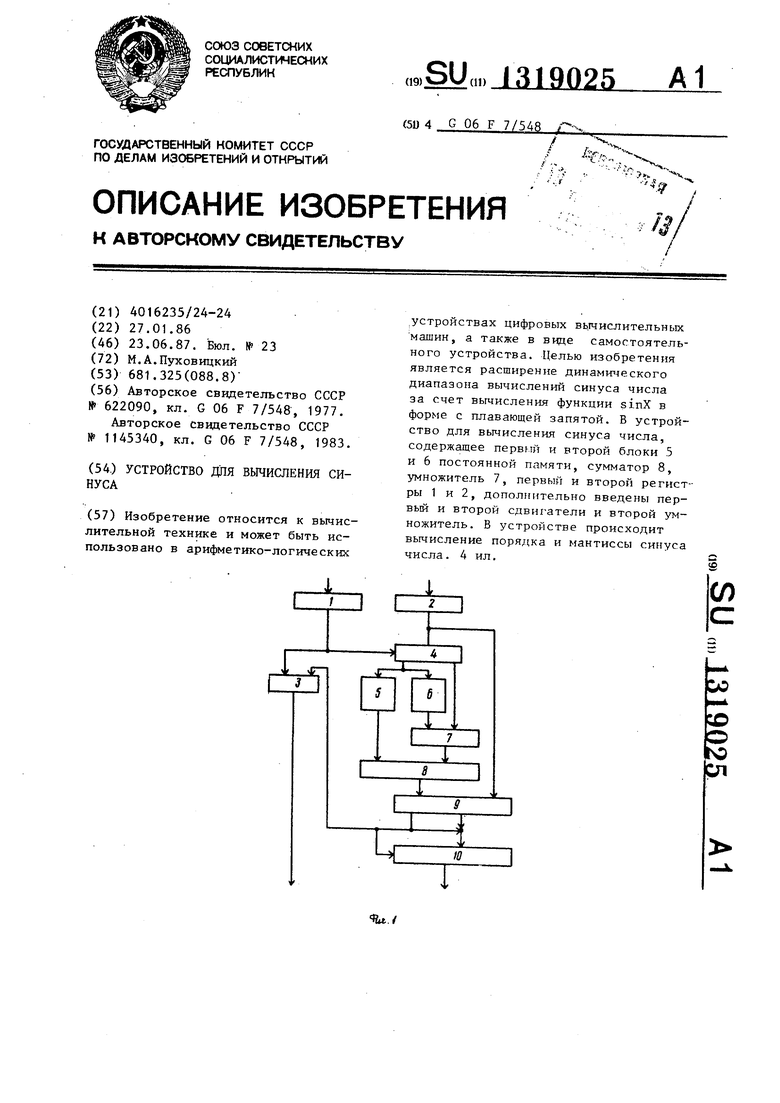

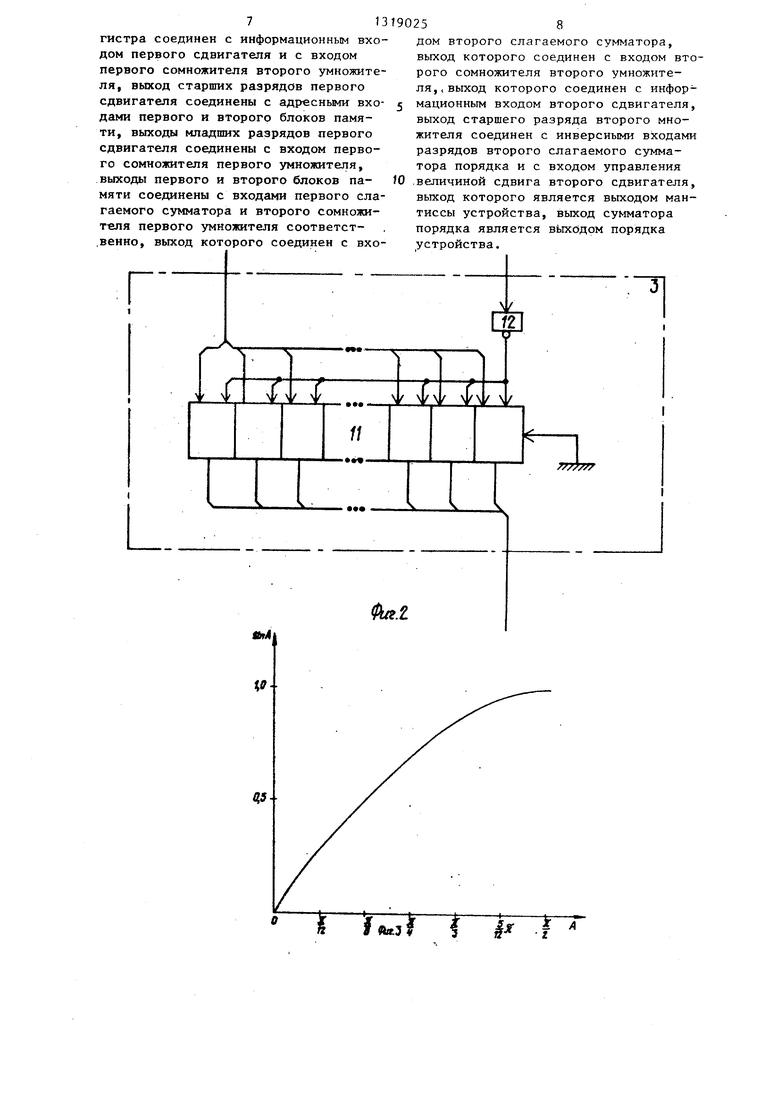

двоичными разрядами. На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - структурная схема блока преобразования порядкаJ на фиг. 3 - j-pa фик функции sin А н фиг. 4 - графи функции (sinA)A.

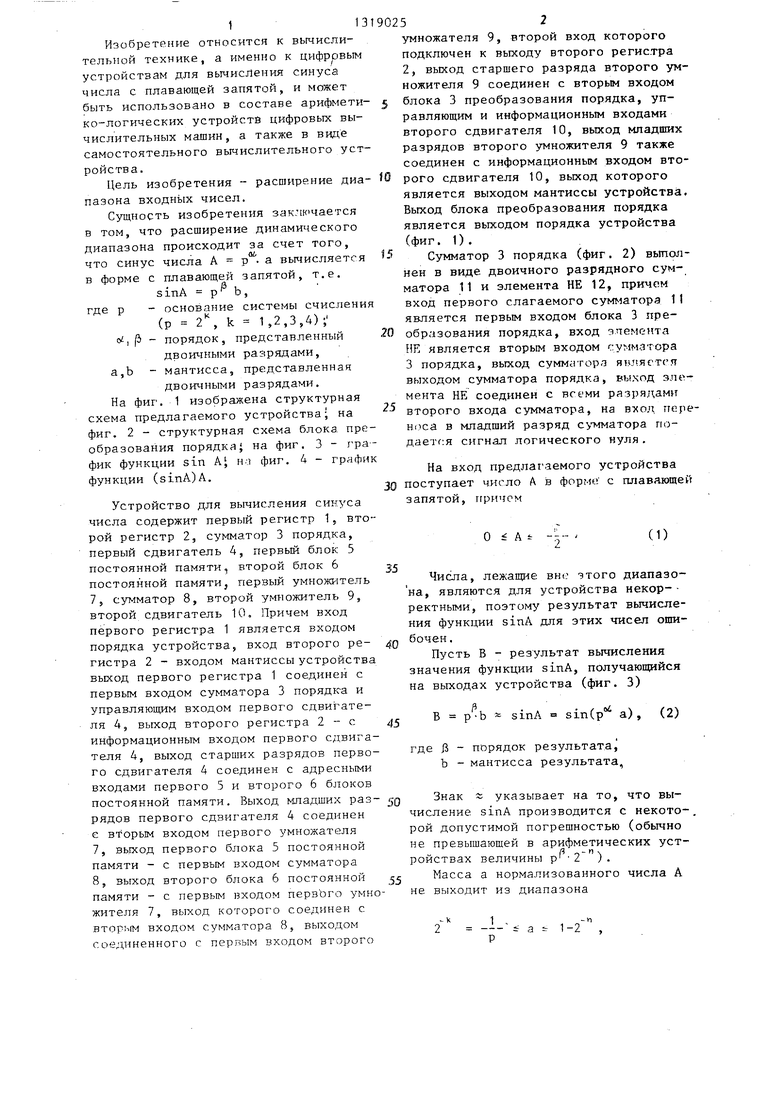

Устройство для вычисления синуса числа содержит первый регистр 1, второй регистр 2, сумматор 3 порядка, первый сдвигатель 4, первый блок 5 постоянной памяти, второй блок 6 постоянной памяти, первый ум 1ожитель 7, сумматор 8, второй умножитель 9, второй сдвигатель 10, Причем вход первого регистра 1 является входом порядка устройства, вход второго регистра 2 - входом мантиссы устройства выход первого регистра 1 соединен с первым входом сумматора 3 порядка и управляющим входом первого сдвигате- ля 4, выход второго регистра 2 - с информационным входом первого сдвига- теля 4, выход старших разрядов первого сдвигателя 4 соединен с адресными входами первого 5 и второго 6 блоков постоянной памяти. Выход младших разрядов первого сдвигателя 4 соединен с вторым входом первого умножателя

7,вьгход первого блока 5 постоянной памяти - с первым входом сумматора

8,выход второго блока 6 постоянной памяти - с первым входом первЬго умножителя 7, выход которого соединен с вторым входом сумматора 8, выходом соединенного с первым входом второго

90252

умножателя 9, второй вход которого подключен к выходу второго регистра 2, выход старшего разряда второго умножителя 9 соединен с вторым входом

5 блока 3 преобразования порядка, управляющим и информационным входами второго сдвигателя 10, выход младших разрядов второго умножителя 9 также соединен с информационным входом втоШ рого сдвигателя 10, выход которого является выходом мантиссы устройства. Вьгход блока преобразования порядка является вьпсодом порядка устройства (фиг. 1).

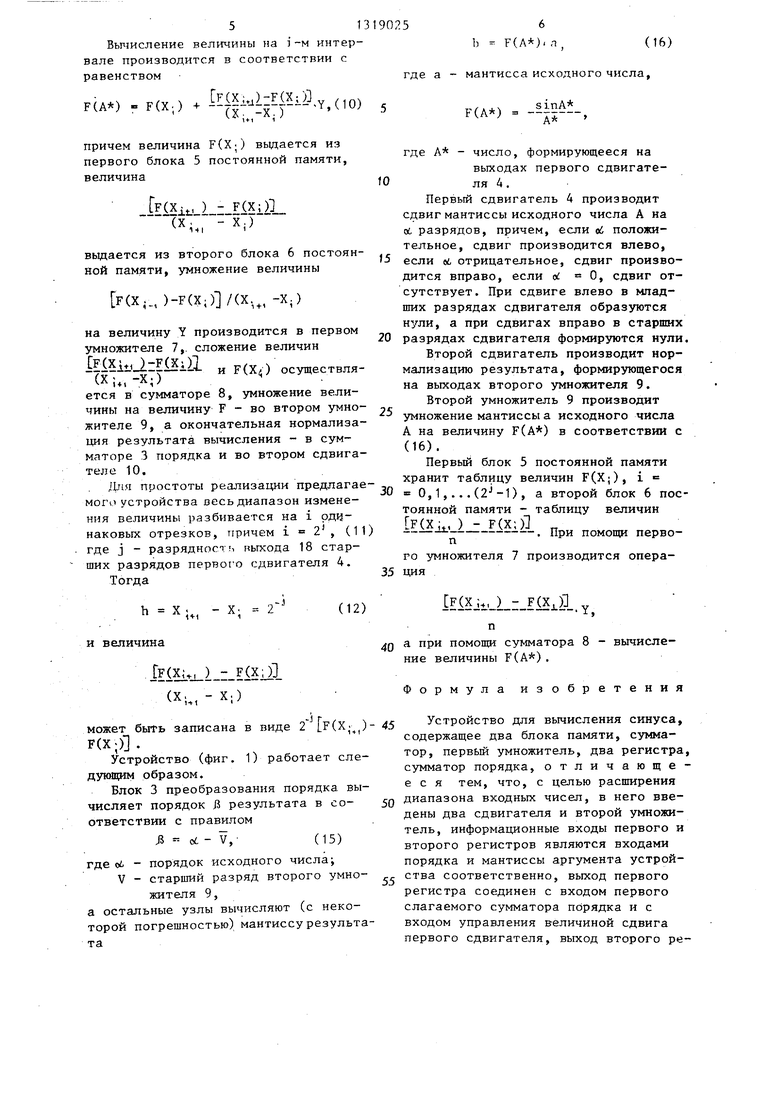

- Сумматор 3 порядка (фиг. 2) вьтол- нен в виде двоичного разрядного сумматора 11 и элемента НЕ 12, причем вход первого слагаемого сумматора 1 является первым входом блока 3 пре0 образования порядка, вход элемента НЕ является вторым входом сумматора 3 порядка, выход сумматора ять -ястся выходом сумматора порядка, выход элемента НЕ соединен с всеми разрядами второго входа сумматора, на вход поре- Н(.)са в младший разряд с мматора подается сигнал логического куля.

На вход предлагаемого устройства 30 поступает число А в форме: с плавающей запятой, ггричем

25

О f --(1)

Числа, лежащие вне этого диапазо- на, являются для устройства некор- - ректными, поэтому результат вычисления функции sitiA для этих чисел ошибочен .

Пусть В - результат вычисления значения функции sinA, получающийся на выходах устройства (фиг. 3)

а

Б р-Ь sinA sin(p а), (2)

где и - порядок результата Ъ - мантисса результата,

50

Знак

указывает на то, что вычисление sinA производится с некоторой допустимой погрешностью (обычно не превышаюш;ей в арифметических устройствах величины ). jj Масса а нормализованного числа А не выходит из диапазона

. 1-2- Р

в этом же диапазоне должна нахбдить- ся н мантисса результата.

Известно (фиг. 4), что для диапазона (1)

sinA А

06366197,

(3)

Представим sinA в вид

, . sinA

SinA -7 А.

А

Подставим (4) в (2)

./5

p b s inA

sinA A

г л- .t.t.t. ,

Учитывая (3), имеем

sinA Fvp . a p b,,

(6)

S, b.

-промежуточное значение порядка

-промежуточное значение ман- 25 тиссы;

F (sinA)/А и 1 5г F Э 0,6366197 интервале (1), причем

30 35 40

и I об

Ь; a-F. ,

Проведя околчательную нормализацию результата промежуточных вычислений, получаем результат

sinA

P.b,

где Д - порядок результата после

нормализации

b - мантисса результата после нормализации, т.е. b 1.

Эти рассуждения справедливы для любых р, так как

min(F)

min()

P

где p 2 , к 1,2,3,4.

Из (6) следует, что сановной частью процесса вычисления величины sinA является процесс вычисления промежуточной величины F (sinA)/А, где А а.

Величина F в предлагаемом устройстве вычисляется в два этапа. На первом этапе число А в первом сдвигателе переводится из формы с плавающей запятой в форму с фиксированной запятой, т.е. при of. О происходит сдвиг м антиссы а на об разрядов вправо, при oi О происходит сдвиг мантиссы а на oi разрядов влево, при oi 0 сдвиг отсутствует. На втором этапе происходит собственно вычисление величины F в соответствии с

F F(x) + F (X)-Y,

(7)

где F(X) - значение функции в точках, определяемых числами, формирующимися на выходе старших разрядов первого сдвигателя;

F (Х) - значение производной функции в точках, определяемых числами, формирующимися на выходе старших разрядов первого сдвигателя; Y - число, формирующееся на

выходе младших разрядов первого сдвигателя; X - число, формирующееся на выходе старших разрядов первого сдвигателя. Таблица величин F(X;) хранится в первом блоке постоянной памяти, таблица величин F (X;) - во втором блоке постоянной памяти. Умножение величины F (X;) на величину Y происходит в первом умножителе, сложение ве- личин F(X;) и F (X ) Y происходит в сумматоре, на выходе которого формируется величина F. Умножение величины F на а происходит во втором умножителе, а окончательная нормализа- дня результата осуществляется во втором сдвигателе и блоке преобразования порядка.

Формирующееся на выходах первого сдвигателя число представляет собой сумму чисел X и Y, где X - число, формирующееся на выходе 18 старших разрядов первого сдвигателя 4; Y - число, формирующееся на выходе 21 старшего разряда первого сдвигателя 4. В предлагаемом устройстве весь диапазон изменения числа X разбит на i.отрезков. При этом для вычисления величины производится замена кривой (sinA/A), изображенной на фиг. 4, набором прямолинейных отрезков.

Дня любых Y. выполняется соотношение

А X ; + Y

(9)

51319025

Вьпшсление величины на i-м интервале производится в соответствии с равенствомгде а

F(A) F(X., )

lEiXluIlEiX;.) , ) i-v v 1ч , V lu;

(X. -X.)

причем величина F(Xj) выдается из первого блока 5 постоянной памяти, величина

(Xij.,))l

- (х,

вьщается из второго блока 6 постоян- ., Ной памяти, умножение величины

F(XJ., )-F(X;)/(x., -X.)

на величину Y производится в первом

умножителе 7,. сложение величин

-Т - -Ч-Т- и F(X4) осуществля- .л ;, -А;;

ется в сумматоре 8, умножение величины на величину F - во втором умно- жителе 9, а окончательная нормализация результата вычисления - в сумматоре 3 порядка и во втором сдвига- теле 10.

Для простоты реализации предлагае- мого устройства весь диапазон изменения величины разбивается на i рдч- наковых отрезков, причем , (11) где j - разрядность ньгхода 18 старших разрядов nepBOfo сдвигателя 4.

Тогда

X

-X; 2

-J

(12)

И величина

IZiXi),j

(X;,, -X;)

может быть записана в виде 2 LF(X )-

F(X;).

Устройство (фиг. 1) работает сле- дунмцим образом.

Блок 3 преобразования порядка вычисляет порядок R результата в со- ответствии с правилом

-В - об - V,- (15)

где oi - порядок исходного числа;

V - старший разряд второго умножителя 9,

а остальные узлы вычисляют (с некоторой погрешностью) мантиссу результата

b F(A).Л,(16)

мантисса исходного числа, sinA

F(A)

A

,

0

5

.

5

где А - число, формирующееся на

выходах первого сдвигателя А ,

Первый сдвигатель 4 производит сдвиг мантиссы исходного числа А на об разрядов, причем, если ой положительное, сдвиг производится влево, если ei отрицательное, сдвиг производится вправо, если аС. 0, сдвиг отсутствует. При сдвиге влево в младших разрядах сдвигателя образуются нзши, а при сдвигах вправо в старших разрядах сдвигателя формируются нули.

Второй сдвигатель производит нормализацию результата, формирующегося на выходах второго умножителя 9.

Второй умножитель 9 производит умножение мантиссы а исходного числа А на величину F(A) в соответствии с (16).

Первый блок 5 постоянной памяти хранит таблицу величин F(X;), i 0,1,...(2-1), а второй блок 6 постоянной памяти - таблицу величин

F(, ) - F(X;)1 „

. При помощи первоп

го умножителя 7 производится операция

F(,)(Xj.)

Y,

0

5

0

а при помощи сумматора 8 - вычисление величины F(A).

Формула изобретения

Устройство для вычисления синуса, содержащее два блока памяти, сумматор, первый умножитель, два регистра, сумматор порядка, отличающееся тем, что, с целью расширения диапазона входных чисел, в него введены два сдвигателя и второй умножитель, информационные входы первого и второго регистров являются входами порядка и мантиссы аргумента устройства соответственно, выход первого регистра собщинен с входом первого слагаемого сумматора порядка и с входом управления в-еличиной сдвига первого сдвигателя, выход второго ре713

гистра соединен с информационным входом первого сдвигателя и с входом первого сомножителя второго умножителя, выход старших разрядов первого сдвигателя соединены с адресными входами первого и второго блоков памяти, выходы младших разрядов первого сдвигателя соединены с входом первого сомножителя первого умножителя, выходы первого и второго блоков памяти соединены с входами первого слагаемого сумматора и второго сомножителя первого умножителя соответст- .вемно, выход которого соединен с вхоL.

258

дом второго слагаемого сумматора, выход которого соединен с входом второго сомножителя второго умножителя,, выход которого соединен с инфор- мационным входом второго сдвигателя, выход старшего разряда второго множителя соединен с инверсными входами разрядов второго слагаемого сумматора порядка и с входом управления

.величиной сдвига второго сдвигателя, выход которого является выходом мантиссы устройства, выход сумматора порядка является выходом порядка устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления косинуса числа | 1988 |

|

SU1522197A1 |

| Устройство для вычисления показательной функции | 1988 |

|

SU1536376A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1273921A1 |

| Устройство для вычисления корня @ -степени | 1986 |

|

SU1381494A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметико-логических устройствах цифровых вьтчислительных машин, а также в вцце самостоятельного устройства. Целью изобретения является расширение динамического диапазона вычислений синуса числа за счет вычисления функции sinX в форме с плавающей запятой. В устройство для вычисления синуса числа, содержащее первий и второй блоки 5 и 6 постоянной памяти, сумматор 8, умножитель 7, первый и второй регистры 1 и 2, дополнительно введены первый и второй сдвиг-атели и второй умножитель. В устройстве происходит вычисление порядка и мантиссы синуса числа. 4 ил.

I А

Ж б

X X У ФигМ 3

rt

г

Авторы

Даты

1987-06-23—Публикация

1986-01-27—Подача