Изобретение относится к вычислительной технике и может быть использовано при обработке массивов чисел.

Цель изобретения - сокращение аппаратурных затрат и повышение однородности устройства.

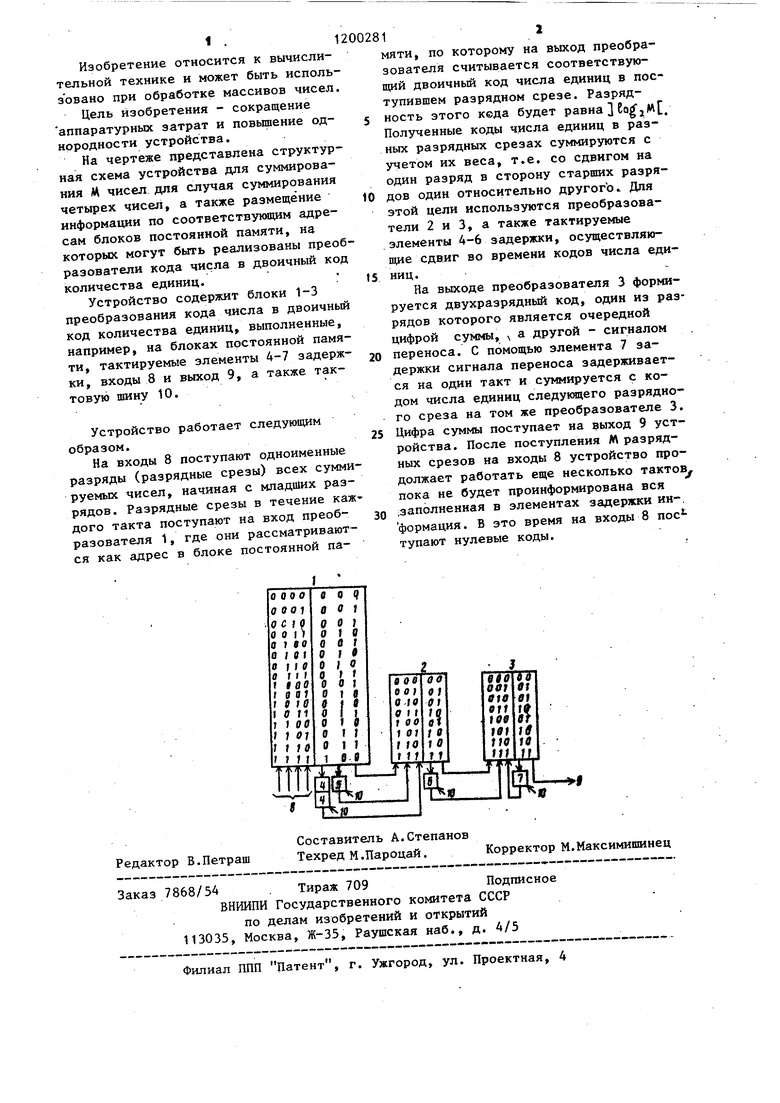

На чертеже представлена структурная схема устройства для суммирования М чисел для случая суммирования четырех 4Hceji, а также размещение информации по соответствукицим адресам блоков постоянной памяти, на которых могут быть реализованы преобразователи кода числа в двоичный код количества единиц.;

Устройство содержит блоки 1-3 преобразования кода числа в двоичньй код количества еданиц, выполненные, например, на блоках постоянной памяти, тактируемые элементы 4-7 задержки, входы 8 и выход 9, а также тактовую шину 10.

Устройство работает следующим образом.

На входы В поступают одноименные разряды (разрядные срезы) всех суммируемых чисел, начиная с младших разрядов. Разрядные срезы в течение каждого такта поступают на вход преобразователя 1, где они рассматриваются как адрес в блоке постоянной памяти, по которому на выход преобразователя считывается соответствующий двоичный код числа единиц в поступившем разрядном срезе. Разрядность этого кеда будет равна 3 6ogjM. Полученные коды числа единиц в разных разрядных срезах суммируются с учетом их веса, т.е. со сдвигом на один разряд в сторону старших разрядов один относительно другого.. Для этой цели используются преобразователи 2 и 3, а также тактируемые элементы 4-6 задержки, осуществляющие сдвиг во времени кодов числа единиц.

На выходе преобразователя 3 формируется двухразрядный код, один из разрядов которого является очередной цифрой суммы, X а другой - сигналом

переноса. С помощью элемента 7 задержки сигнала переноса задерживается на один такт и суммируется с кодом числа единиц следующего разрядного среза на том же преобразователе 3.

Цифра суммы поступает на выход 9 устройства. После поступления М разрядных срезов на входы 8 устройство продолжает работать еще несколько тактов, пока не будет проинформирована вся

;заполненная в элементах задержки ин-. формация. В это время на входы 8 пос тупают нулевые коды.

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное вычислительное устройство | 1985 |

|

SU1322261A1 |

| Ассоциативное устройство для суммирования массива чисел | 1988 |

|

SU1564615A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1988 |

|

SU1529457A2 |

| Устройство для преобразования количества единиц двоичного кода в код по модулю К | 1987 |

|

SU1527714A1 |

| Устройство для суммирования М чисел | 1989 |

|

SU1672439A1 |

| Устройство для преобразования по функциям Уолша | 1983 |

|

SU1137479A1 |

| Конвейерный сумматор | 1987 |

|

SU1427359A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Суммирующее устройство | 1990 |

|

SU1714591A1 |

УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ М ЧИСЕЛ, содержащее первый блок преобразования кода числа в двоичный код количества единиц, входы которого соединены с входами устройства, и тактируемые элементы задержки, причем выходы первого блока преобразования кода числа в двоичный код количества единиц с второго по п -и, где « - SogjMC, соединены с вxoдa ш соответствукнцих тактируемых элементров задержки, отличающееся т.ем, что, с целью сокращения аппаратурных затрат, оно дополнительно содержит 1C блоков преобразования кода числа в двоичный код количества единиц, где k равно числу логарифмирований, необходимых для выполнения соотношения v. С 2, причем выход каждого | -го разряда каждого j -го блока преобразования кода числа в двоичный код количества единиц соединен через ( - 1) тактируемых элементов задержки с соответствующим входом ( j 1)-го блока преобразования кода числа в двоичный код количества единиц, где ,...,ж, m- eogJeo|j...eo,M... -- --J i jpai выход первого разряда j -го блока преобразования кода числа в двоичный код количества единиц соединен с соответствукйцим входом (j + 1)-го блока преобразования кода числа в двоичный код количества единиц, выход старшего разряда V -го блока преобю разования кода числа в двоичный код количества единиц соединен через тактируемый злемент задержки с дою полнительным входом того же блока сю преобразования кода числа в двоичный код количества единиц, выход мЛад,шего разряда - с выходом устройства, а тактовые входы тактируемых элементов задержки соединены с тактовой шиной устройства.

| Электронные вычислительны машины и система: Справочник по цифровой вычислительной технике / Под ред | |||

| Б.М.Малиновского | |||

| Киев: Техника, 1980, с | |||

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-23—Публикация

1984-06-26—Подача