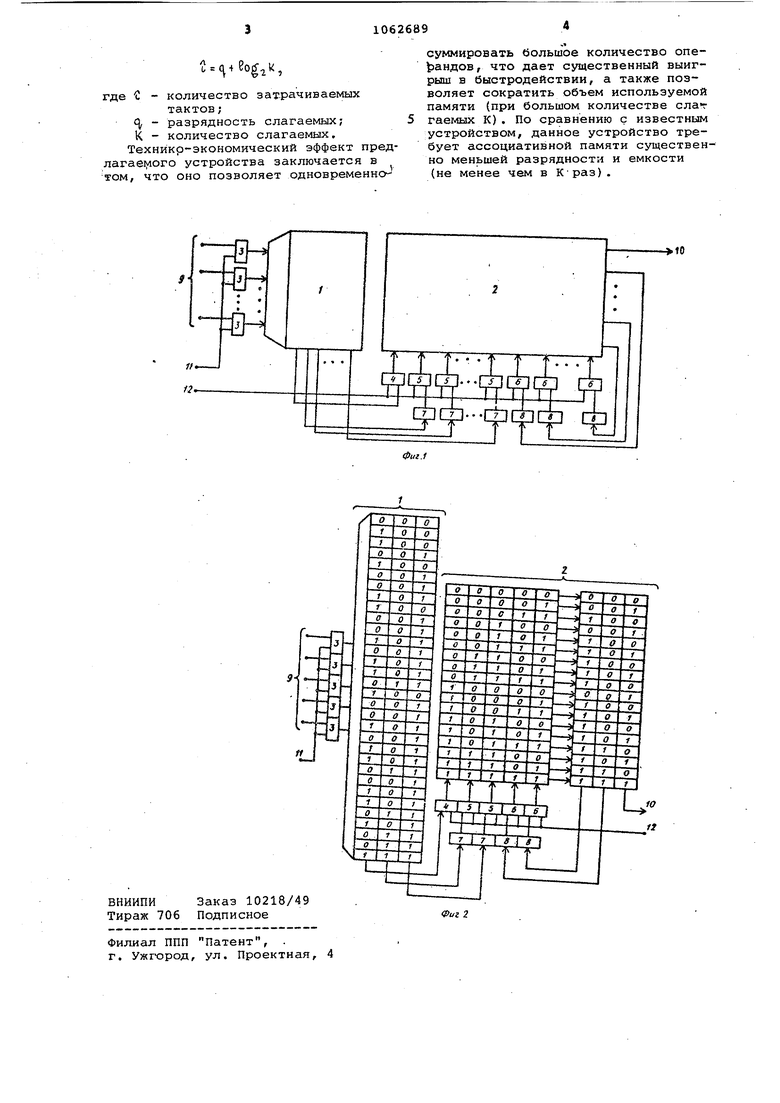

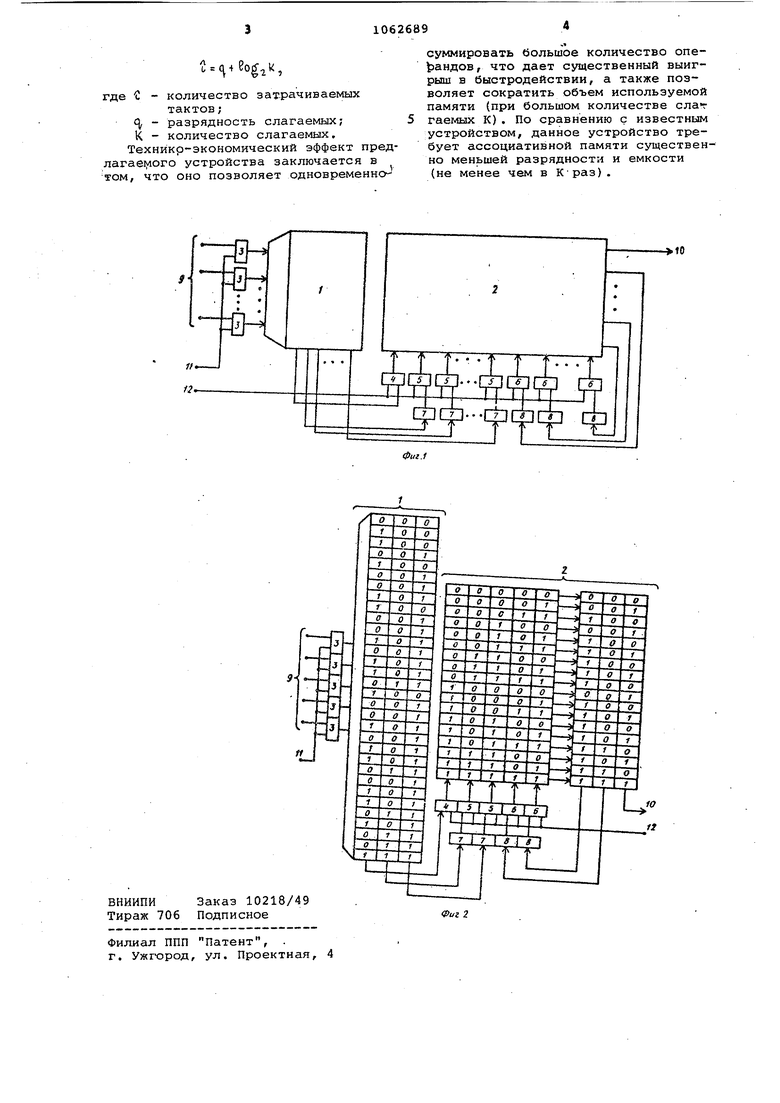

Изобретение относ.ится к вычислительной Технике и может использовать ся в устройствах обработки цифровой информации, Извест ю устройство, реализующее поразрядный способ суммирования нескольких чисел, содерх ащее ряды одноразрядных двоичных сумматоров, причем входы сумматоров каждого ряда соединены с выходами сумматоров предыдущего ряда ij . Недостатками устройства являются большой объем оборудования и неоднородность . Известна также реализация автомата Мура на базе ассоциативной памяти позволяющего осуществлять поразрядно сук1мирование нескольких чисел. Данно ycTpoiicTBo содержит ассоциативное запоминающее устройство, первый выход которого является выходом суммы ycTpoiiCTBa, разряды второго выхода ассоциативного запоминающего устройства через первые элементы задержки соединены с первыми, входами соответствующих элементов И первой группы, вторые входы которых подключены к первой шине синхронизации устройства,, а выходы к соответствующим раз ряда..-, первого входа опроса ассоциации ,чсго запоминающего устройства, pftSjJHMK .второго входа которого соеди нены свходами слагаемых устройств а 2 , Недостатком устройства являются большие аппаратурные затраты, .что BFjpa}i;aeTCH в больыом объеме ассоциа тнвного запоминающего устройства, ра рядность признаковой части которого равна в данном случае К , где К - число слагаемых, а объем ассоциа THj.K-iOH памяти равен 2 К слов. Целью изобретения .является сокращеипе а.П1аратурных затрат в сул1мирую щем устройстве. Поставленная цель достигается тем .Ч.ТО суммир.ующее устройство, содержаiue;e ассоциативный запоминающий -блок гге-рвую группу элементов задержки первую группу элементов И, первый рс13ряд ыи ВЫ.КОД ассоциативного запомннгно.щего блока является выходом суммы устройства, остальные разрядны выходы а социативного запоминающего блока через соответствующие, элементы задержки первой группы соединены с пер.вьми входами соответствующих элементов И первой группы, вторые входы которых подключены к первой шине синхронизации устройства, а выходы - к соответствующим входам опро са первой группы ассоциативного запоминающего блока, содержит также постоянный запоминающий блок, вторую 1руппу элементов задержки,вторую и третью группы элементов И и элемент И, причем адресные входы постоянног за.поминающего блока соединены с выхо дами соответствующих элементов И второй группы, первые входы которых соответственно соединены с входами слагаемых устройства, а вторые входы с второй шиной синхронизации устройства, первый разрядный выход постоянного запоминающего блока соединен с первым входом элемента И, второй вход которого подключен к первой шине синхронизации устройства, а выход соединен с входом опроса второй группы ассоциативного запоминающего блока, остальные разрядные выходы постоянного запоминающего блока через соответствующие элементы задержки второй группы соединены с первыми входами элементов И третьей группы, вторые входы которьях подключены к первой шине синхронизации устройства, а выходы соединены с соответствующими входами опроса третьей группы ассоциативного запоминающего блока. На фиг. 1 представлена структурная схема суммирующего устройства; на фиг. 2 - прошивка блоков 1 и 2 для случая суммирования пяти слагаемых. Устройство содержит постоянный запоминающий блок 1, ассоциативный запоминающий блок 2, группу элементов И 3, элемент И 4, группы элементов И 5 и 6, группы элементов 7 и 8 задержки. На фиг. 1 1акже указаны информационные входы 9 устройства, выход 10 суммы, шины 11 и 12 синхронизации. Устройство работает следующим образом. На информационные входы 9 устройства одновременно подаются одноименные разряды К cлaгaeмJi x, которые в течение тактового импульса определяют адрес слова, считываемого из блока 1. Считанное из блока 1 словосамо является частью признака, подаваемого на признаковые входы 2, причем все разряды, к.роме младшего, задерживаются на один такт. Остальной часть признака являются все, кроме старшего, разряды считывае лые из блока 2 и Зс1держанные на один такт. Сформированный признак дополнительно синхронизируется на элементах И 4 - 6.путем подачи сигнала по шине 12, передний фронт котрого начинается позже, а задний раньше тактового импульса, подаваемого по шине 11. Эта мера вызвана неидеальностью элементов 7 и 8 задержки. В том же такте, в котором был подан разрядный срез слагаемых, на .выходе 10 блока 2 появляется одноименный выходной разряд. Таким образом, на выходе получается результат суммирования в последовательном, коде, причем количество тактов, за которое вычисляется сумма, равно

|J (| +

1

где С - количество затрачиваемых

тактов;

- разрядность слагаемых; К - количество слагаемых. Технико-экономический эффект предлагае1 1ого устройства заключается в том, что оно позволяет одновременносуммировать большое количество опе|зандов, что дает существенный выигрыш в быстродействии, а также позволяет сократить объем используемой памяти (при большом количестве слат гаемых К). По сравнению с известным устройством, данное устройство требует ассоциативной памяти существенно меньшей разрядности и емкости (не менее чем в Краз).

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

| Суммирующее устройство | 1990 |

|

SU1775722A1 |

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Суммирующее устройство | 1991 |

|

SU1803912A1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Ассоциативное суммирующее устройство | 1983 |

|

SU1174920A1 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| Ассоциативное суммирующее устройство | 1989 |

|

SU1665373A1 |

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

СУММИРУЮЩЕЕ УСТРОЙСТВО, содержащее ассоциативный запоминающий блок, первую группу элементов задержки и перву группу элементов И, первый разрядный выход ассоциативного запоминающего блока является выходом суммы устройства, остальные разрядные выходы ассоциативного запоминающего блока через соответствующие элементы задержки первой группы соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых подключены к первой шине синхронизации устройства, а выходы - к соответствующим входам опроса первой группы ассоциативного . запоминающего блока, о т л и ч а. ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, суммирующее устройство содержит постоянный запоминающий блок, вторую группу элементов задержки, вторую и третью группы элементов И и элемент И, причем адресные входы постоянного запоминающего блока соединены с выходами соответствующих элементов И второй группы, первые входы которых соответственно соединены с входами слагаемых устройства,а вторые входы - с второй шиной синхронизации , устройства, первый разрядный вьоход IS постоянного запоминающего блока соединен с первым входом элемента И, второй вход которого подключен к первой шине синхронизации устройства., а выход соединен с входом опроса второй группы ассоциативного запоминающего блока, остальные разрядные выходы постоянного запоминающего блока через соответствующие элементы задержки второй группы (Соединены с первыми входами элелен- . Ю 05 тов И третьей группы, вторые входы которых подключены к первой шине синхронизации устройства, а выходы соединены с соответствующими входаCD ми опроса третьей группы ассоциативного запоминающего блока.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Справочник по цифровой вычисг лительной технике, (электронные вычислительные машины и системы) | |||

| Под ред | |||

| Б.Н | |||

| Малиновского | |||

| Киев, Техника, 1980, с | |||

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Кохонен Т | |||

| Ассоциативная память | |||

| М | |||

| , Мир , 1.980, с | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| рис | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-12-23—Публикация

1982-10-20—Подача