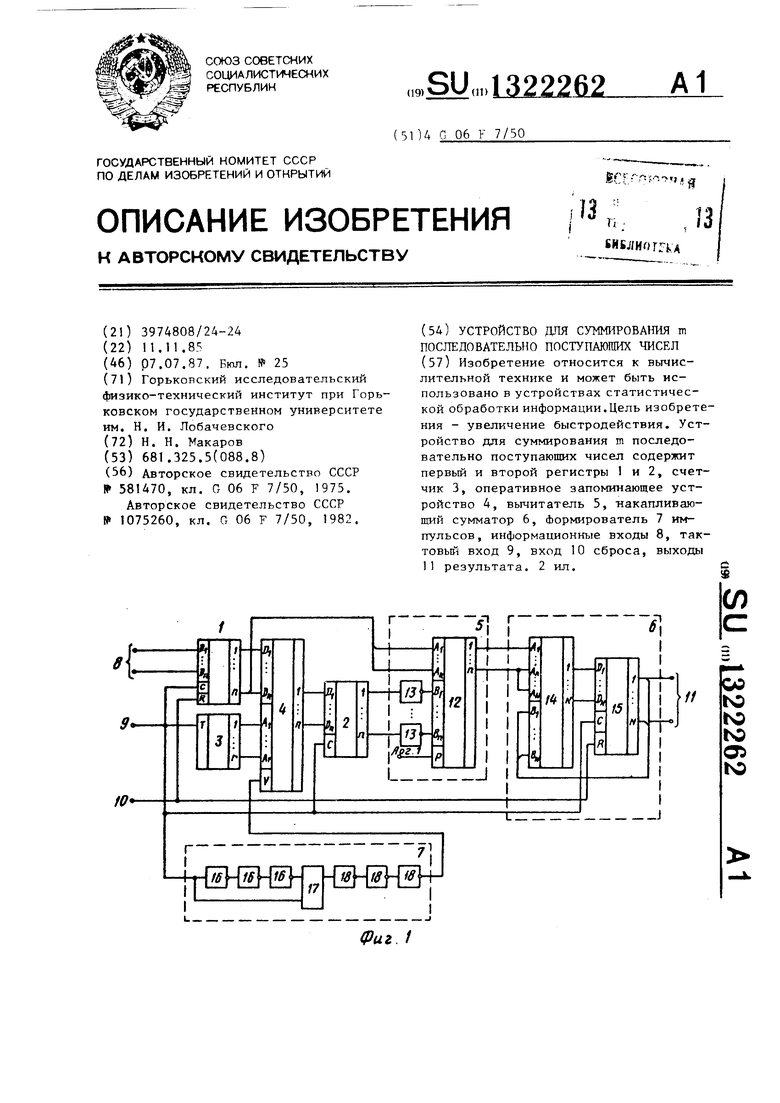

Изобретение относится к иычисли- тельной технике и может быть использовано в устройствах статистической обработки информации.

Цель изобретения - увеличение бы- стродействия.

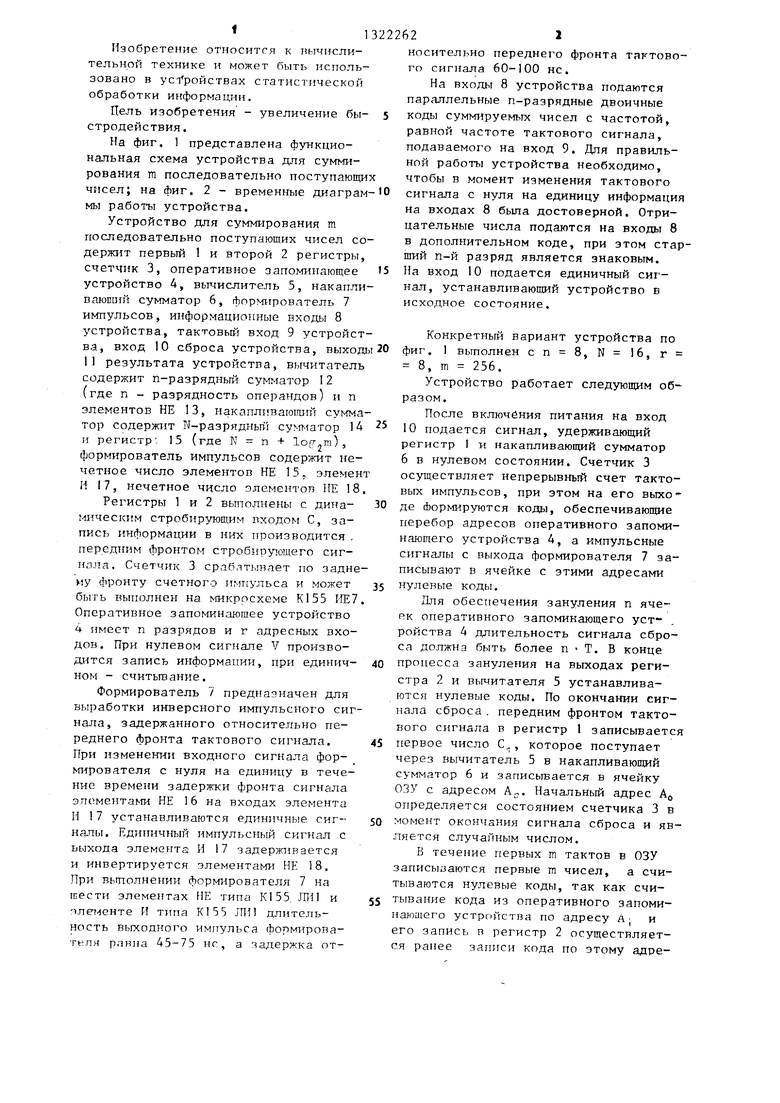

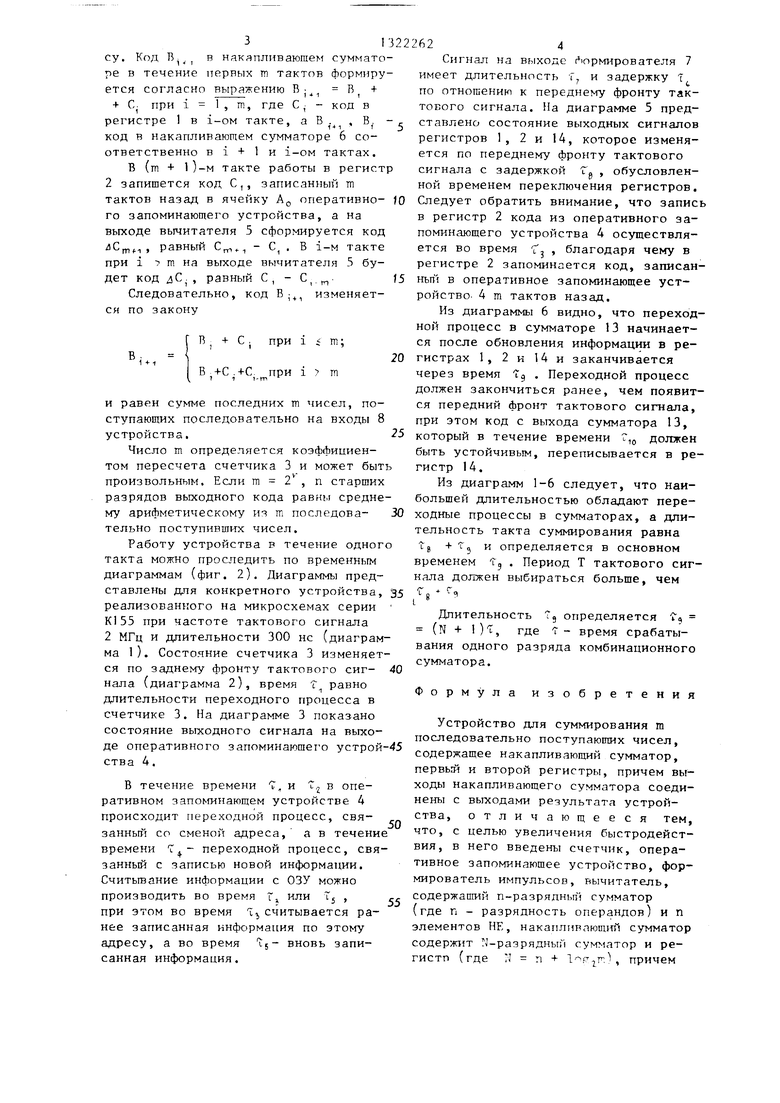

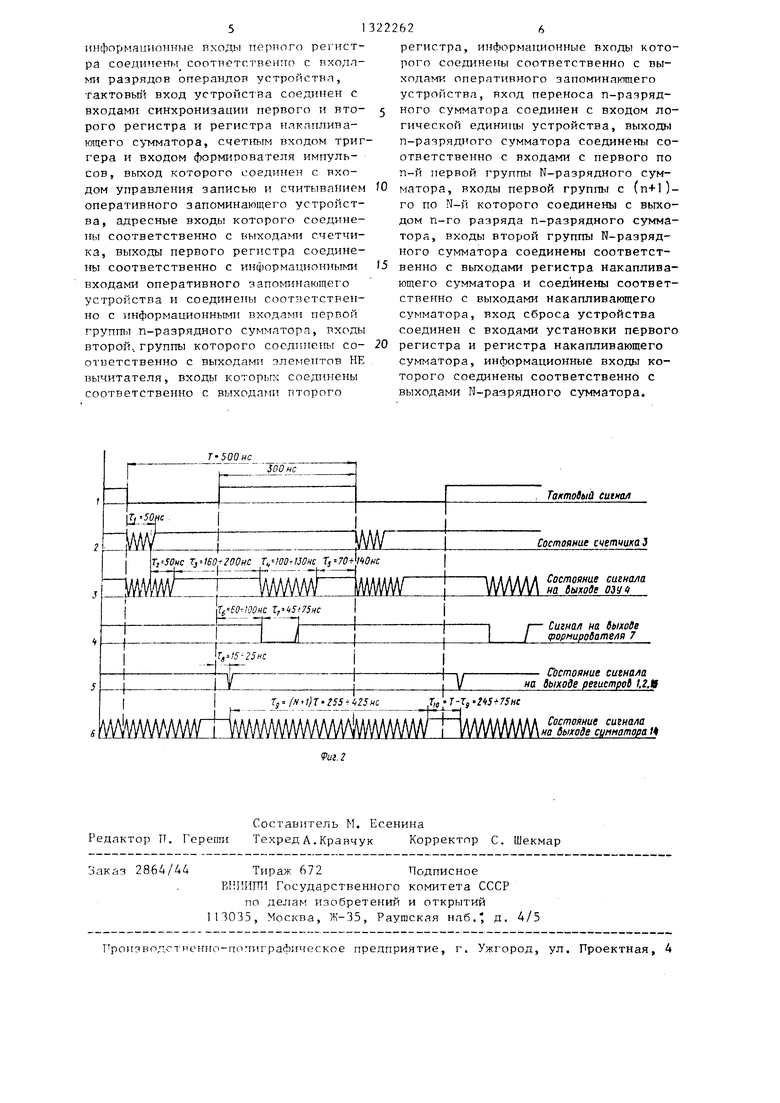

На фиг, 1 представлена функциональная схема устройства для суммирования m последовательно поступающи чисел; на фиг, 2 - временные диаграм мы работы устройства.

Устройство для суммирования m последовательно поступающих чисел содержит первый 1 и второй 2 регистры, счетчик 3, оперативное запоминающее устройство А, вычислитель 5, накапливающий сумматор 6, формирователь 7 импульсов, информационные входы 8 устройства, тактовый вход 9 устройства, вход 10 сброса устройства, выход 11 результата устройства, вычитатель содержит п-разрядный сумматор I2 (где п - разрядность операндов) и п элементов НЕ 13, накапливающий сумматор содержит N-разрядньш 14 и регистр: 15 (где К п + log.m), формирователь импульсов содержит нечетное число элементов НЕ 15, элемен И 17, нечетное число элементов НЕ 18

Регистры 1 и 2 вьтолнены с динамическим cтpoбиpyюtt им входом С, запись информации в них производится . передним фронтом стробирующего сиг- пала. Счетчик 3 срабатывает по заднему фронту счетного iiMnyjTbca и мозкет быть выполнен на микросхеме К155 ИЕ7 Оперативное запоминающее устройство 4 имеет п разрядов и г адресных входов. При нулевом сигнале V производится запись информации, при единич- ном - считьгаание.

Формирователь 7 предназначен для выработки инверсного импульсного сигнала, задержанного относительно переднего фронта тактового сигнала, При изменении входного сигнала формирователя с нуля на единицу в течение времени задертргки фронта сигнала элементами НЕ 16 на входах элемента Н 1 7 устанавливаются единичные сиг- напы. Единичный импульсный сигнал с ьыхода элемента И 17 задерживается и инвертируется элементами НЕ 18, При вьшолнении формирователя 7 на гпести элементах F1E типа К155. ЯИ1 и элементе И типа ЛН1 длительность выхоцного импульса формирователя равна 45-75 не, а задержка от

носительно переднего фронта тактового сигнала 60-100 не,

На входы 8 устройства подаются параллельные п-разрядные двоичные коды суммируемых чисел с частотой, равной частоте тактового сигнала, подаваемого на вход 9, Для правильной работы устройства необходимо, чтобы в момент изменения тактового сигнала с нуля на единицу информация на входах 8 была достоверной. Отрицательные числа подаются на входы 8 в дополнительном коде, при этом старший п-й разряд является знаковым. На вход 10 подается единичный сигнал, устанавливающий устройство в исходное состояние.

Конкретный вариант устройства по фиг, 1 вьтолнен , N 16, г 8, m 256,

Устройство работает следующим образом.

После включения питания на вход 10 подается сигнал, удерживающий регистр I и накапливающий сумматор 6 в нулевом состоянии, Счетч:ик 3 осуществляет непрерывный счет тактовых импульсов, при этом на его выходе Формируются коды, обеспечивающие перебор адресов оперативного запоминающего устройства 4, а импульсные сигналы с выхода формирователя 7 записывают в ячейке с этими адресами нулевые коды,

Лля обеспечения зануления п ячеек оперативного запоминающего устройства 4 длительность сигнала сброса должна быть более п Т, В конце процесса зануления на выходах регистра 2 и вычитателя 5 устанавливаются нулевые коды. По окончании сиг- пала сброса . передним фронтом тактового сигнала в регистр 1 записывается первое число С,, которое поступает через вычитатель 5 в накапливающий сумматор 6 и записывается в ячейку ОЗУ с адресом А, Начальный адрес Ад определяется состоянием счетчика 3 в момент окончания сигнала сброса и является случайным числом,

В течение первых m тактов в ОЗУ записываются первые m чисел, а считываются нулевые коды, так как считывание кода из оперативного запоминающего устройства по адресу А; и его запись в регистр 2 осуществляется ранее записи кода по этому адре31322

су. Код В, в накапливающем сумматоре в течение первых m тактов формируется согласно выражению Bj В +

+ С. при 1 1, т, где С - код в регистре 1 в i-ом такте, а В . В,, -г код в накапливающем сумматоре 6 соответственно в i + 1 и i-oM тактах.

В (т + 1)-м такте работы в регистр 2 запишется код С,, записанный m тактов назад в ячейку А оперативно- fO го запоминающего устройства, а на выходе вычитателя 5 сформируется код йС, равный С - С . В i-M такте при i 7 m на выходе вычитателя 5 будет код С , равный С, - С,. ff

Следовательно, код В., изменяется по закону

В, + С j при i i т; В +С .+С. при i m

т 1 1-ГТ1

и равен последних m чисел, поступающих последовательно на входы 8 устройства,

Число m определяется коэффициентом пересчета счетчика 3 и может быть произвольным. Если m 2 , п старщих разрядов выходного кода paBni.i среднему арифметическому из m последова- 30 тельно поступивших чисел.

Работу устройства в течение одного такта можно проследить по временным диаграммам (фиг. 2). Диаграммы представлены для конкретного устройства, 35 реализованного на микросхемах серии К155 при частоте тактового сигнала 2 МГд и длительности 300 не (диаграмма 1). Состояние счетчика 3 изменяется по заднему фронту тактового сиг- 40 нала (диаграмма 2), время Т равно длительности переходного процесса в счетчике 3. На диаграмме 3 показано состояние выходного сигнала на выходе оперативного запоминающего устрой-45 ства 4.

В течение времени Т, и t в оперативном запоминающем устройстве 4 происходит переходной процесс, связанный со сменой адреса, а в течение времени 4- переходной процесс, связанный с записью новой информации. Считьгоание информации с ОЗУ можно производить во время TI или Tj , , при этом во время 1 считывается ранее записанная информация по этому адресу, а во время вновь записанная информация.

50

г

O ff

0

5

0

:б24

Сигнал на выходе (10рмирователя 7 имеет длительность f и задержку 1 по отношению к переднему фронту тактового сигнала. На диаграмме 5 представлено состояние выходных сигналов регистров 1, 2 и 14, которое изменяется по переднему фронту тактового сигнала с задержкой Т , обусловленной временем переключения регистров. Следует обратить внимание, что запись в регистр 2 кода из оперативного запоминающего устройства 4 осуществляется во время Г , благодаря чему в регистре 2 запоминается код, записан- ньш в оперативное запоминающее устройство. 4 m тактов назад.

Из диаграммы 6 видно, что переходной процесс в сумматоре 13 начинается после обновления информации в регистрах 1, 2 и 14 и заканчивается через время Тд . Переходной процесс должен закончиться ранее, чем появится передний фронт тактового сигнала, при этом код с выхода сумматора 13, который в течение времени должен быть устойчивым, переписывается в регистр 14,

Из диаграмм 1-6 следует, что наибольшей длительностью обладают переходные процессы в сумматорах, а длительность такта суммирования равна

+ г

5 И определяется в основном

временем т, . Период Т тактового сигнала должен выбираться больше, чем

Длительность Т, определяется Г (N + 1)1, где Т - время срабатывания одного разряда комбинационного сумматора.

Формула изобретения

Устройство для суммирования m последовательно поступающих чисел, содержащее накапливающий сумматор, первьй и второй регистры, причем выходы накапливающего сумматора соединены с выходами результата устройства, отличающееся тем, что, с целью увеличения быстродействия, в него введены счетчик, оперативное запоминающее устройство, формирователь импульсов, вычитатель, содержащий п-разрядньп1 сумматор (где п - разрядность операндов) и п элементов НЕ, накапливающий сумматор содержит N-разряднып сумматор и ре- гистп (где N л + ) , причем

информационные входы пертюго регистра соедиттены соответственнее с нходл- ми разрядов операндов устройства, тактовьп вход устройства соединен с входами синхронизации первого и второго регистра и регистра накапливающего сумматора, счетным входом триг гера и входом формирователя импульсов, выход которого соединен с входом управления записью и считыванием оперативного запоминающего устройства, адресные входы которого соединены соответственно с выходаьп счетчика, выходы первого регистра соединены соответственно с информационными входами оперативного запоминающего устройства и соединены соответственно с информационными входами первой групптз п-разрядного сумматора, входы второй,группы которого соединены соответственно с выходами элементов НЕ вычитателя, входы которьк соединены соответственно с выходами второго

Составитель М. Есенина Редактор П. Гереиш Техред Д. Кравчук Корректор С. Шекмар

2864/44

Тираж 672Подписное

ВНИНГП1 Государственного комитета СССР

по делам изобретений и открытий 13035, Москва, Ж-35, Раушская наб. д. А/5

Г роизводстиенно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

222626

регистра, информационные входы которого соединены соответственно с выходами оперативного запоминающего устройства, вход переноса п-разряд- 5 ного сумматора соединен с входом логической единицы устройства, выходы п-разрядного сумматора соединены соответственно с входами с первого по п-й первой группы N-разрядного сум- 0 матора, входы первой группы с (п+1)- го по N-й которого соединены с выходом п-го разряда п-разрядного сумматора, входы второй группы N-разрядного сумматора соединены соответст- 5 венно с выходами регистра накапливающего сумматора и соединены соответственно с выходами накапливающего сумматора, вход сброса устройства соединен с входами установки первого 0 регистра и регистра накапливающего сумматора, информационные входы которого соединены соответственно с выходами N-разрядного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1988 |

|

SU1647901A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ РАДИОЛОКАЦИОННОГО ИЗОБРАЖЕНИЯ МЕСТНОСТИ | 1988 |

|

SU1841035A1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Сигнализатор совпадения фаз | 1990 |

|

SU1824595A1 |

| Устройство кодирования сигнала цветных графических изображений | 1987 |

|

SU1555917A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах статистической обработки информации.Цель изобретения - увеличение быстродействия. Устройство для суммирования m последовательно поступающих чисел содержит первый и второй регистры 1 и 2, счетчик 3, оперативное запоминающее устройство 4, вычитатель 5, накапливающий сумматор 6, Формирователь 7 импульсов, информационные входы 8, тактовый вход 9, вход 10 сброса, выходы 11 результата. 2 ил. с ф f // J оо 1C к ьо а tsD I j иг. 1

| Параллельный накапливающий сумматор | 1975 |

|

SU581470A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для суммирования @ -разрядных последовательно поступающих чисел | 1982 |

|

SU1075260A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1985-11-11—Подача