4

05

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Устройство для умножения | 1985 |

|

SU1322266A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств для умножения двоичных и десятичных чисел. Цель изобретения - сокращение аппаратурных затрат. Устройство для умножения содержит регистры 1-3 сомножителей и результата, матричный умножитель 4, регистры 5-9, сумматоры 10-13 и корректирующие сумматоры 14-16. Цель достигается исключением из устройства четвертого корректирующего сумматора за счет изменения функции первого корректирующего сумматора 14. 4 ил.

JL±.

ipuai

и

3150

Изобретение относится к области вычислительной техники и может быть использовано при разработке быстро- действ то1цих устро 5ст в для умножения двоичных и десятичньк чисел.

Цель изобретения - сокращение колчества оборудования.

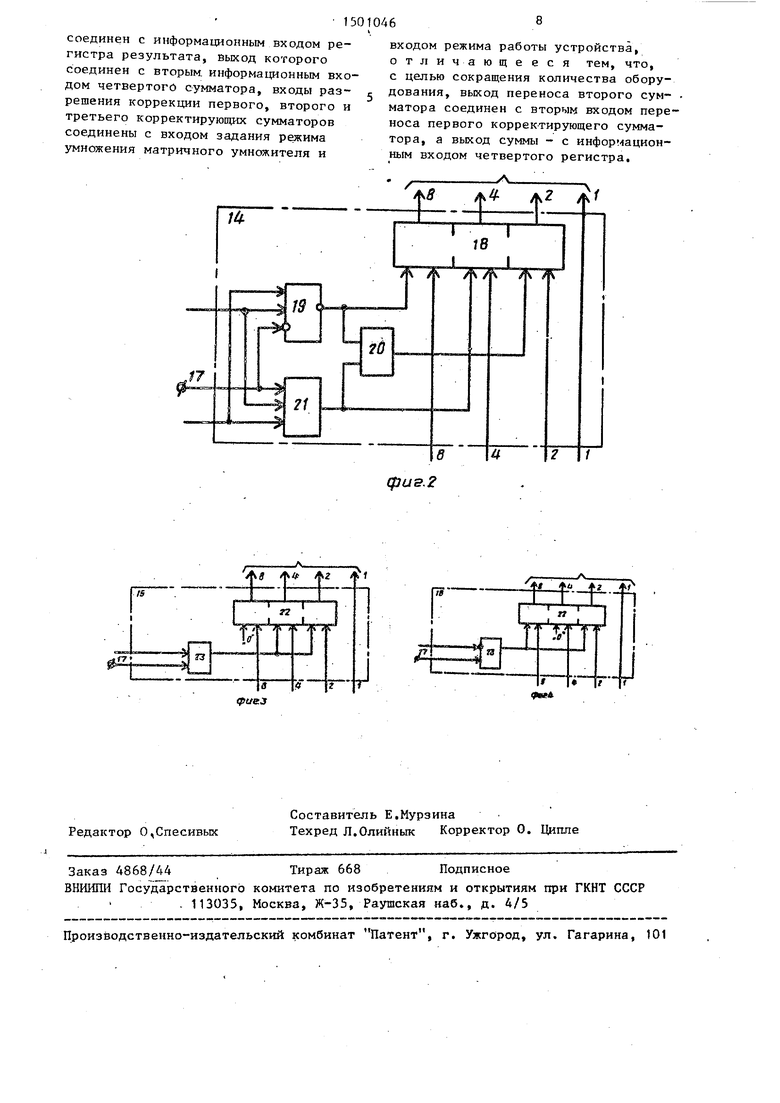

На фиг.1 приведена структурная схема устройства; на фиг. 2-4 - функ циональные схемы первого-третьего корректирующгос сумматоров соответственно.

Устройство для умножения содержит (фиг.1) регистры первого 1 и второ- го 2 сомножителей, регистр 3 результата, матричный умножитель 4, регистры 5-9, сумматоры 10-13, корректирующие сумматоры 14-16 и вход 17 режма работы устройства.

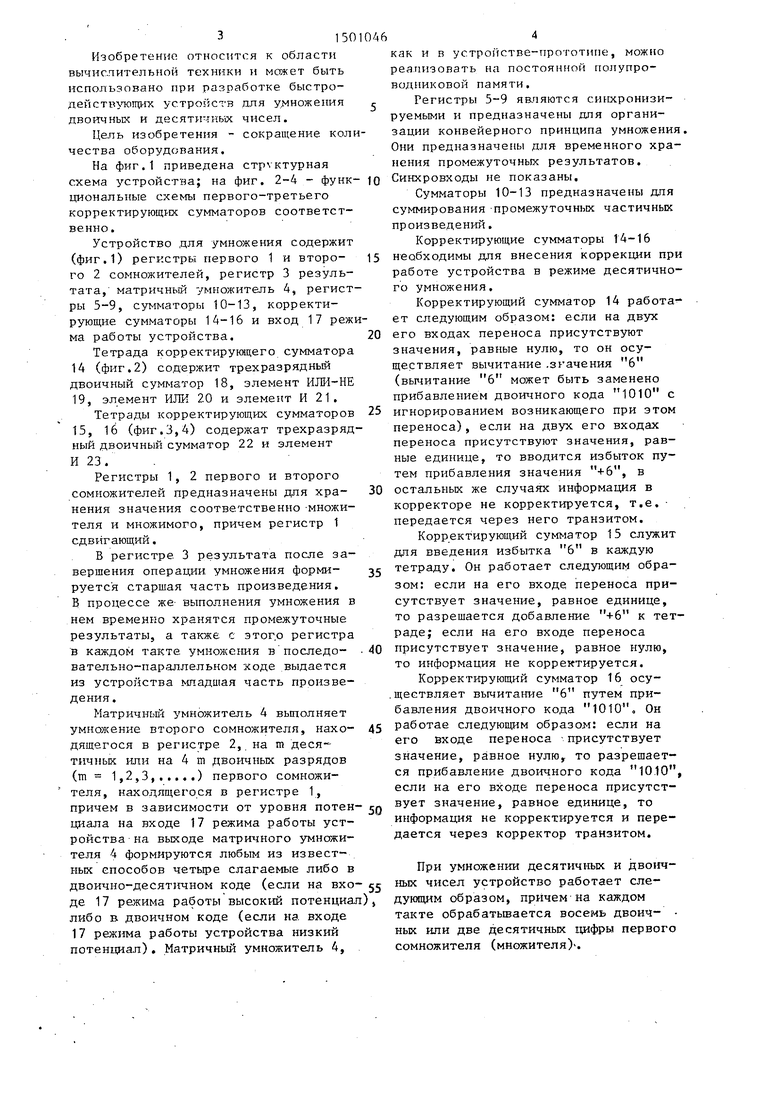

Тетрада корректирукщего сумматора 14 (фиг.2) содержит трехразрядный двоичный сумматор 18, элемент ИЛИ-НЕ 19, элемент ИЛИ 20 и элемент И 21.

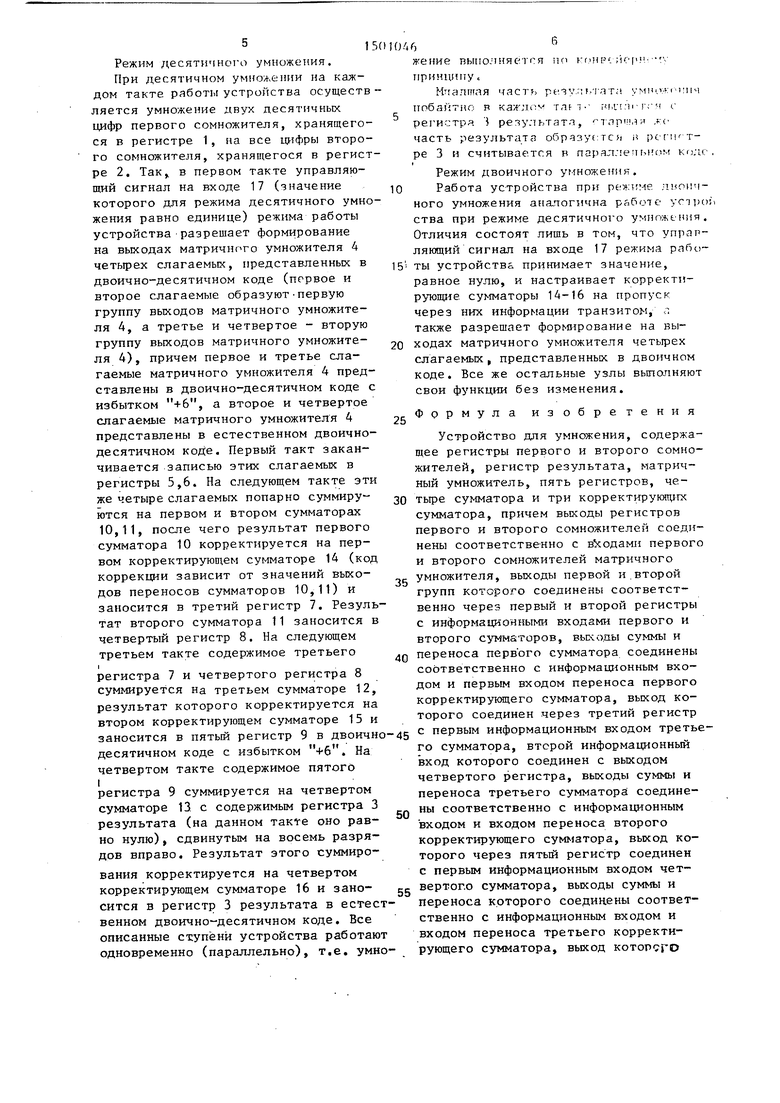

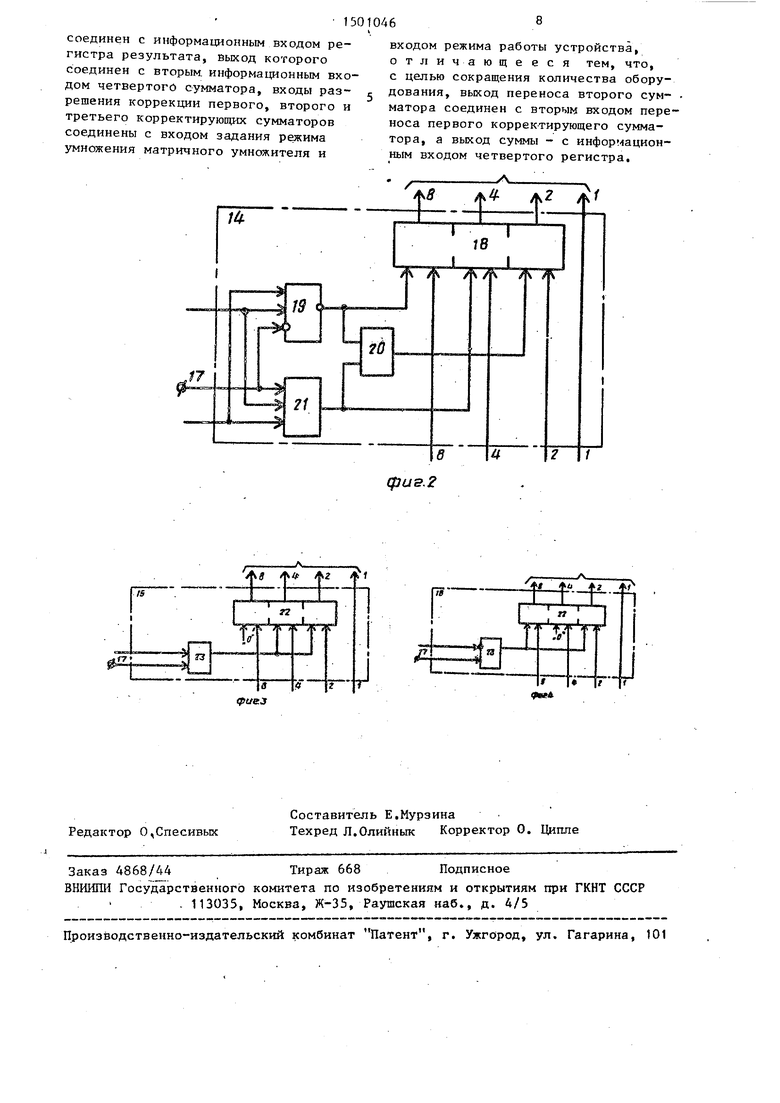

Тетрады корректирующих сумматоров 15, 16 (фиг.3,4) содержат трехразрядный двоичный сумматор 22 и элемент И 23. .

Регистры 1, 2 первого и второго сомножителей предназначены для хра- нения значения соответственно -множителя и множимого, причем регистр 1 сдвигающий.

В регистре. 3 результата после завершения операции умножения форми- руется старщая часть произведения. В процессе же- выполнения умножения в нем временно хранятся промежуточные результаты, а также с этог.о регистра в каждом такте умножения в последо- вательно-параллельном ходе выдается из устройства младшая часть произведения.

Матричньш умножитель А выполняет умножение второго сомножителя, нахо- дящегося в регистре 2, на m десятичных шт на 4 m двоичных разрядов (т 1,2,3,) первого сомножителя, находящегося в регистре 1, причем в зависимости от уровня потен- диала на входе 17 режима работы устройства на выходе матричного умножителя 4 формируются любьш из известных способов четыре слагаемые либо в двоично-десят1гчном коде (если на вхо- де 17 режима работы высокий потенциал либо в двоичном коде (если на. входе 17 режима работы устройства низкий потенциал). Матричный умножитель 4,

как и в устройстве-прототипе, можно реатп 3овать на постоянной полупроводниковой памяти.

Регистры 5-9 яапяются синхронизируемыми и предназначены для организации конвейерного принципа умножени Они предназначены для временного хранения промежуточных результатов. Синхровходы не показаны.

Сумматоры 10-13 предназначены для суммирования -промежуточных частичных произведений.

Корректрфующие сумматоры 14-16 необходимы для внесения коррекции пр работе устройства в режиме десятичного умножения.

Корректирующий сумматор 14 работает следующим образом: если на двух его входах переноса присутствуют значения, равные нулю, то он осуществляет вычитание .значения 6 (вычитание 6 может быть заменено прибавлением двоичного кода 1010 с игнорированием возникающего при этом переноса), если на двух его входах переноса присутствуют значения, равные единице, то вводится избыток путем прибавления значения +6, в остальных же случаях информация в корректоре не корректируется, т,е.- передается через него транзитом.

Корректирующий сумматор 15 служит для введения избытка 6 в каждую тетраду. Он работает следующим образом: если на его входе переноса присутствует значение, равное единице, то разрешается добавление +6 к тетраде; если на его входе переноса присутствует значение, равное нулю, то информация не корректируется.

Корректирующий сумматор 16 осуществляет вычитание 6 путем прибавления двоичного кода 1010, Он работае следующим образом: если на его входе переноса присутствует значение, равное нулю, то разрешается прибавление двоичного кода 10.10 если на его входе переноса присутствует значение, равное единице, то информация не корректируется и передается через корректор транзитом.

При умножении десятичных и двоичных чисел устройство работает сле- дукйцим образом, причем на каждом такте обрабатывается восемь двоич- ных или две десятичных гщфры первого сомножителя (множителя)-.

51

Режим десятичнсч о умножения. При десятичном умножении на каждом такте работы устройства осуществ ляется умножение двух десятичных цифр первого сомножителя, хранящегося в регистре 1, на все цифры второго сомножителя, хранящегося в регистре 2, Так,, в первом такте управляющий сигнал на входе 17 (значение которого для режима десятичного умножения равно единице) режима работы устройства разрешает формирование на выходах матричнг го умножителя А четырех слагаемых, представленных в двоично-десятичном коде (первое и второе слагаемые образуют-первую группу выходов матричного умножителя 4, а третье и четвертое - вторую группу выходов матричного умножителя 4), причем первое и третье слагаемые матричного умножителя 4 представлены в двоично-десятичном коде с избытком +6, а второе и четвертое слагаемые матричного умножителя 4 представлены в естественном двоично- десятичном коде. Первый такт заканчивается записью этих слагаемых в регистры 5,6. На следующем такте эти же четыре слагаемых попарно суммируются на первом и втором сумматорах 10,11, после чего результат первого сумматора 10 корректируется на первом корректирующем сумматоре 14 (код коррекции зависит от значений выходов переносов сумматоров 10,11) и заносится в третий регистр 7. Результат второго сумматора 11 заносится в четвертый регистр 8. На следующем третьем такте содержимое третьего

регистра 7 и четвертого регистра 8 суммируется на третьем сумматоре 12, результат которого корректируется на втором корректирующем сумматоре 15 и заносится в пятый регистр 9 в двоичн десятичном коде с избытком +б. На

четвертом такте содержимое пятого

I

регистра 9 суммируется на четвертом

сумматоре 13. с содержимым регистра 3 результата (на данном тактге оно равно нулю)f сдвинутым на восемь разрядов вправо. Результат этого суммирования корректируется на четвертом корректирующем сумматоре 16 и заносится в регистр 3 результата в естесвенном двоично десятичном коде. Все описанные ступени устройства работаю одновременно (параллельно), т.е. умн10/4 f)

жение выполияе-упя пс :гя1р -;ic i - принципу,

часть ре лу.:;г- 1 ата умнож тч

побайтно в каж;1( T.IFI-- гч, ;;;)-ITH с 5

регистра i результат., inpi,in же часть результата обр-чзусто и рст И т- ре 3 и считывается и парал: е тгяп1М кодс

Режим двоичного уг-тножения.

10Работа устройства при режит-ie лиопчного умножения аналогична рйботе ynijo ства при режиме десятичного умножения Отличия состоят лишь в том, что упрар- ляющий сигнал на входе 17 режима раби15 | ты устройства принимает значение, равное нулю, и настраивает корректи- рующце сумматоры 14-16 на пропуск через них информации транзитом, л также разрешает формутрование на вы20 ходах матричного умножителя четырех слагаемых, представленных в двоичном коде. Все же остальные узлы вьшолняют свои функции без изменения.

25

Формула изобретения

Устройство для умножения, содержащее регистры первого и второго сомножителей, регистр результата, матричный умножитель, пять регистров, четыре сумматора и три корректирующих сумматора, причем выходы регистров первого и второго сомножителей соединены соответстве-нно с вводами первого и второго сомножителей матричного

умножителя, выходы первой и.второй групп которого соединены соответственно через первый и второй регистры с информационными входами первого и второго сумматоров, вьсчоды суммы и

переноса первого сумматора соединены соответственно с информационным входом и первым входом переноса первого корректирукщего сумматора, выход которого соединен через третий регистр

с первым информационным входом третьего сумматора, второй информационный вход которого соединен с выходом четвертого регистра, выходы суммы и переноса третьего сумматора соединены соответственно с информационным входом и входом переноса второго корректирующего сумматора, выход которого через пятый регистр соединен с первым информационным входом четвертог.о сумматора, выходы суммы и переноса которого соединены соответственно с информационньш входом и входом переноса третьего корректирующего сумматора, выход которого

соединен с информационным входом регистра результата, выход которого соединен с вторым, информационным входом четвертого сумматора, входы разрешения коррекции первого, второго и третьего корректирующих сумматоров соединены с входом задания режима умножения матричного умножителя и

1JiUR3

входом режима работы устройства, отличающе еся тем, что, с целью сокращения количества обору- дования, выход переноса второго сумматора соединен с вторым входом переноса первого корректирующего сумматора, а выход суммы - с информацион- HbiM входом четвертого регистра.

фиг. 2

1 J

ifefA

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1985 |

|

SU1322266A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1988-01-06—Подача