Изобретение относится к вычислительной технике и может быть использовано в устройствах и системах отображения графической информации на электронно-лучевых трубках.

Цель изобретения - повышение быстродействия устройства.

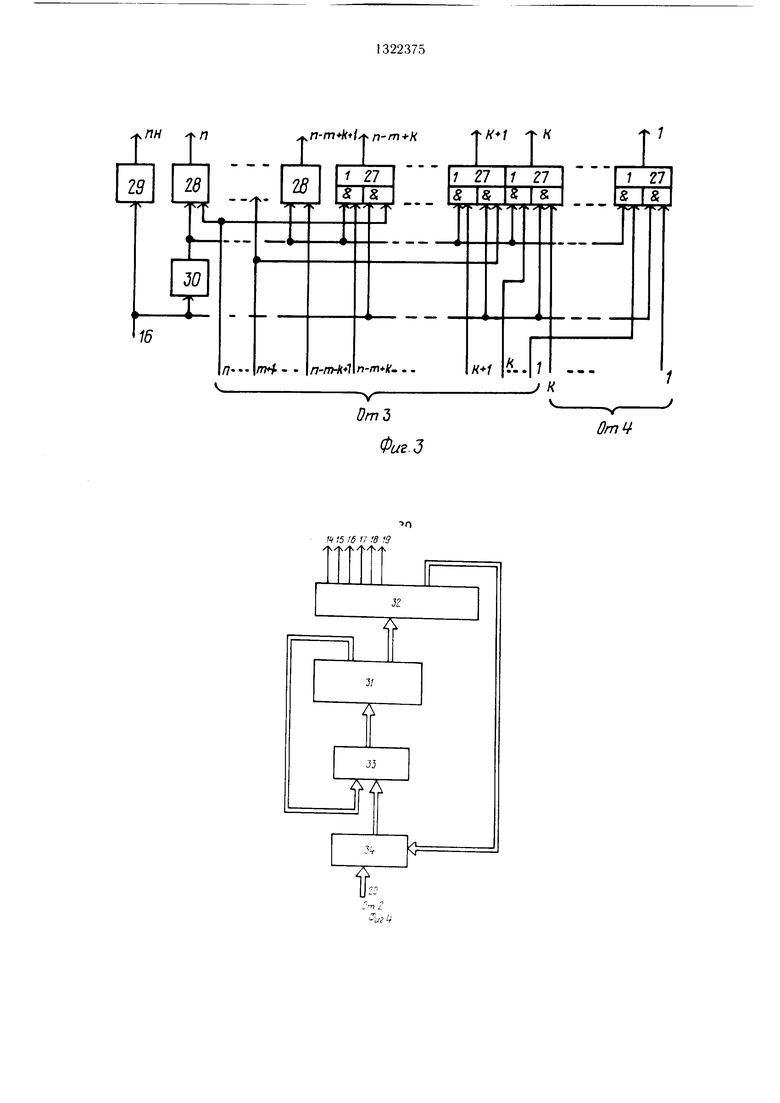

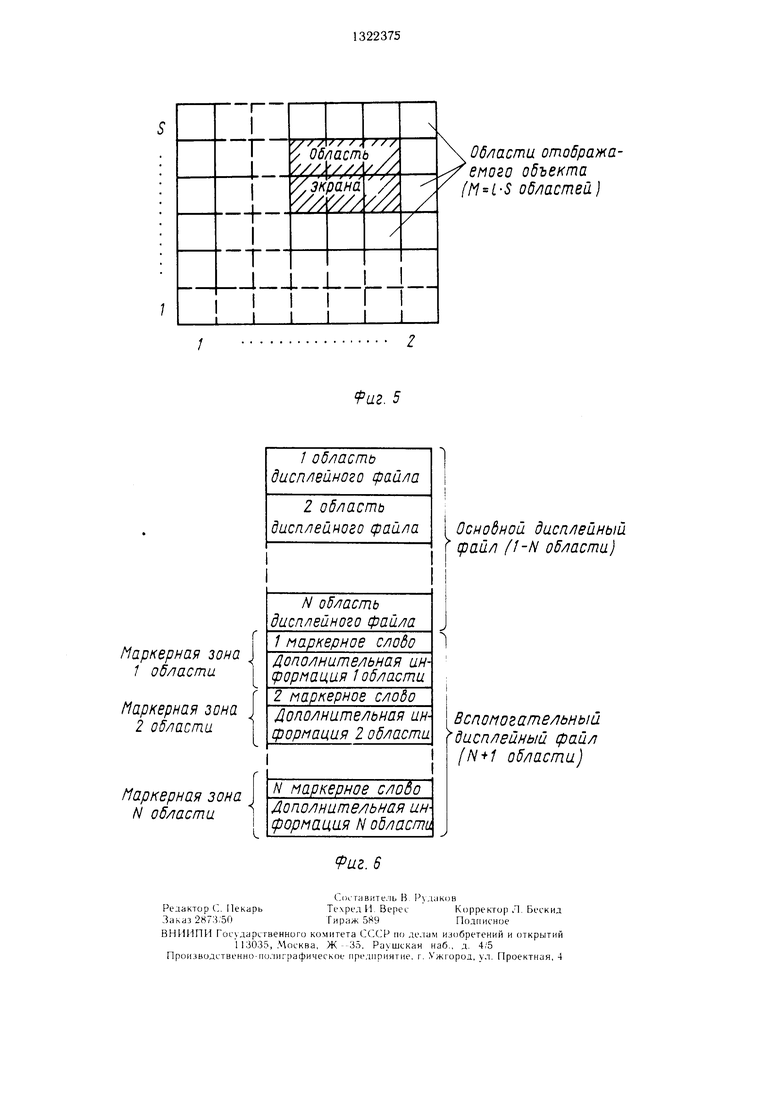

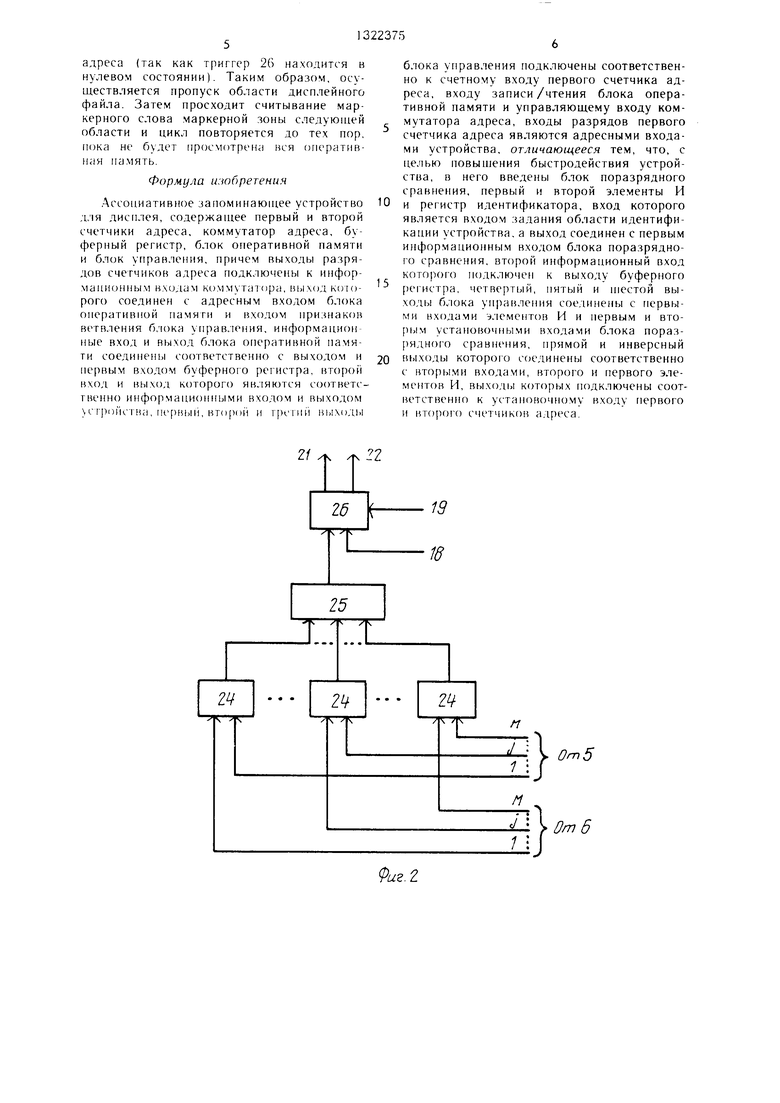

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока поразрядного сравнения; на фиг. 3 - структурная схема подключения входов коммутатора адреса к первому и второму счетчикам адреса; на фиг. 4 - структурная схема блока управления; на фиг. 5 и 6 - соответственно условное разбиение отображаемого объекта на области обьекта и оперативной памяти на области дисплейного файла.

Устройство (фиг. 1) содержит блок I оперативной памяти, коммутатор 2 адреса, первый счетчик 3 адреса, второй счетчик 4 адреса,буферный регистр 5, регистр 6 идентификатора, блок 7 поразрядного сравнения, первый элемент И 8, второй элемент И 9, блок 10 управления.

Устройство имеет вход 1 1 задания области идентификации, информационный вход 12 и информационный выход 13.

Блок 10 имеет выходы 14-19 и вход 20, блок 7выходы 21 и 22. Устройство

имеет вход 23.

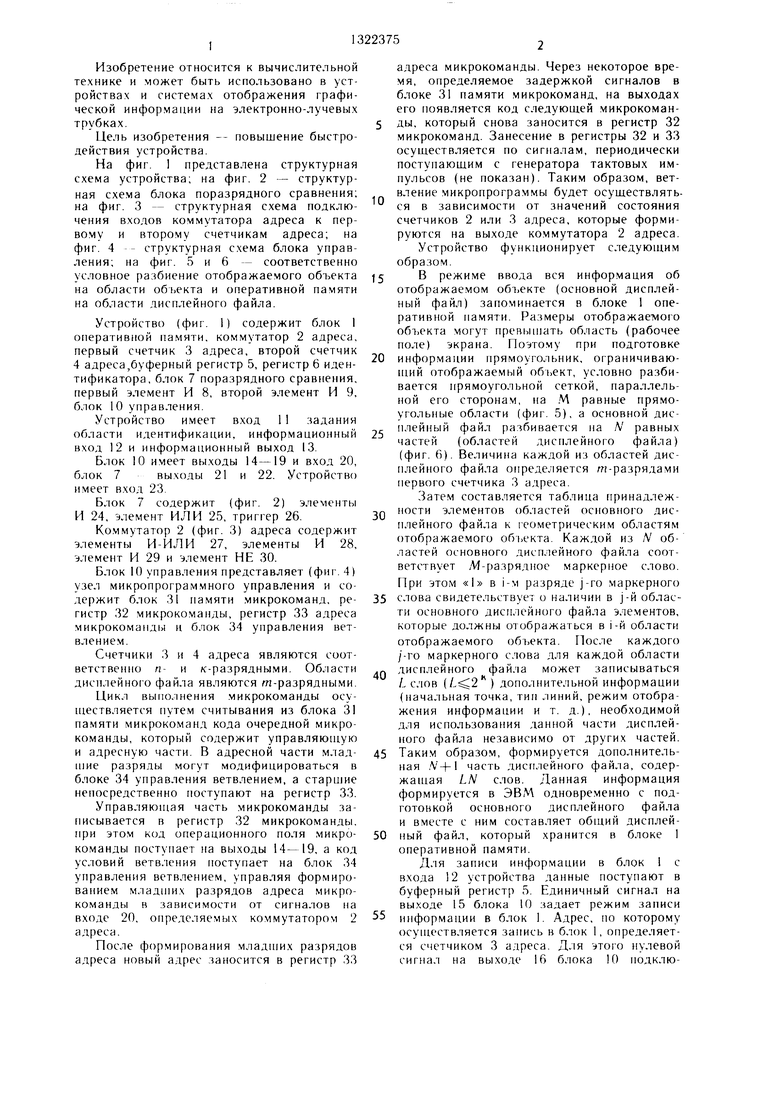

Блок 7 содержит (фиг. 2) элементы И 24, элемент ИЛИ 25, триггер 26.

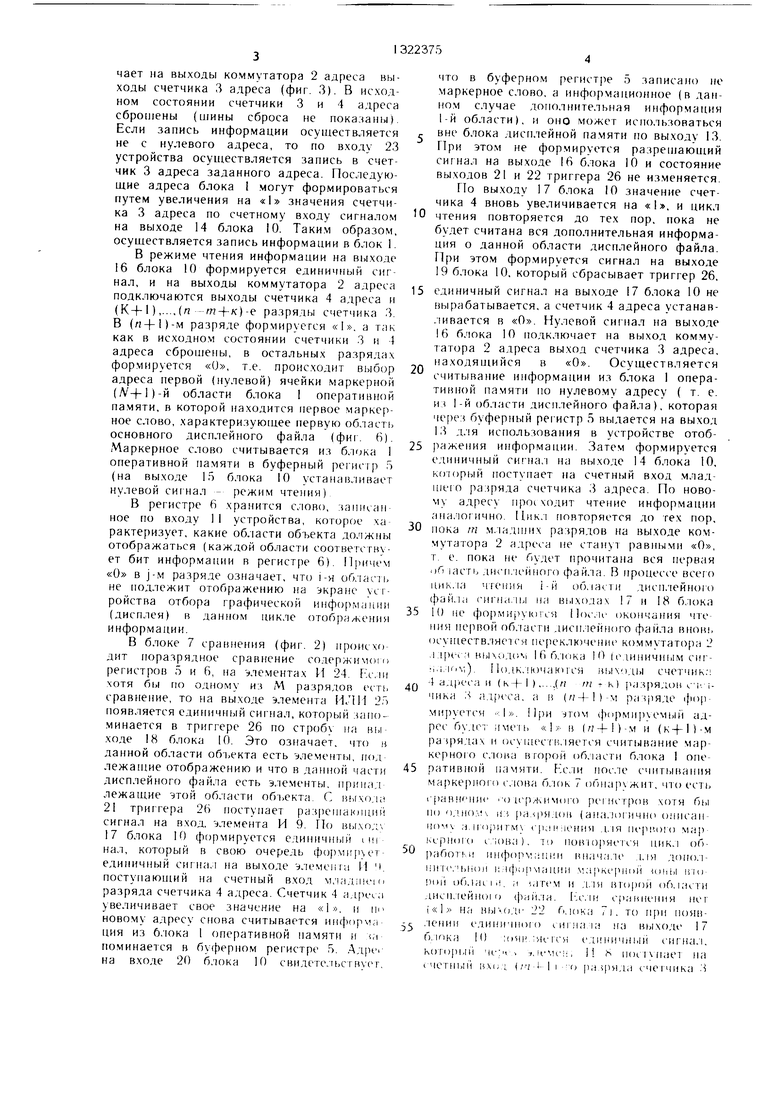

Коммутатор 2 (фиг. 3) адреса содержит элементы И-ИЛИ 27, элементы И 28, элемент И 29 и элемент НЕ 30.

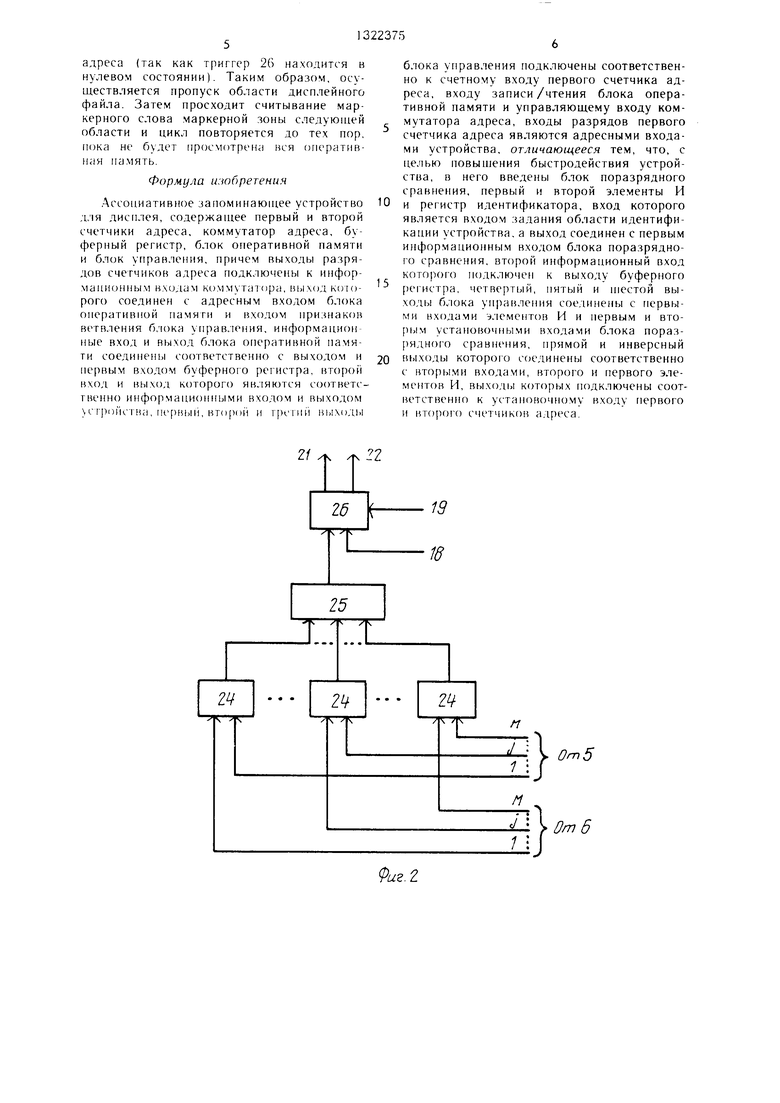

Блок И) управления представляет (фиг. 4) узел микропрограммного управления и содержит блок 31 памяти микрокоманд, регистр 32 микрокоманды, регистр 33 адреса микрокоманды и блок 34 управления ветвлением.

Счетчики 3 и 4 адреса являются соответственно и к-разрядными. Области дисплейного файла являются т-разрядными.

Цикл выполнения .микрокоманды осуществляется путем считывания из блока 31 памяти микрокоманд кода очередной микрокоманды, который содержит управляющую и адресную части. В адресной части млад- разряды могут модифицироваться в блоке 34 управления ветвлением, а старшие непосредственно поступают на регистр 33.

Управляющая часть микрокоманды записывается в регистр 32 микрокоманды, при это.м код операционного поля микрокоманды поступает на выходы 14-19, а код условий ветвления поступает на блок 34 управления ветвлением, управляя формированием млад1пих разрядов адреса микрокоманды в зависимости от сигналов на входе 20, определяемых коммутатором 2 адреса.

После формирования младших разрядов адреса новый адрес заносится в регистр 33

адреса микрокоманды. Через некоторое время, определяемое задержкой сигналов в блоке 31 памяти микрокоманд, на выходах его появляется код следующей микрокоман- ды, который снова заносится в регистр 32 микрокоманд. Занесение в регистры 32 и 33 осуществляется по сигналам, периодически поступающим с генератора тактовых импульсов (не показан). Таким образом, ветвление микропрограммы будет осуществлять- ся в зависимости от значений состояния счетчиков 2 или 3 адреса, которые формируются на выходе коммутатора 2 адреса. Устройство функционирует следующим образом.

5В режиме ввода вся информация об

отображаемом объекте (основной дисплейный файл) запоминается в блоке 1 оперативной памяти. Размеры отображаемого o6iieKTa могут превышать область (рабочее поле) экрана. Поэтому при подготовке

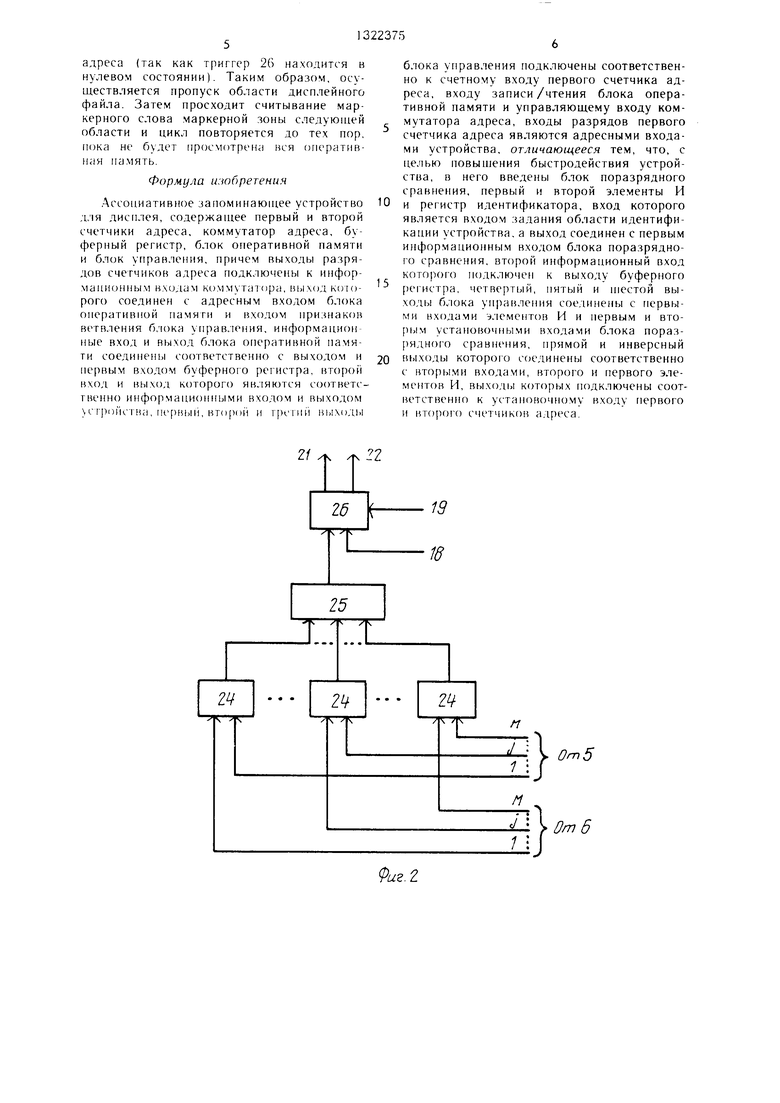

0 информации прямоугольник, ограничивающий отображаемый обьект, условно разбивается прямоугольной сеткой, параллельной его сторонам, на М равные прямоугольные области (фиг. 5), а основной дис плейный файл разбивается на Л равных частей (областей дисплейного файла) (фиг. 6). Величина каждой из областей дисплейного файла определяется Агг-разрядами первого счетчика 3 адреса.

Затем составляется таблица принадлежQ ности элементов областей OCHOBHOI O дисплейного файла к геометрическим областям отображаемого обьекта. Каждой из /V областей основного дисплейного файла соответствует М-разрядное маркерное слово. При этом «I в i-M разряде j-ro маркерного

5 слова свидетельствует о наличии в j-й области основного дисплейного файла элементов, которые должны отображаться в i-й области отображаемого объекта. После каждого /-ГО маркерного слова для каждой области дисплейного файла может записываться L слов (/.2 ) дополнительной информации (начальная точка, тип линий, режим отображения информации и т. д.), необходимой для использования данной части дисплейного файла независимо от других частей.

5 Таким образом, формируется дополнительная . -|-1 часть дисплейного файла, содержащая LN слов. Данная информация формируется в ЭВМ одновременно с подготовкой основного дисплейного файла и вместе с ним составляет общий дисплей0 ный файл, который хранится в блоке 1 оперативной памяти.

Для записи информации в блок I с входа 12 устройства данные поступают в буферный регистр 5. Единичный сигнал на выходе 15 блока 10 задает режим записи

5 информации в блок 1. Адрес, по которому осуществляется запись в блок 1, определяется счетчиком 3 адреса. Для этого нулевой сигнал на выходе 16 блока 10 нодклю0

чает на выходы коммутатора 2 адреса выходы счетчика 3 адреса (фиг. 3). В исходном состоянии счетчики 3 и 4 адреса сброшены (шины сброса не показаны). Если запись информации осуществляется не с нулевого адреса, то по в.ходу 23 устройства осун1.ествляется запись в счетчик 3 адреса заданного адреса. Последующие адреса блока 1 могут формироваться путем увеличения на «1 значения счетчика 3 адреса по счетному входу сигналом на выходе 14 блока 10. Таки.м образом, осуществляется запись информации в блок 1. В режиме чтения информации на выходе

16блока 10 фор.мируется единичный сигнал, и на выходы ко.ммутатора 2 адреса подключаются выходы счетчика 4 адреса и (К+1)(п )-е разряды счетчика 3.

В (n-(-l)-M разряде формируется «I. а т;ж как в исходно.м состоянии счетчики .3 и 4 адреса сброшены, в остальных разрядах фор.мируется «О, т.е. происходит выбор адреса первой (нулевой) ячейки маркерной (Л -(-1)-й области блока I оператинной памяти, в которой находится первое маркерное слово, характеризующее первую област1 основного дисплейного файла (фиг. 6). Маркерное слово считывается из блока 1 оперативной памяти в буферный регистр 5 (на выходе 15 блока 10 устанав.тивает нулевой сигнал - режим чте}{ия)

В регистре 6 хранится с. юво, записан ное но входу 1 1 устройства, которое ха рактеризует, какие области объекта должны отображаться (каждой области соответствует бит информации в регистре 6). Причем «О в J-M разряде означает, что i-я облаем. не подлежит отображению на акранс устройства отбора графической информации (дисплея) в данном цикле отображения информации.

В блоке 7 сра)нения (фиг. 2) нроисхг)- дит поразрядное сравнение содержимо i регистров 5 и 6, на элементах 1-1 24. F-ЛМИ хотя бы по одному из Л1 разрядов есть сравнение, то на выходе элемента НЛП 2Г) появляется единичный сигнал, который запо- .минается в триггере 26 по стробу па BI,I ходе 18 блока 10. Это означает, что н данной области обт.екта есть элементы, под лежащие отображению и что в данной части дисплейного файла есть элементы, припал лежащие этой об-ласти об 1,екта. С иыхо.и 21 триггера 26 поступает pa3peniai)uinn сигнал на вход, элемента П 9. По вы.ол

17блока 10 формируется единичный ни

нал, который в свою очередь ф()) единичный сигнал на выходе элемоига 11 м поступающий на счетный вход м, d разряда счетчика 4 адреса. Счетчик 4 адреса увеличивает свое значение на «1, и iii новому адресу снова считывается информл ция из блока I оперативной памяти и i;i поминается в буферном регистре 5. Ад|)е. на входе 20 блока К) свидетс.гьсгвхч г.

25

г -

20

0

0 5

0

5

что в буферном perHCTjie э записано )ie маркерное слово, а информационное (в данном случае дог1о,1Ш(те,тьная информация 1-й области), и оно может испо,тьзоваться вне блока дисплейной на.мяти но выходу 13. При этом не формируется разрен1ающий сигнал на выходе 16 блока 10 и состояние выходов 21 и 22 триггера 26 не изменяется. По выходу 17 блока 10 значение счетчика 4 вновь увеличивается на «1, и цикл чтения повторяется до тех пор, нока не будет считана вся дополнительная информация о данной области дисплейного файла. При этом формируется сигнал на выходе 19 блока 10, который сбрасывает триггер 26,

единичный сигнал на выходе 17 блока 10 не вырабатывается, а счетчик 4 адреса устанав- .чивается в «О. Нулевой сигнал на выходе 16 блока 10 подключает на выход коммутатора 2 адреса выход счетчика 3 адреса, находяп1ийся в «О. Осуществляется считывание информации из блока 1 оперативной памяти но нулево.му адресу ( т. е. из 1-й области дисплейного файла), которая че)ез буферный регистр 5 выдается на выход 13 д,ля использования в устройстве отображения информации. Затем формируется единичный CHnia. i на выходе 14 блока 10, который поступает на счетн1 1Й вход .млад- iiieio разряда счетчика 3 адреса. По новому адресу npot ходит чтение информации ана.логично. Пик.л повторяется до тех пор, пока m м.ладщнх разрядов на выходе коммутатора 2 адреса не равными «О, т. е. пока не будет прочитана вся первая об lacTb дисплейного файла. В процес се всего UHK.ia ч гения Ьй области дисп,лейного (})ай. сигпа.ль на в1,1Х()дах 17 н 18 б.лока 10 не фо()ми уюгся Послг оконча1Гия чте пня первой области дисн.лейного файла BHOBI, ()сун1ествляе1ся пс 1еклк)ченис коммутато()а 2 лл)е1.:1 и1)1чодсА| l66. 10 (слнничньгм сиг - 1.;,). П().1к,)чакмч я ныхмдь счетчик:;

4 ад|1еса и ( к-f-i ){ п к) разрядов c l . iчика ,Ч a.afjt ca, а rs («4-1 )-м рачряде ми1)уется . 1))И этом ({х рмирхемый адрес бу.ют .iiMC ih i (:;+1)-м и (к-|-1)-м разрядах и осущес гв,1яется считывание маркерного с.юиа второй области б,1ока 1 оперативной памяти. Ксли после считьпи)ния ма жер11ото г,лова блок 7 об}|ар жит, чюесть 1)авн ни( I D icp. j-.HMoi o ptMni ipoB хотя бы nu );iHf).M li: , ра.(| Я.ло|) (анало1 ичн(1 омпсанHONU ,Ч,1ГО|)ИГМ р; Н:10НИЯ Д. IЯ IH ll()Г() МарK cpH(iT(j сюва ), Т) пов1()рн1 14 я цик.л обработки ||н()орм;:11ии впача.ле лля доно.( Ч,|11)Л II Л{);р Numilll .Л|1КерИ11Й lOllbl iriopnii o6,iaci.t, ;i .атсм и д. 1я иг()рг)й области .лисп.лейно о ());iii;ia. 1 лми сраинения нет i«Ь на И1)1чолг 22 Г лпка 7i. то Г1)и появ- .лении един)1 ниио сит.ча la на выход 17 б.к 1к;) 10 ;(sii ;нстся единичный сиг на.л. ксгторый к-;и 1, if .H i:, I S 1Г()1. 1 riaer па (четный ИМ; 1 (/ч-i-li- o разряд,) счегчика 3

адреса (так как триггер 26 находится в нулевом состоянии). Таким образом, осуществляется пропуск области дисплейного файла. Затем просходит считывание маркерного слова маркерной зоны следуюн1ей области и цикл повторяется до тех пор, пока не будет просмотрена вся оперативная память.

Формула изобретения

Ассоциативное запоминающее устройство д, 1я дисплея, содержап1ее первый и второй счетчики адреса, коммутатор адреса, буферный регистр, блок оперативной памяти и блок управления, причем выходы разрядов счетчиков адреса подключены к информационным входам коммутаюра, 1И,1Х()Д кого- рого соединен с адресным входом блока оперативной памяти и входом признаков ветвления б.чока управления, информационные вход и выход блока оперативной памяти соедипены соответственно с выходом и первым входом буферного регистра, второй вход и выход которого ЯВ.-1ЯЮТСЯ соответственно информационными входом и вьгчодом С1 р|)йстна, 1К )ный, BT())()ii и г)ети11 выходы

блока управления подключены соответственно к счетному входу первого счетчика адреса, входу записи /чтения блока оперативной памяти и управляющему входу коммутатора адреса, входы разрядов первого счетчика адреса являются адресными входами устройства, отличающееся тем, что, с целью повыщения быстродействия устройства, в него введены блок поразрядного сравнения, первый и второй элементы И

и регистр идентификатора, вход которого является входом задания области идентификации устройства, а выход соединен с первым информационным входом блока поразрядного сравнения, второй информационный вход которого подключен к выходу буферного регистра, четвертый, пятый и Н1естой выходы блока управления соединены с первыми входами элементов И и первым и вто- м,1м устаповочными входами блока пораз- 1ЯДНОГО сравнения, прямой и инверсный

выходы которого соединены соответственно с вторыми входами, вторО1 о и первого элементов И, выходы которых подключены соответственно к установочному входу первого и второго счетчиков адреса.

ffrnS

От 6

пн п

n-m k i n-m+K

28

-Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство отображения графической информации | 1982 |

|

SU1111197A1 |

| Ассоциативное оперативное запоминающее устройство | 1989 |

|

SU1714682A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Двухуровневое устройство для управления памятью микрокоманд | 1987 |

|

SU1513448A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Имитатор канала | 1987 |

|

SU1467556A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

Изобретение относится к вычислительной технике. Цель изобретения состоит в повышении быстродействия устройства при решении задачи ассоциативного поиска в больших массивах информации об объекте за счет просмотра только тех частей дисплейного файла, которые содержат элементы, подлежащие отображению в данной ситуации. Устройство содержит блок I оперативной памяти, коммутатор 2 адреса, первый 3 и второй 4 счетчики адреса, буферный регистр 5, регистр 6 идентификатора, блок 7 поразрядного сравнения, первый 8 и второй 9 элементы памяти, блок 10 управления. 6 ил. сл со N5 N3 СО сл ruг 12

I

tf 15 16 П В 9

ХК/К /t4/tv

J К v

/77

/ область дисп/1ейного файла

2 область дисплейного файла

/V область дисплейного файла

1 маркерное слодо

Дополнительная i///- д}0рмаи,ия 1 области

2 маркерное слодо

Дополнительная ин- формация 2 области

л маркерное слодо

Лополиительная (рормаиня N области.

9иг. 6

Редактор С,. Пекарь Заказ 2873:50

С|)1тав11те. 1Ь В Рулакив

Техред И, ВерееКорректор Л. Бескид

Тираж 589Подписное

ВНИНПН Гос ударственного комитета СССР по делам изобретений и открытий

113035, Л осква, Ж 35. Раушскан наб,, д. 4/5 Производственнол о. 1играфичеекое преднриятие, г. Ужгород, ул. Проектная. 4

; Области, отобрата- емого объекта iM i-S о5листеИ

az. 5

Оснодной дисплейный г срайл (1-N области)

Вспомогате/1ьный дисплейный файл области)

| ШИРИН А | |||

| Г., Дерюгин А | |||

| А | |||

| Цифровые вычислительные машины (память ЦВМ).-М.; Сов | |||

| радио, 1976, с | |||

| ПРИСПОСОБЛЕНИЕ ДЛЯ АВТОМАТИЧЕСКОГО ТАРТАНИЯ | 1915 |

|

SU415A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-21—Подача