Изобретение относится к импульсной технике и может быть использовано для контроля и диагностики цифровых устройств. Целью изобретения является расширение функциональных возможностей генератора за счет формирования инверсных псевдослучайных кодов.

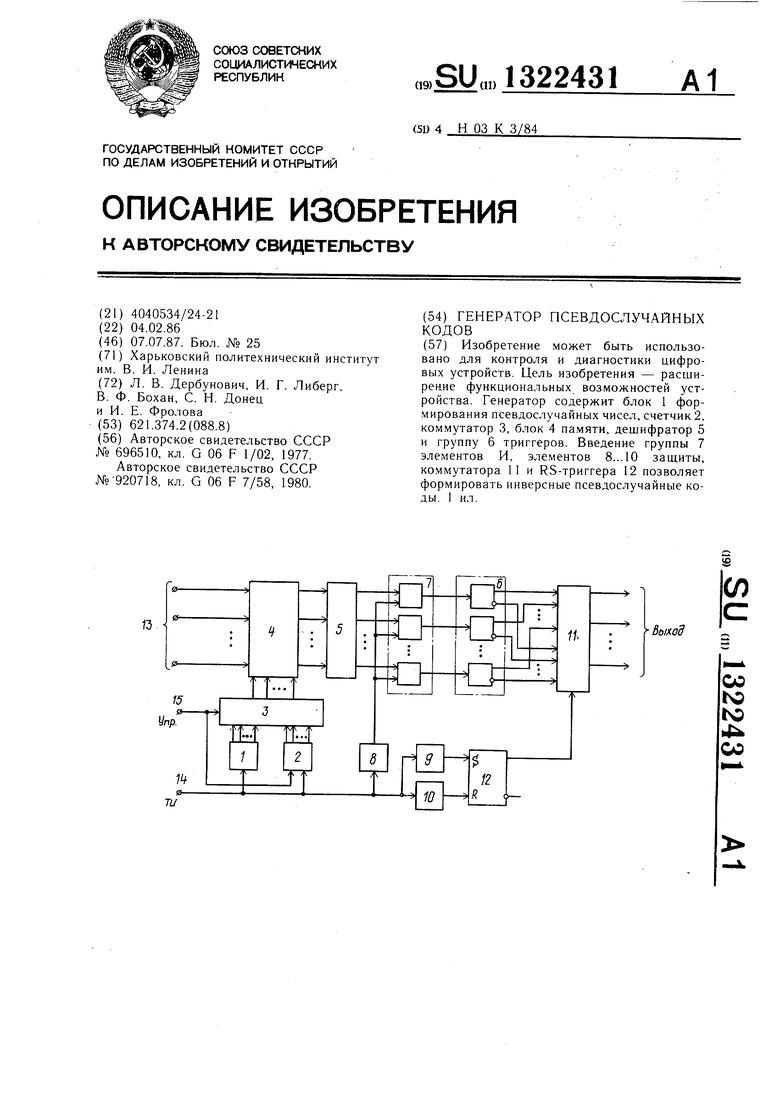

На чертеже приведена структурная схема генератора псевдослучайных кодов.

Генератор псевдослучайных кодов содержит блок 1 формирования псевдослучайных чисел, счетчик 2, первый коммутатор 3, блок 4 памяти, выходы которого соединены с входами дешифратора 5, группу 6 триггеров, группу 7 элементов И, первый, второй и третий элементы 8-10 задержки, второй коммутатор 11, RS-триггер 12, группу 13 информационных шин, шину 14 тактовых импульсов, шину 15 управления, соединенную с входом управления первого коммутатора 3 и входом управления счетчика 2, вход синхронизации которого соединен с входом первого элемента 8 задержки и входами второго и третьего элементов 9 и 10 задержки, выходы которых соединены соответственно с S-H Р-входами RS-триггера 12, выход которого соединен с входом управления второго коммутатора 11, входы первой и второй групп входов которого соединены соответственно с прямыми и инверсными выходами группы 6 триггеров, счетные входы которой соединены с выходами группы 7 элементов И, первые входы которой соединены с соответствующими выходами дешифратора 5, а вторые входы соединены между собой и с выходом первого элемента 8 задержки. Шина 14 тактовых импульсов соединена с входами синхронизации блока 1 формирования псевдослучайных кодов и счетчика 2. выходы которых соединены соответственно с входами первой и второй групп входов первого ком.мутатора 3, выходы которого соединены с соответствую иди ми адресными входами блока 4 памяти, информационные входы которого соединены с соответствующими шинами группы 13 информационных шин.

Генератор псевдослучайных кодов работает следующим образом.

В режиме задания частоты переключения разрядов формируемых кодов на группу 13 информационных щин, т. е. на информационные входы блока 4 памяти, поступают коды номеров выходов устройства. Поступающий на вход управления первого ко.ммутатора 3 сигна:: управления подключает выходы счетчика 2 к адресным входам блока 4 памяти. Этим же сигналом разрешается работа счетчика 2 и происходит последовательное заполнение всех ячеек блока 4 памяти кодами номеров выходов устройства. Для каждого из кодов выбрано определенное число ячеек блока 4 памяти, в которые записывается код одного

и того же выхода устройства. Это позволяет при условии равновероятного выбора адресов блока 4 памяти считывать из неги коды номеров выходов устройства с заданной для каждого выхода частотой переключения. После окончания процесса заполнения блока 4 памяти на вход управления первого коммутатора 3 поступает сигнал управления, который отключает адресные входы йлока 4 памяти от счет чика 2 и подключает их к блоку 1 формирования псев.дослучайных чисел. На этом режим задания частоты переключения каждого из разрядов генерируемых кодов завершается.

5 В режиме генерации псевдослучайных кодов импульсы тактовой частоты, поступающие на тину 14 тактовых импульсов, обеспечивают формирование блоком 1 равномерно распределенных псевдослучайных чисел, поступающих на адресные входы бло0 ка 4 памяти. Код номера выхода устройства с выхода блока 4 памяти поступает на вход дешифратора 5 и обеспечивает возбуждение одного из его выходов. Задержанный на время срабатывания блока 4 памяти и де5 шифратора 5 первым элементом 8 задержки импульс тактовой частоты поступает на вторые входы группы 7 элементов И, вызывает переключение одного из триггеров группы 6 триггеров по счетному входу, который соответствует возбужденному

0 выходу дешифратора 5.

Так как RS-триггер 12 в исходном положении установлен в нулевое состояние, то на входе управления второго коммутатора 1 1 сигнал равен нулю и на выходы устройства проходят сигналы с прямых выходов

5 триггеров группы 6 триггеров.

Таким образом, новый код на выходах устройства отличается от предыдущего кода только в одном разряде.

И.мпульс тактовой частоты, пришедший на вход второго элемента 9 задержки, задерживается на время, необходимое для завершения переходных процессов в блоках 6, 7 и 1, и поступает на S-вход RS-триггера 12, обеспечивая появление на входе управления второго коммутатора 11. еди5 ничного сигнала, что приводит к подключению на входы устройства инверсных выходов триггеров группы 6 триггеров, т. е. осуществляется формирование инверсного значения кода. Тот же импульс тактовой частоты, пришедший на вход третьего эле0 мента 10 задержки, задерживается им на время, обеспечивающее равное время нахождения на выходах устройства прямого и инверсного кодов, и поступает на R-вход RS-триггера 12, возвращая его в исходное состояние, что снова приводит к появ5 лению на выходах устройства прежнего прямого значения кода.

С приходом следующего тактового импульса процесс повторяется.

0

Формула изобретения

Генератор псевдослучайных кодов, содержащий блок формирования псевдослучайных чисел, счетчик, первый коммутатор, блок памяти, выходы которого соединены с входами дешифратора, группу триггеров, группу информационных шин, шину тактовых импульсов, соединенную с входами синхронизации блока формирования псевдослучайных кодов и счетчика, выходы которых соединены соответственно с входами первой и второй групп входов первого коммутатора, выходы которого соединены с соот- ветствуюш,ими адресными входами блока памяти, информационные входы которого соединены с соответствуюш.ими шинами группы информационных шин, отличающийся тем, что, с целью расширения функциональных возможностей за счет формирования инверс0

ных псевдослучайных кодов, в него введены группа элементов И, первый, второй и третий элементы задержки, второй коммутатор, RS-триггер, шина управления, соединенная с входом управления первого коммутатора и входом управления счетчика, вход синхронизации которого соединен с входом первого элемента задержки и входами второго и третьего элементов задержки, выходы которых соединены соответственно с S- и R-входами RS-триггера, выход которого соединен с входом управления второго коммутатора, входы первой и второй групп входов которого соединены соответственно с прямыми и инверсными выходами группы триггеров, счетные входы которых соединены с выходами группы элементов И, первые входы которой соединены с соответствующими выходами дешифратора, а вторые входы соединены между собой и с выходом первого элемента задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1987 |

|

SU1540025A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1264317A2 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

Изобретение может быть использовано для контроля и диагностики цифровых устройств. Цель изобретения - расширение функциональных возможностей устройства. Генератор содержит блок 1 формирования псевдослучайных чисел, счетчик 2, коммутатор 3, блок 4 памяти, дешифратор 5 и группу 6 триггеров. Введение группы 7 элементов И, элементов 8...10 защиты, коммутатора 11 и RS-триггера 12 позволяет формировать инверсные псевдослучайные коды. 1 ил. Выход со IND to оо

| Генератор псевдослучайных кодов | 1977 |

|

SU696510A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор псевдослучайных кодов | 1980 |

|

SU920718A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-04—Подача