1J3

Изобретение относится к технике передачи данных и может быть использовано для передачи цифровой информации в информационных системах.

Цель изобретения - повышение помехоустойчивости передачи информации за счет многократного определения каждого разряда принимаемого кода.

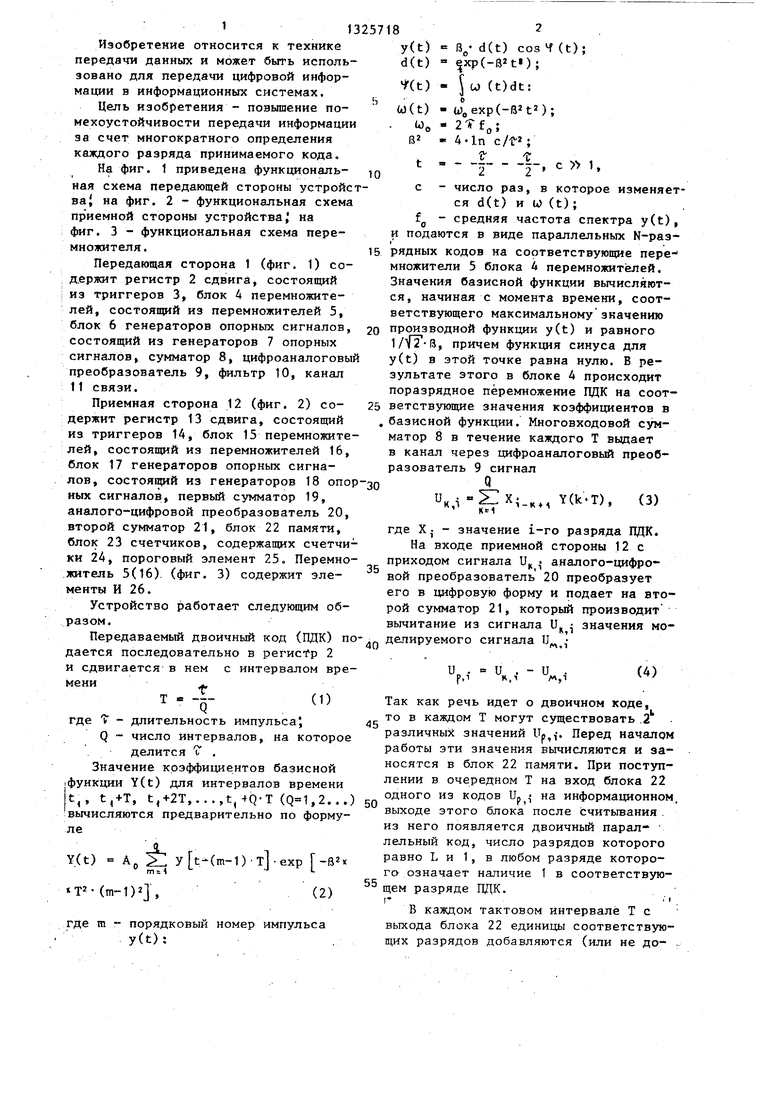

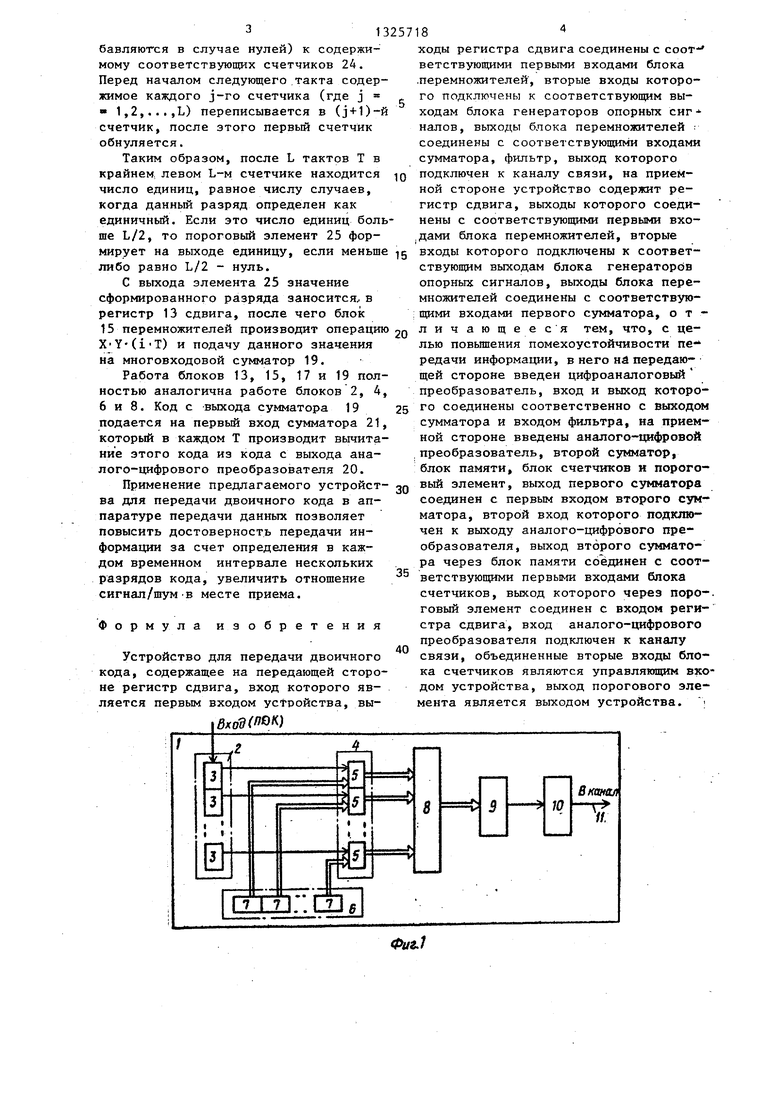

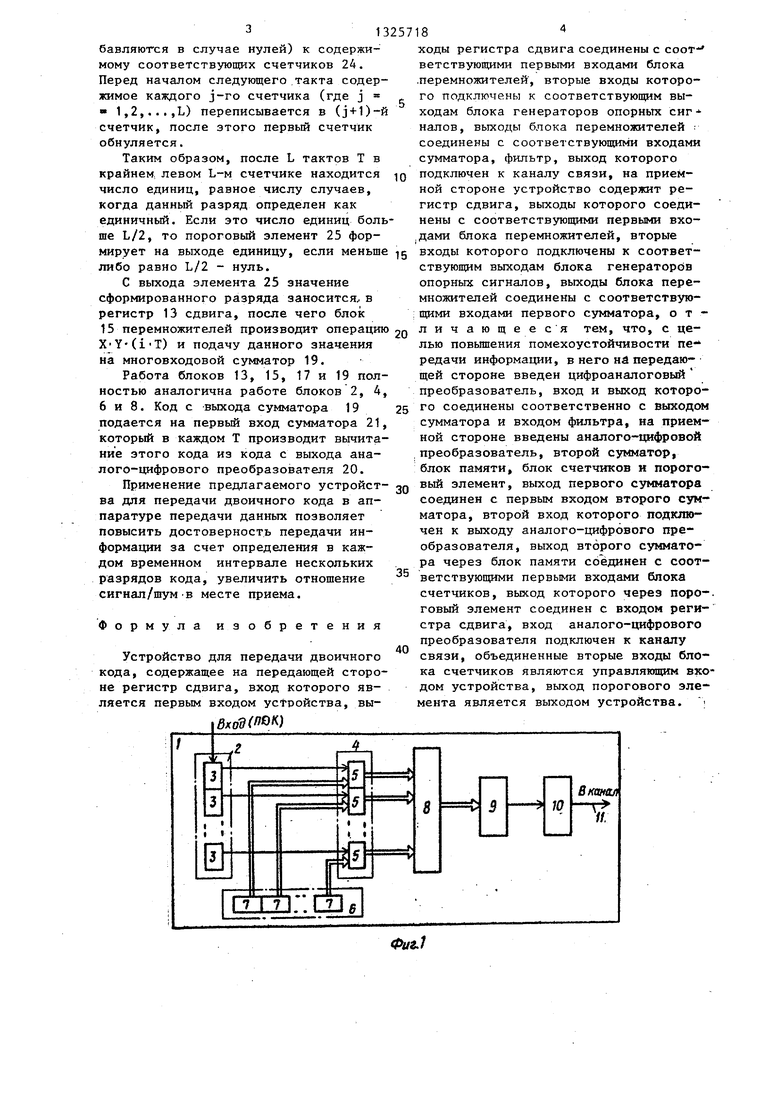

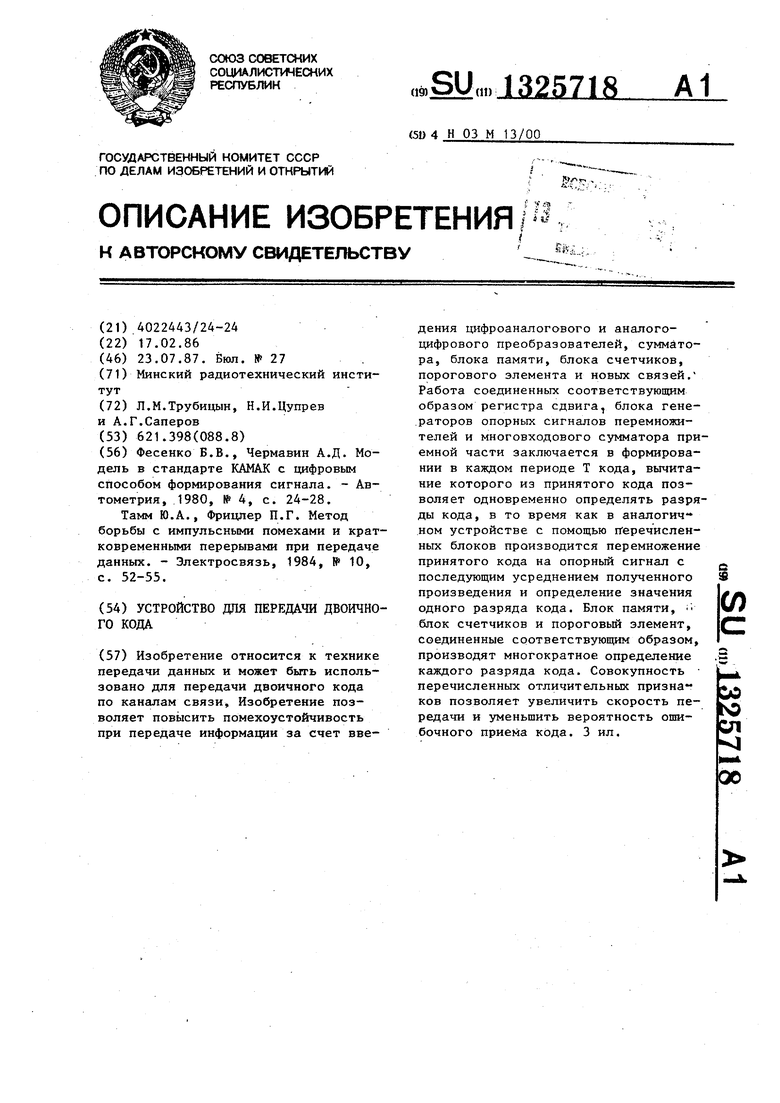

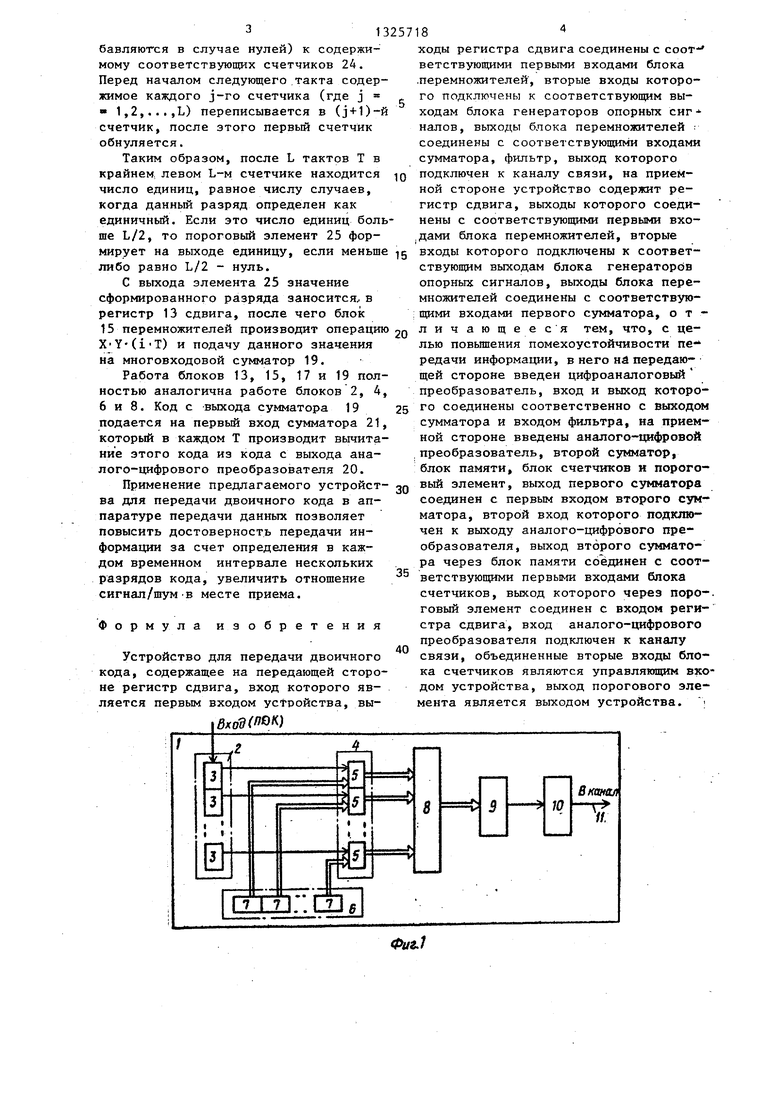

На фиг. 1 приведена функциональ- ная схема передающей стороны устройства i на фиг, 2 - функциональная схема приемной стороны устройства, на фиг. 3 - функциональная схема перемножителя.

Передающая сторона 1 (фиг, 1) содержит регистр 2 сдвига, состоящий из триггеров 3, блок 4 перемножителей, состоящий из перемножителей 5, блок 6 генераторов опорньзх сигналов, состоящий из генераторов 7 опорных сигналов, сумматор 8, цифроаналоговый преобразователь 9, фильтр 10, канал 11 связи.

Приемная сторона 12 (фиг. 2) со- держит регистр 13 сдвига, состоящий из триггеров 14, блок 15 перемножителей, состоящий из перемножителей 16, блок 17 генераторов опорных сигналов, состоящий из генераторов 18 опор ных сигналов, первый сумматор 19, аналого-цифровой преобразователь 20, второй сумматор 21, блок 22 памяти, блок 23 счетчиков, содержащих счетчики 24, пороговый элемент 25„ Перемножитель 5(16). (фиг. 3) содержит элементы И 26.

Устройство работает следующим образом.

Передаваемый двоичный код (ПДК) подается последовательно в регистр 2 и сдвигается в нем с интервалом времени

Т - (1)

t

Q

где 7 - длительность импульса

Q число интервалов, на которое

делится

Значение коэффициентов базисной 1ФУНКЦИИ Y(t) для интервалов времени t,, t,+T, t,+2T,...,t,4Q.T (,2...) 50 вычисляются предварительно по формуле

i Ар . У t-Cm-D Tl-exp

m S 4

1)2j,(2)

где m порядковый номер импульса y(t):

2

V dCt) cos Ч(t);

xp();

5 U) (t)dt:

Ыоехр(-Виа);

W,

2f f.;

В - 4«1п

f Z t в - --- - --- с 1,

с - число раз, в которое изменяется d(t) и U) (t);

fjj - средняя частота спектра y(t), и подаются в виде параллельных N-раз- рядных кодов на соответствующие пере- множители 5 блока 4 перемножитёлей. Значения базисной функции вычисляются, начиная с момента времени, соответствующего максимальному значению производной функции y(t) и равного , причем функция синуса для y(t) в этой точке равна нулю. В результате этого в блоке 4 происходит поразрядное перемножение ПДК на соответствующие значения коэффициентов в базисной функции. Многовходовой сумматор 8 в течение каждого Т выдает в канал через цифроаналоговый преобразователь 9 сигнал

Q U,.,,, Y(k.T), (3)

где Х- - значение i-ro разряда ПДК.

На входе приемной стороны 12 с приходом сигнала и„ аналого-цифровой преобразователь 20 преобразует его в цифровую форму и подает на второй сумматор 21, который производит вычитание из сигнала U значения моделируемого сигнала U,F.

H.V - M,,(4)

5

0

5

Так как речь идет о двоичном коде, то в каждом Т могут существовать .2 различных значений Up,f. Перед началом работы эти значения вычисляются и заносятся в блок 22 памяти. При поступлении в очередном Т на вход блока 22 одного из кодов Up на информационном, выходе этого блока после считывания . из него появляется двоичный парал- лельный код, число разрядов которого равно L и 1, в любом разряде которого означает наличие 1 в соответствующем разряде ПДК.

г .

Б каждом тактовом интервале Т с

выхода блока 22 единицы соответствующих разрядов добавляются (или не до- .

313

бавляются в случае нулей) к содержимому соответствующих счетчиков 24. Перед началом следующего.такта содержимое каждого j-ro счетчика (где j 1,2,..,,L) переписывается в (j+1)-ft счетчик, после этого первый счетчик обнуляется.

Таким образом, после L тактов Т в крайнем левом L-M счетчике находится число единиц, равное числу случаев, когда данный разряд определен как единичный. Если это число единиц больше L/2, то пороговый элемент 25 формирует на выходе единицу, если меньше либо равно L/2 - нуль.

С выхода элемента 25 значение сформированного разряда заносится в регистр 13 сдвига, после чего блок 15 перемножителей производит операцию X Y (i T) и подачу данного значения на многовходовой сумматор 19.

Работа блоков 13, 15, 17 и 19 полностью аналогична работе блоков 2, 4, 6 и 8. Код с выхода сумматора 19 подается на первый вход сумматора 21, который в каждом Т производит вычитание этого кода из кода с выхода аналого-цифрового преобразователя 20.

Применение предлагаемого устройства для передачи двоичного кода в аппаратуре передачи данных позволяет повысить достоверность передачи информации за счет определения в каждом временном интервале нескольких разрядов кода, увеличить отнощение сигнал/шум-в месте приема.

Формула изобретения

Устройство для передачи двоичного кода, содержащее на передающей стороне регистр сдвига, вход которого является первым входом усфройства, вы

Q д

:

0

5

0

5

0

18

ходы регистра сдвига соединены с соот ветствующими первыми входами блока .перемножителей, вторые входы которого подключены к соответствующим выходам блока генераторов опорных сиг налов, выходы блока перемножителей соединены с соответствующими входами сумматора, фильтр, выход которого подключен к каналу связи, на приемной стороне устройство содержит регистр сдвига, выходы которого соединены с соответствующими первыми вхо- ,дами блока перемножителей, вторые входы которого подключены к соответствующим выходам блока генераторов опорных сигналов, выходы блока перемножителей соединены с соответствующими входами первого сумматора, отличающееся тем, что, с целью повыщения помехоустойчивости пе редачи информации, в него на передающей стороне введен цифроаналоговый преобразователь, вход и выход которого соединены соответственно с выходом сумматора и входом фильтра, на приемной стороне введены аналого-цифровой преобразователь, второй сумматор, блок памяти, блок счетчиков и пороговый элемент, выход первого сумматора соединен с первым входом второго сумматора, второй вход которого подключен к выходу аналого-цифрового преобразователя, выход второго сумматора через блок памяти соединен с соответствующими первыми входами блока счетчиков, выход которого через поро-. говый элемент соединен с входом регистра сдвига, вход аналого-цифрового преобразователя подключен к каналу связи, объединенные вторые входы блока счетчиков являются управляющим вхо- дом устройства, выход порогового элемента является выходом устройства. ;

BKdd(nf)t()

X 1

- 26

III

I Из канала

N

Фиг.З

Составитель В.Бородин Редактор И.Шулла Техред Л.Сердюкова

Заказ 3127/57 Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

Корректор Н.Король

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи двоичного кода | 1987 |

|

SU1511865A2 |

| Устройство для разделения сигналов в многоканальных системах передачи | 1988 |

|

SU1598190A1 |

| Устройство для передачи двоичного кода | 1988 |

|

SU1547014A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| СПОСОБ КОМПРЕССИИ-ДЕКОМПРЕССИИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2488960C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1693735A1 |

| Функциональный преобразователь нескольких переменных | 1986 |

|

SU1387022A1 |

Изобретение относится к технике передачи данных и может быть использовано для передачи двоичного кода по каналам связи. Изобретение позволяет повысить помехоустойчивость при передаче информации за счет введения цифроаналогового и аналого- цифрового преобразователей, сумматора, блока памяти, блока счетчиков, порогового элемента и новых связей. Работа соединенных соответствующим образом регистра сдвига, блока гене- .раторов опорных сигналов перемножителей и многовходового сумматора приемной части заключается в формировании в каждом периоде Т кода, вычитание которого из принятого кода позволяет одновременно определять разряды кода, в то время как в аналогич ном устройстве с помощью перечисленных блоков производится перемножение принятого кода на опорный сигнал с последующим усреднением полученного произведения и определение значения одного разряда кода. Блок памяти, блок счетчиков и пороговый элемент, соединенные соответствующим образом, производят многократное определение каждого разряда кода. Совокупность перечисленных отличительных призна ков позволяет увеличить скорость передачи и уменьшить вероятность ошибочного приема кода. 3 ил. С 8 (Л с

| Фесенко Б.В., Чермавин А.Д | |||

| Модель в стандарте КАМАК с цифровым способом формирования сигнала | |||

| - Автометрия, 1980, № 4, с | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| Тамм Ю.А., Фрицлер П.Г | |||

| Метод борьбы с импульсными помехами и кратковременными перерывами при передаче данных | |||

| - Электросвязь, 1984, № 10, с | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

Авторы

Даты

1987-07-23—Публикация

1986-02-17—Подача