11

Изобретение относится к вьтисли- тельной технике и может быть использовано в системах обработки сигнала, где требуется устранение шумов методом усреднения сигнала по ансамблю реализаций, в частности в медицине при обработке сигналов электроэнце™ .фалограмм и электроннограмм.

Целью изобретения является расти- рение функциональных возможностей устройства за счет возможности усреднения сигнала по произвольному числу реализа ЦИЙ.

На фиГе представлена структурная схема устройства; на фиг,2 - схема блока микропрограммного управленияi на фиг.З - схема арифметико-логического блока.

Устройство для анализа случайных сигналов (фиг.1) содержит аналого- цифровой преобразователь (АЦП) J, арифметико-лоri-гческий блок 2, блок 3 памяти, второй регистр 4, блок 5 микропрограммного управления, генератор 6 тактовых импульсов, счетчик 7, третий цифроаналоговый преобразователь 8, вход 9 команды вьщачи аналогового сигнала среднего знах1ения5 тактовый вход 10, счетчики П 12 и 13, ре гистры 4, 15. и 6, цифроаналоговые. преобразователи 17, 18, демульти- плексоры 19, 20, мультиплексор 21, вход 22 команды вьщачи цифрового сигнала среднего значения,

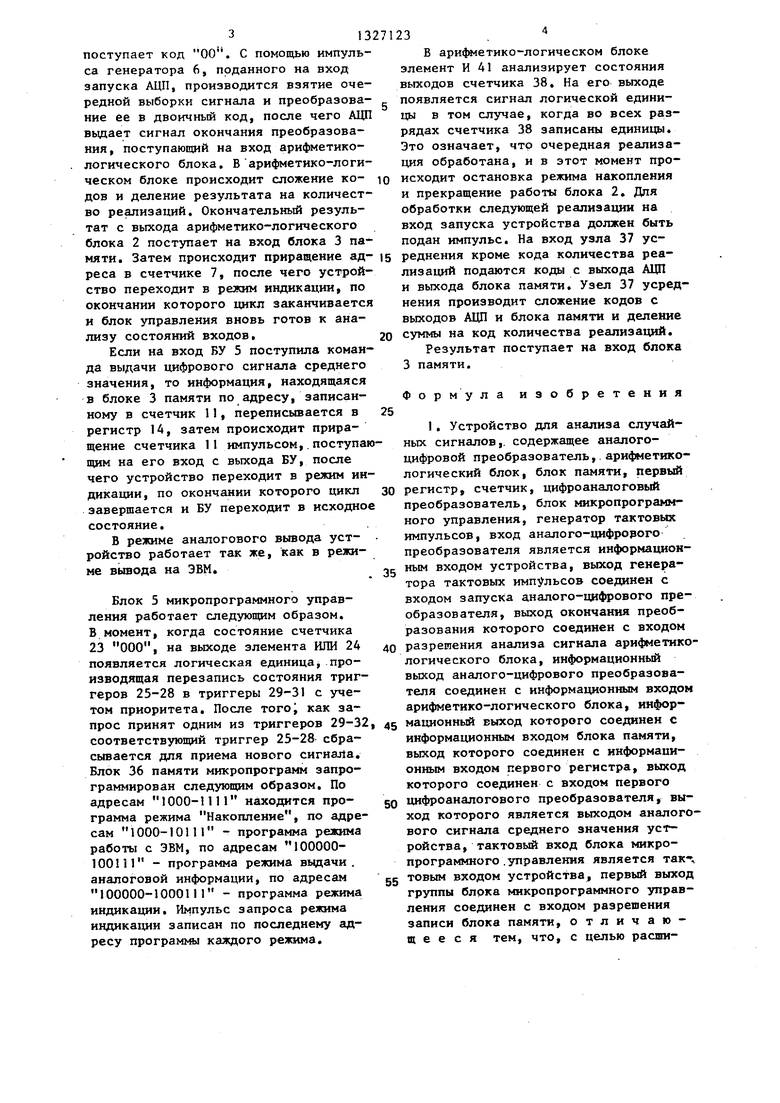

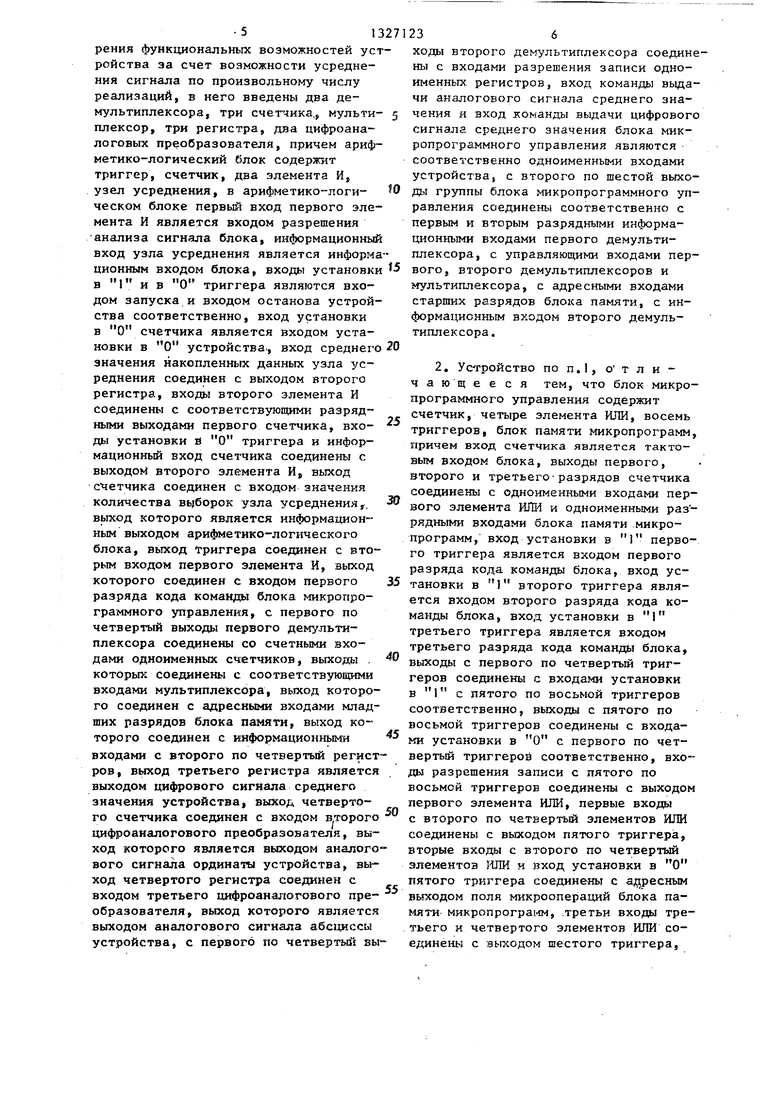

Блок ьшкропрограммного управления (фиг,2) содержит счетчик 23, элемент ИЛИ 24, триггеры 25-32;, элементы ИЛИ 33, 34 и 35, блок 36 памяти микропрограмм.

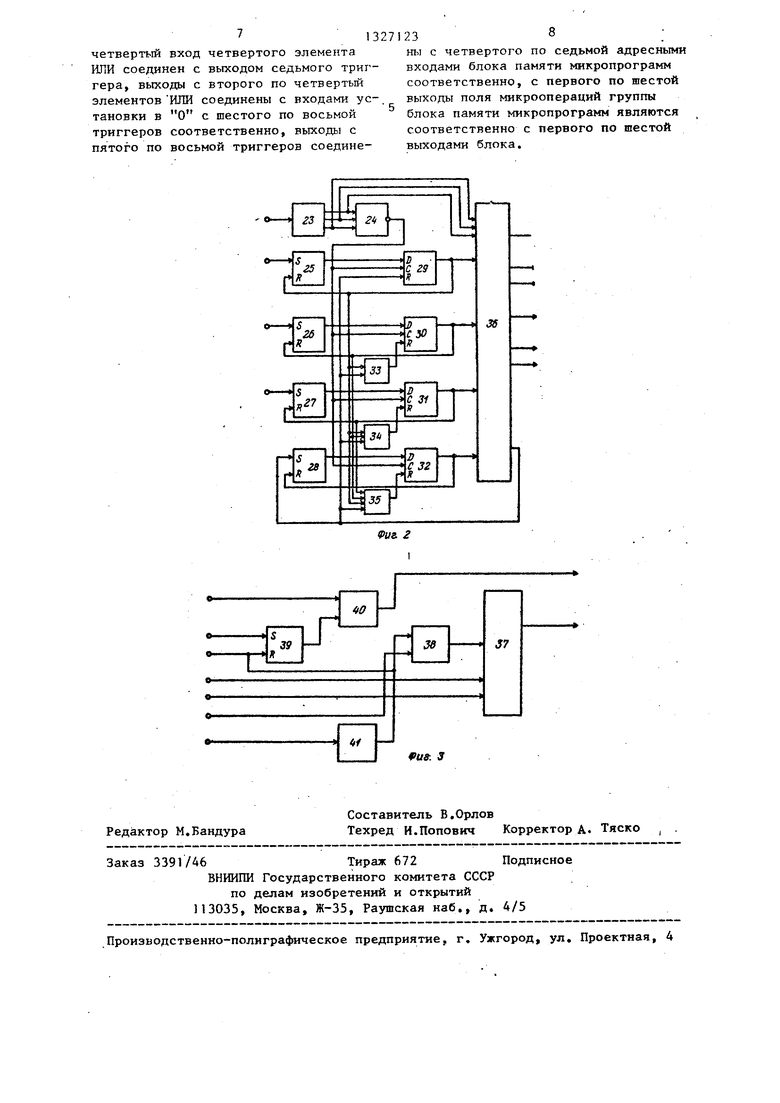

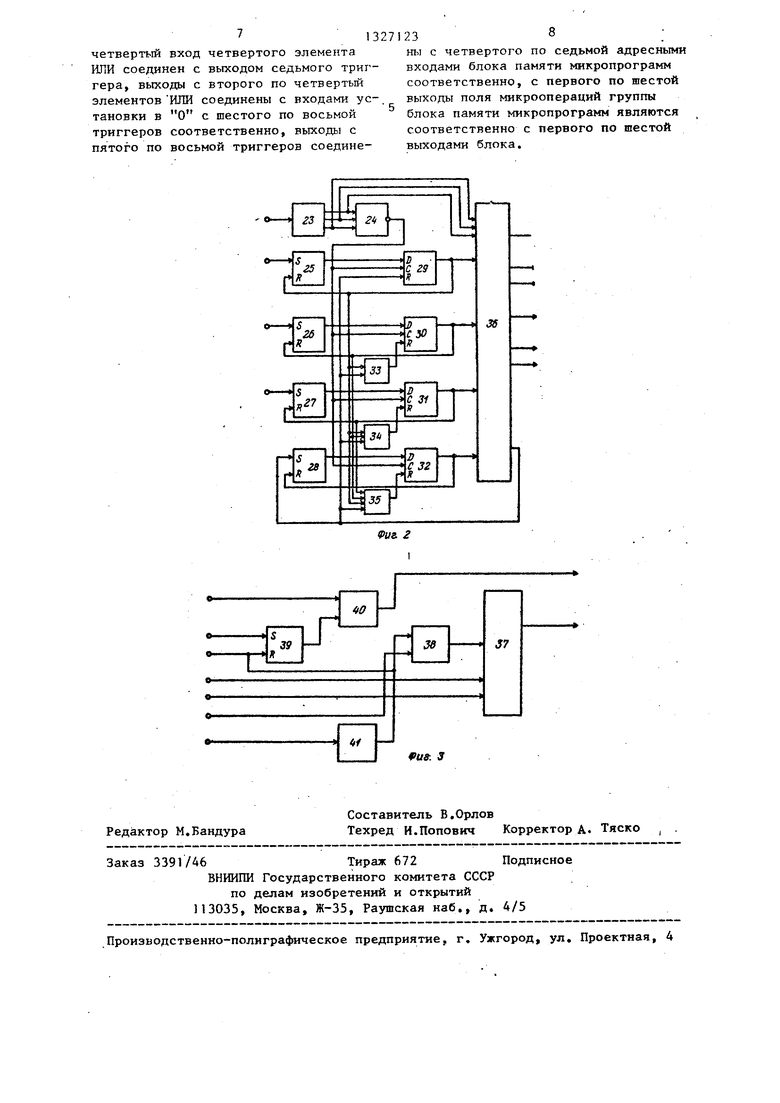

Арифметико-логический блок (фиГвЗ содержит узел 37 усреднения, счетчик 38, триггер 39, элементы И 40, 4,

Устройство работает следуиЕ им образом,

Устройство имеет четыре режима работы: накопления; индика1ши на экран Осциллографа; цифровой вывод на ЭВМ; аналоговый вывод в растянутом масштабе времени (на самописец или другой медленно действующий регистратор). Режимы включаются сигналамиэ поступающими на входы блока 5 { Шкро- программного управления,

Дпя указанных режимов работы ус- тановлан следующий приоритет: режим накопления обладает высшим приоритетом; режим вывода на ЭВМ§ режим аналогового вьшода; режим индикации.

23.

Режим индикации включен в течение всего времени, когда на входах разрядов кода команд блока 5 микропрограммного з Т равления отсутствуют сиг команд режимов с Если на одном из указанных входов появштся сигнал команды, устройство выполняет команду, а затем возвращается в режим индикации , Этим обеспечивается постоянное наличие сигнала на экране осцил- лографаэ независимо от частоты переключения реж:имов. Сигналы на входе кода команд блока 5 микропрограммного травления (БУ) отсутствуют. Двухразрядный дворгчный код 11 с выхода 5У поступает на управляюЕще входы демультиплексоров 19, 20 и мультиплексора в результате чего выходы счетчика соединены с входом блока 3 памяти и входом цифроаналогового преобразователя 17, предназначенного для формирования сигнала горизонтального отклонения луча осциллографа. Выход регистра 6 подключен к входу цифроаналогового преобразователя (иДП) В, предназначенного для формирования Сигнала вертикального откло- мения луча осциллографа. Импульсом, поступающим с выхода БУ- на вход разрешения записи регистра 16, информация, находящаяся в блоке 3 памяти по адресу, установленному в счетчике 13, переписьшается в регистр 16. Затем на информационный вход счетчика 13 поступает импульс, увеличивающий значение счетчика на единицу. С вьпсода регистра 16 информация поступает на вход ЦАП 8, формируя ординату очередной выборки. Абсцисса выборки формируется в ЦАП 17, на вход которого подан код адреса выборки На этом цикл индикации заканчивается БУ.

Режим накопления включается в случае, если на вход первого разряда кода команд БУ поступил сигнал с выхода арифметико-логического блока 2, формируемый из сигнала готовности АЦП в случае, если на вход арифметико-логического блока 2 бьш подан сигнал запуска устройства, означающий качало обработки очередной реализации По сигналу остановки устройства режим накопления останавливается, а сигнал установки в Ч) устройства подается, ес.пи накопление необходимо начать сиа чапа

На управляющие входы дешифраторов к мультиплексора в режиме накопления

313

поступает код 00. С помощью импульса генератора 6, поданного на вход запуска АЦП, производится взятие очередной выборки сигнала и преобразование ее в двоичный код, после чего АЦП вьщает сигнал окончания преобразования, поступающий на вход арифметико- логического блока, В арифметико-логическом блоке происходит сложение ко- дов и деление результата на количество реализаций. Окончательный результат с вьрсода арифметико-логического блока 2 поступает на вход блока 3 памяти. Затем происходит приращение ад- реса в счетчике 7, после чего устройство переходит в режим индикации, по окончании которого цикл заканчивается и блок управления вновь готов к анализу состояний входов,

Если на вход БУ 5 поступила команда выдачи цифрового сигнала среднего значения, то информация, находящаяся в блоке 3 памяти по адресу, записанному в счетчик 11, переписьгоается в регистр 14, затем происходит приращение счетчика 11 импульсом,.поступающим на его вход с выхода БУ, после чего устройство переходит в режим ии- дикации, по окончании которого цикл завершается и БУ переходит в исходное состояние.

В режиме аналогового вывода уст- ройство работает так же, как в режиме вывода на ЭВМ.

Блок 5 микропрограммного управления работает следующим образом. В момент, когда состояние счетчика 23 000, на выходе элемента ИЛИ 24 появляется логическая единицаj производящая перезапись состояния триггеров 25-28 в триггеры 29-31 с учетом приоритета. После того как запрос принят одним из триггеров 29-32 соответствующий триггер 25-28 сбрасывается для приема нового сигнала. Блок 36 памяти микропрограмм запрограммирован следующим образом. По адресам 1000-1111 находится про- грамма режима Накопление, по адресам 1000-10111 - программа режима работы с ЭВМ, по адресам 100000- 100111 - программа режима вьщачи . аналоговой информации, по адресам 100000-1000111 - программа режима индикации. Импульс запроса режима индика1и{н записан по последнему адресу программы каждого режима.

23 ,

Б арифметико-логическом блоке злемент И 41 анализирует состояния выходов счетчика 38, На его выходе появляется сигнал логической единицы в том случае, когда во всех разрядах счетчика 38 записаны единицы. Это означает, что очередная реализация обработана, и в этот момент происходит остановка режима накопления и прекращение работы блока 2. Для обработки следующей реализации на вход запуска устройства должен быть подан импульс. На вход узла 37 усреднения кроме кода количества реализаций подаются коды с выхода АЦП и выхода блока памяти. Узел 37 усред- нення производит сложение кодов с выходов АЦП и блока памяти и деление суммы на код количества реализаций.

Результат поступает на вход блока 3 памяти.

Фор м у ла изобретения

I, Устройство для анализа случайных сигиапов,. содержащее аналого- цифровой преобразователь,.арифметико- логический блок, блок пг1мяти, первый регистр, счетчик, цифроаналоговый преобразователь, блок микропрограммного управления, генератор тактовых импульсов, вход анапого-цифророго преобразователя является информацион- иым входом устройства, выход генератора тактовых импульсов соединен с входом запуска аналого-цифрового преобразователя, выход окончания преобразования которого соединен с входом разрешения анализа сигнала арифметико логического блока, информационный выход аналого-цифрового преобразователя соединен с информационным входом арифметико-логического блока, информационный выход которого соединен с информационным входом блока памяти, выход которого соединен с информационным входом первого регистра, выход которого соединен с входом первого цифроаналогового преобразователя, выход которого является выходом аналогового сигнала среднего значения устройства, тактовый вход блока микропрограммного .управления является так товым входом устройства, первый выход группы блока микропрограммного управления соединен с входом разрешения записи блока памяти, отличающееся тем, что, с целью расши513

рения функциональньпс возможностей устройства за счет возможности усреднения сигнала по произвольному числу реализаций, в него введены два де мультиплексора, три счетчика., мульти- плексор, три регистра, два дифроана- логовых преобразователя, причем арифметико-логический блок содержит триггер, счетчик, два элемента И, узел усреднения, в арифметико-логи- ческом блоке первьй вход первого элемента И является входом разрешения анализа сигнала блока, информационный вход узла усреднения является информационным входом блока, входы установки в 1 и в О триггера являются входом запуска и входом останова устройства соответственно, вход установки в О счетчика является входом установки в О устройства., вход среднего значения накопленных данных узла усреднения соединен с выходом второго регистра, входы второго элемента И соединены с соответствующими разрядными выходами первого счетчика, вхо- ды установки б О триггера и информационный вход счетчика соединены с выходом второго элемента И, выход с четчика соединен с входом значения количества выборок узла усреднения,. вь1ход которого является информационным выходом арифметико-логического блока, выход триггера соединен с вторым входом первого элемента И, выход которого соединен с входом первого разряда кода команды блока микропрограммного управления, с первого по четвертый выходы первого демульти- плексора соединены со счетными входами одноименных счетчиков, выходы . которых соединены с соответствующими входами мультиплексора, выход которого соединен с адресными входами младших разрядов блока памяти, выход которого соединен с информационньми входами с второго по четвертый регист ров, выход третьего регистра является выходом цифрового сигнала среднего значения устройства, выход четверто

го счетчика соединен с входом второго

цифроаналогового преобразователя, вы ход которого является выходом аналогового сигнала ординаты устройства, выход четвертого регистра соединен с входом третьего цифроаналогового преобразователя, выход которого является выходом аналогового сигнала абс1диссь устройства, с первого по 4eTBepTbd вы

5 0 О 5

0

236

ходы второго демультиплексора соединены с входами разрешения записи одноименных, регистров, вход команды выдачи аналогового сигнала среднего значения и вход жомандь выдачи цифрового сигнала среднего значения блока микропрограммного управления являются соответств€шно одноименными входами устройства с второго по шестой выходы группы блока микропрограммного управления соединены соответственно с первым и вторым разрядными информационными входами первого демультиплексора, с управляющими входами первого, второго демультиштексоров и мультиплексора, с адресными входами старших разрядов блока памяти, с информационным входом второго демультиплексора.

2. Устройство по п. , о т л и - чающееся тем, что блок микропрограммного управления содержит счетчик, четыре элемента ИЛИ, восемь триггеров, блок памяти микропрограмм, причем вход счетчика является тактовым входом блока, выходы первого, второго и третьего-разрядов счетчика соединены с одноименными входами первого элемента ИЛИ и одноименными разрядными входами блока памяти микропрограмм, вход установки в 1 первого триггера является входом первого разряда кода команды блока, вход установки в 1 второго триггера является входом второго разряда кода команды блока, вход установки в 1 третьего триггера является входом третьего разряда кода команды блока, выходы с первого по четвертый триггеров соединены с входами установки в 1 с пятого по восьмой триггеров соответственно, выходы с пятого по восьмой триггеров соединены с входами установки в О с первого по четвертый триггеров соответственно, входы разрешения записи с пятого по восьмой триггеров соединены с выходом первого элемента ИЛИ, первые входы с второго по четвертый элементов ИЛИ соединены с выходом пятого триггера, вторые входы с второго по четвертый элементов ИЛИ и вход установки в О пятого триггера соединены с адресным выходом поля микроопераций блока памяти MHKponporpai iM, .третьи входы третьего и четвертого элементов ИЖ соединены с вьгходом шестого триггера.

713271

четвертый вход четвертого элемента ИЛИ соединен с выходом седьмого триггера, выходы с второго по четвертый элементов ИЛИ соединены с входами установки в О с шестого по восьмой триггеров соответственно, выходы с пятого по восьмой триггеров соедине238

ны с четвертого по седьмой адресными входами блока памяти микропрограмм соответственно, с первого по шестой выходы поля микроопераций группы блока памяти микропрограмм являются соответственно с первого по шестой выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006941C1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Микропроцессор | 1983 |

|

SU1195364A1 |

| СИСТЕМА ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006942C1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1987 |

|

SU1490691A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА | 2002 |

|

RU2221267C1 |

| Устройство обработки информации | 1986 |

|

SU1451710A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

Изобретение относится к вычислительной технике и может быть использовано в медицине при обработке сигналов электроэнцефалограмм. Цель изобретения - расширение функциональных возможностей за счет возможности усреднения сигнала по произвольному числу реализаций. Работа устройства основывается на совмещении во време- ии режимов накопления, индикации, аналогового и цифрового вывода информа цки, обеспечивая при этом взаимную независимость указанных режимов. Устройство содержит аналого-цифровой преобразователь 1 , ари етико-логн- ческий блок 2, блок 3 памяти, регистры 4, 14, 15, 16, блок 5 микропрограммного управления, генератор 6 тактовых импульсов, счетчики 7, 11, 12, 13, цифроаналоговые преобразователи 8, 17, 18, демультигшексоры 19 и 20, мультиплексор 21. Устройство позволяет обрабатывать сигналы, устраняя myMt методом усреднения сигнала по ансамблю реализаций 1 з.п. ф-лы, 3 ил. S О)

Редактор М.Бандура

Составитель В.Орлов

Техред И.Поповкч Корректор А. Тяско

Заказ 3391/46Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для вычисления текущей оценки среднего значения | 1982 |

|

SU1049922A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Прозоров С.П | |||

| Цифровой накопитель повторяющихся сигналов | |||

| - Приборы и техника эксперимента, 1984, № 2, с | |||

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

Авторы

Даты

1987-07-30—Публикация

1985-12-13—Подача