лельный регистр 3, формирователь 4 синхросигнала линейных посыпок, блок 5 сдвига, преобразователь 6 основания кода, .блок 7 памяти, блок 8 контроля

Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи с различными передающими средами.

Цель изобретения - повьшение поме-5 цифровой суммы на границах к одовых

хозащищенности,групп, блок 9 счетчиков цифровой сумНа фиг.1 представлена структурнаямы в кодовой группе, блок 10 стробиэлектрическая схема кодера кода 3B2Q;рования, С5гмматор 11,

на фиг,2 - временные диаграммы, пояс-Кодер кода 3B2Q работает следуюняющие его работу, щим образом,

Кодер кода 3B2Q содержит последо-Преобразование двоичного основа- нательный регистр 1 , формирователь 2ния счисления в четверичное осуще - синхросигнала кодовых групп, парал-ствляется в соответствии с табл,1,

I

Т а б л и ц а 1

В табл,1 рядом с каждой четверичной кодовой группой указано значение цифровой суммы (ЦС) в данной группе, вычисляемое как алгебраическая сумма амплитуд импульсов в кодовой группе при условии, что симво-- лам 0,1,2, 3 кода поставлено в соответствие нормированное напряжение -3, -1 , +1, +3 (фиг,2т),

Над каждой из трех колонок кодовых групп указано значение КС на границ кодовых групп к моменту поступления следующей двоичной группы: так, например, если 11С -2 и поступает двоичная группа 011, то она кодируется группой 32 из левой колонки, что соответствует формированию двух импульсов с амплитудами +3 и +1 и цифровой суммой в кодовой группе +4, Эта сумма (+4) складывается с предыдущим значением на границе кодовых групп (-2). Результат (+2) говорит о том.

лельный регистр 3, формирователь 4 синхросигнала линейных посыпок, блок 5 сдвига, преобразователь 6 основания кода, .блок 7 памяти, блок 8 контроля

что следующая двоичная группа, например 010, кодируется группой из правой колонки с ЦС +2, т,е. группой

20 с амплитудами +1 и -3 и IJC в группе равной -2, Складывая данное значение (-2) с предыдущим значением ЦС на границе кодовых групп (+2), выясняем, что следующая двоичная группа

кодируется группой из средней колонки алфавита с ЦС О и т.д. Таким образом, табл.1 преобразования двоичного

снования счисления в четверичное позволяет построить кодер кода 3B2Q,

сигнал на выходе которого является балансным (т.е. имеет ограниченную ЦС на границах кодовых групп).

Рассмотрим работу кодера кода ЗВ29 на примере преобразования двоич- ной группы 001 (фиг.2),

Двоичный тактовый сигнал, поступающий с входа двоичного тактового сигнала (фиг.2е), проходя через ин3

вертирующий вход последовательного регистра I (фиг.26), записьшает в него (фиг,2 в,г,д) двоичный сигнал (фиг.2а), поступающий с входа двоичного сигнала. Кодовый синхросигнал (фиг.2з) с второго выхода формирователя 2 синхросигнала кодовых групп осуществляет запись первого 1, второго 2 и третьего 3 импульсов

Сигналы с выходов преобразователя 6 основания кода (фиг.2м) поступают также на соответствующие входы блока 9 счетчиков цифровой суммы в кодо- 5 вой группе, на первый вход которого подается сигнал с первого выхода, формирователя 4 синхросигнала линейных посылок (фиг,2и), а н& второй вход - с выхода блока 5 сдвига

(фиг.2в,г,д) с выходов последователь-10 (фиг.2о). v

ного регистра 1 в параллельный ре- Импульсы на выходах блока 9 счет30

гистр 3 (фиг.2к), а также предыдущее значение цифровой суммы с. пыходов (фиг.2р) блока 8 контроля цифровой суммы на границах кодовых групп - в блок 7 памяти (фиг.2л), Для рассматриваемого случая кодирования двоичной группы 001 произвольно принято, 4fo предьщущая ЦС О, что соответствует сочетанию сигналов 010 на выходах блока 8 контроля цифровой суммы на границах кодовых групп (фиг.2р) и на выходах блока 7 памяти (фиг.2л). В инверсном кодовом синхросигнале (фиг,2ж), поступающем с первого выхода формирователя.2 кодового синхросигнала на первый вход преобразователя 6 основания кода, (0) соответствует первому импульсу, а (|) - второму импульсу в кодовой группе на выходах преобразо-вателя 6 основания кода (фиг. 2м) , причем п.ер- вый выход соответствует символу (О), второй выход - символу (I), третий выход - символу (2), четвертый выход - символу (3) четверичного ос нования кода.Как следует из.табл.1, двоичная группа 001 при ЦС О кодируется группой 02, что отражено наличием первого импульса (О) на первом выходе, второго импульса (2) на .третьем выходе (фиг,2и) преобразователя 6 основания кода.

Для устранения состязаний и получения квантованного по времени ли- 5 нейного сигнала импульсы с выходов (фиг.2м) преобразователя 6 основания кода переписываются в блоке 10 стро- бирования инверсным синхросигналом . линейных посылок (фиг.2н) с второго 50 выхода формирователя 4 синхросигнала линейных посылок. Полученные на выходах блока IО стробирования сигна- . лы (фиг.2с) суммируются с соответстчика цифровой суммы в кодовой группе (фиг,2п) соответствуют пяти значениям цифровой суммы в группе -4, -2, О,

15 +2, 4. Так, группа 02, согласно табл.1, имеет ЦС -2, что отражено наличием импульса на втором выходе (фиг.2п) блока 9 счетчиков цифровой суммы в кодовой группе.

20 В блоке 8 контроля цифровой суммы на границах кодовых групп значение ЦС в кодовой группе (-2) (фиг,2п) складьшается с предыдущим значением ЦС О (фиг,2л) (сочетание сигналов

25 010 на выходах блока 7 памяти), а результат (цС -2 ) с выходов блока 8 контроля цифровой суммы на границах кодовых групп (фиг,2р) переписьтает- ся кодовым синхросигналом (фиг.2з)

35

40

на выходе (фиг.2л) блока 4 памяти (сочетание сигналов 100 на выходах блока 7 памяти). К зтому моменту на выходах преобразователя 6 основания кода(фиг,2к) присутствует записанная в параллельном виде следующая двоичная группа 010 (фиг,2а), кодируемая при ЦС -2 в соответствии с табл,1 группой 23 (фиг,2т), преобразуемой на выходе сумматора 11 в импульсы с амплитудами-+2, +3 и т.д.

Последовательный регистр 1 и па-т раллельный регистр 3 могут быть вы полнены в виде тактируемых регистров сдвига на D-триггерах, Формирователь 2 синхросигнала кодовых групп и Фоо- мирователь 4 синхросигнала линейных посылок представляют собой делитель на три и умножитель на два соответственно. Блок 5 сдвига может быть выполнен на D-триггере. Блок 10 стробирования может быть выполнен на четырех D-триггерах, тактовые входы которых подключены к первому входу блока 10 стробирования, а информацивующим весом в сумматоре 11 (уиг,2т),55 оиные - к остальным входам, Сумма- Кодовой группе 02 соответствуют сиг- : тор 11 может быть реализоваи с- по- налы с нормированными амплитудами -3 + 1 (фиг.2т) ,

мощью пассивных делителей на резисторах, входы которых подключены к

Сигналы с выходов преобразователя 6 основания кода (фиг.2м) поступают также на соответствующие входы блока 9 счетчиков цифровой суммы в кодо- вой группе, на первый вход которого подается сигнал с первого выхода, формирователя 4 синхросигнала линейных посылок (фиг,2и), а н& второй вход - с выхода блока 5 сдвига

(фиг.2о). v

чика цифровой суммы в кодовой группе (фиг,2п) соответствуют пяти значениям цифровой суммы в группе -4, -2, О,

+2, 4. Так, группа 02, согласно табл.1, имеет ЦС -2, что отражено наличием импульса на втором выходе (фиг.2п) блока 9 счетчиков цифровой суммы в кодовой группе.

В блоке 8 контроля цифровой суммы . на границах кодовых групп значение ЦС в кодовой группе (-2) (фиг,2п) складьшается с предыдущим значением ЦС О (фиг,2л) (сочетание сигналов

010 на выходах блока 7 памяти), а результат (цС -2 ) с выходов блока 8 контроля цифровой суммы на границах кодовых групп (фиг,2р) переписьтает- ся кодовым синхросигналом (фиг.2з)

на выходе (фиг.2л) блока 4 памяти (сочетание сигналов 100 на выходах блока 7 памяти). К зтому моменту на выходах преобразователя 6 основания кода(фиг,2к) присутствует записанная в параллельном виде следующая двоичная группа 010 (фиг,2а), кодируемая при ЦС -2 в соответствии с табл,1 группой 23 (фиг,2т), преобразуемой на выходе сумматора 11 в импульсы с амплитудами-+2, +3 и т.д.

Последовательный регистр 1 и па-т раллельный регистр 3 могут быть вы полнены в виде тактируемых регистров сдвига на D-триггерах, Формирователь 2 синхросигнала кодовых групп и Фоо- мирователь 4 синхросигнала линейных посылок представляют собой делитель на три и умножитель на два соответственно. Блок 5 сдвига может быть выполнен на D-триггере. Блок 10 стробирования может быть выполнен на четырех D-триггерах, тактовые входы которых подключены к первому входу блока 10 стробирования, а информациоиные - к остальным входам, Сумма- тор 11 может быть реализоваи с- по-

оиные - к остальным входам, Сумма- тор 11 может быть реализоваи с- по-

мощью пассивных делителей на резисторах, входы которых подключены к

$1244803

соответствующим входам сумматора 11, с таблицей истинности, полученной из а выходы через диоды к выходу сумма- таблицы преобразования двоичной сис- тора 11.темы счисления: в четвертичную

Преобразователь 6 основания кода (табл. ) и приведенной .в табл. должен быть вьшолнен в соответствии 2.

Таблица2

00 О 10 01О О О 1

12448038

Продолжение табл. 2

9I24A803. О

В табл.2 А, В и D - 3 символа ис-Продолжение табл.3

ходней двоичной последовательности, .

записываемых в последовательный ре-О 1 О О гистр 1 и хранящиеся на выходах параллельного регистра 3 в течение

кодового интервала; С - кодовьй сиг- -

нал, поступающий на первый вход пре- Последние 4 столбца табл.2 соотобразователя 6 основания кода;.Е, Fветствуют четырем выходным сигналам

и G - сигналы на выходах блока 7преобразователя основания счисления

памяти. (символы (О), (1), (2) и (3) .

В табл.3 приведены разрешенные В соответствии с табл.2, преобсочетания сигналов EFG и соответству-разователь 6 основания кода 8 может

ющие этим сочетаниям значения цифро-быть выполнен в виде четырех дещифвой суммы на границах кодовых групп.ра,торов на восьмиканальных мульти15плексорах типа КП7, адресными входаТаблица 3ми которых являются сигналы А,.В и С,

,:а на информационные входы поступают

J,- р G ЦСсигналы в соответствии с табл.4 - 7,

полученными из табл.2 для входных

Q О 1 +220 символов (О), (1), (2) и (3).

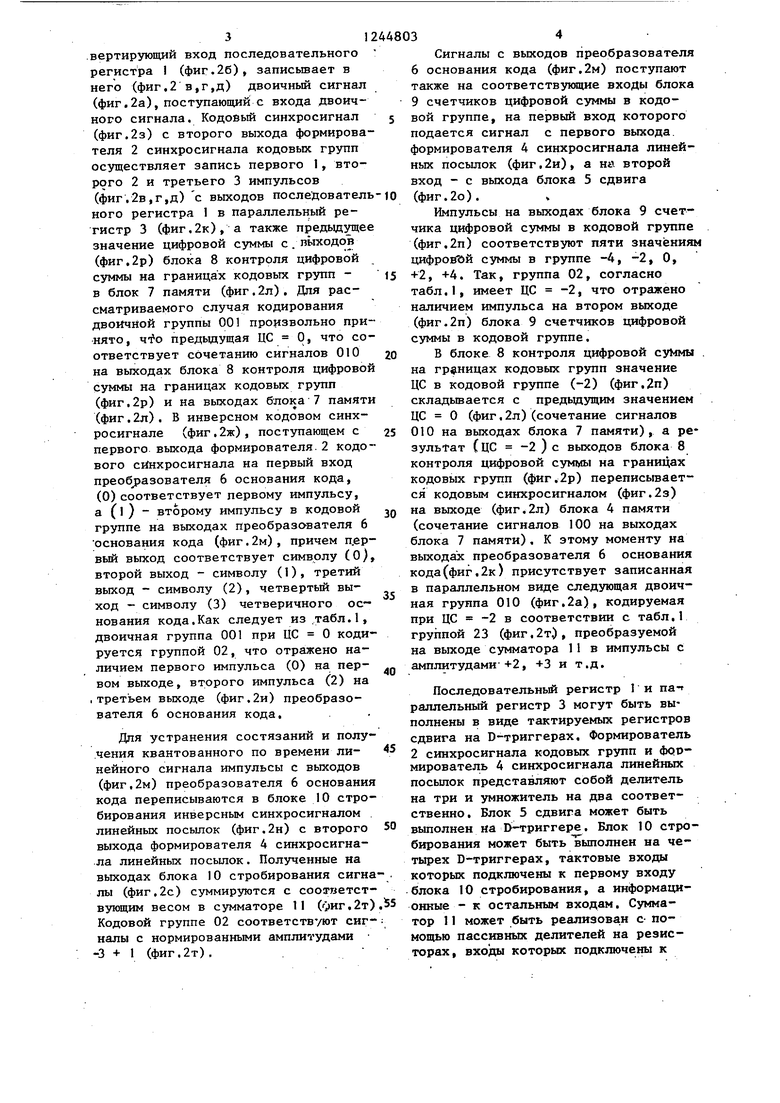

Таблица 4 Таблица истинности дешифратора символов О

1.31244803

В табл.4 - 7 Х - Xj - информационные входы мультиплексоров типа КП7, а под таблицами приведены логические функции, которые должны поступать на соответствующие информа- 5 ционные входы. Например, на вход Х мультиплексора типа КП7 дешифратора

14 Таблица 10

.Таблица истинности дешифратора, реализующего функцию III

X

X

X..

Х

EF

15, 124480316

Блок 9 счетчиков цифровой суммыотражает появление группы 30, преобв кодовой группе должен быть выполненразуемой в импульсы с амплитудами +3,

в соответствии с табл.13, полученной-3 с цифровой суммой в группе, равиз таблиць преобразования двоичнойной нулю (наличие импульса на выходе

системы счисления в четверичную 5блока счетчика цифровой суммы в ко(табл.1). Симво лам кода О, I, 2, 3довой группе 11, табл.13). В соотставятся в соответствие сигналы светствик с табл,13, блок 9 счетчиков,

нормированной амплитудой -3, -1, +1,цифровой суммы в кодовой группе мо+3, что отражено в табл.13. При под-жет быть выполнен в виде дешифратора

счете цифровой суммы в кодовой груп- на пяти мультиплексорах типа КП7,

пе берется алгебраическая сумма амп-таблицы истинности которых приведены

литуд первого и второго символов.в табл.14 - 18.

Например, первая строка в табл.13.

t а б л и ц а 1 з Таблица истинности блока счё тчиков цифровой

суммы в кодовой группе

17124480318

Таблица 14

Таблица истинности мультиплексора, подсчитывающего цифровую сумму (-4)

Таблица

Таблица истинности мультиплексора, подсчи- тьтающего цифровую сумму (-2)

Х Xg Xj Xg Xf

----„ JjYpOOO 001 010 Oil 100 101 110 .Y

21124480322

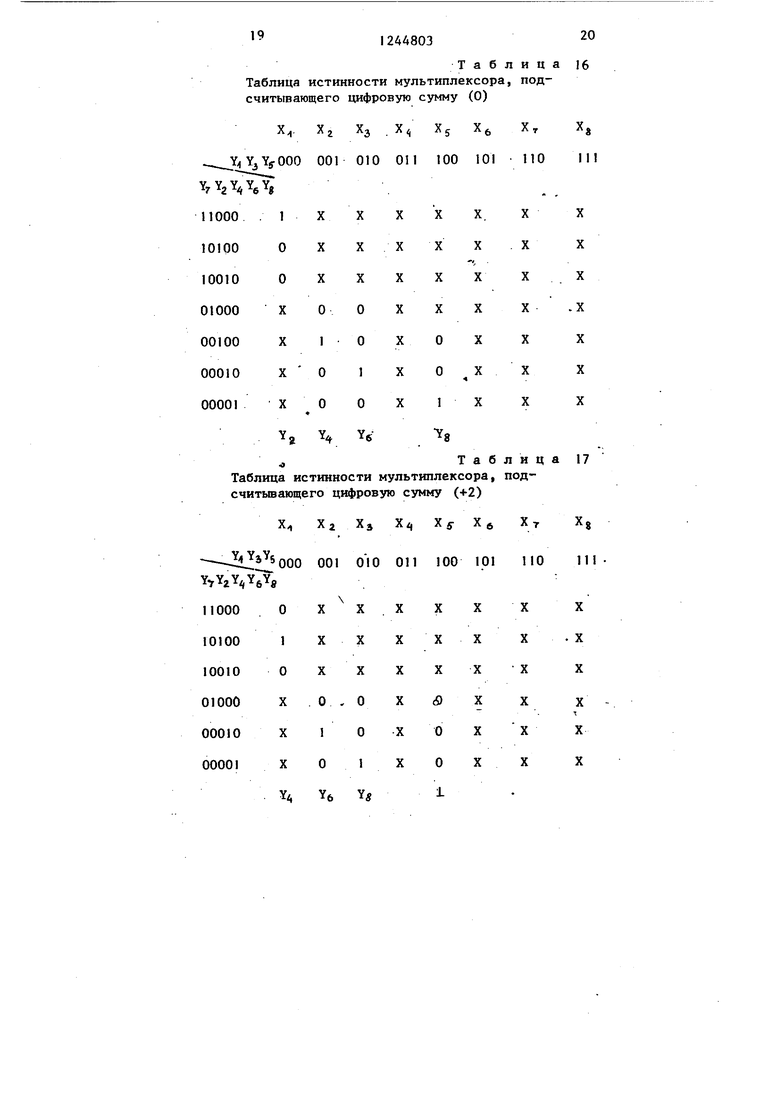

Та.б лица 18

Таблица истинности мультиплексора, подсчитывающего цифровую сумму (М)

231244803 .24

В нем происходит суммирование зна- табл.19, блок 8 контроля цифровой чения предыдущей цифровой суммы с вы- суммы на границах кодовых групп мо- ходов блока 7 памяти (Е F G, табл.19) жет быть выполнен в виде дешифратора и значения цифровой суммы в данной на трех мультиплексорах типа КП7, кодовой группе с выходов блока 9 5 таблицы истинности которых получены счетчиков цифровой суммы (Z Z.t, из табл. 19 и приведены в Z:, ). В соответствии стабл. 20-22.

Таблица 20

Таблица истинности мультиплексора для цифровой суммы (-2)

Xf Хг Xj X/, .Х5- Хб Хг

000 001 010 011 Гбо 101 ПО 2-1 ZjZjZj, Zj

Табл-ица 21

Таблица истинности мультиплексора для цифровой суммы (О)

Х

X

EFG

000 on 010 on 100 101

ZyiZj Z Z iZgT. a б л и ц a 22

Таблица истинности мультиплексора для цифровой суммы (+2)

X,t Хг X Хб Ху EFG000 001 010 011 100 101 110

10000X О XX XXX

Xe

111

100 101

XT

no

8

in

Xg 111 X

X

X

X

X

X X

124480326

Продолжениетабл.22

0XX X XX ОХО X XX

1XО XX-Х X , X1.x XX

;

Блок 7 памяти может быть вьтолнен на трех D-триггерах,.информационные входы которых соединены с входами блока 7 памяти, а тактовые входы - с входами, подключенными к второму выходу формир&вателя 4 синхросигнала кодовых групп.

Формула изобретения

Кодер кода 3B2Q, содержащий сумматор и формирователь синхросигнала ко- довых групп, выход которого подключен к входу формирователя синхросигнала линейных посылок и первому входу преобразователя основания кода, причем вход формирователя, синхросигнала кодовых групп является входом двоич ного тактового сигнала кодера, выходом которого является выход сумматора, о тлич агоще ее si тем, что, с целью повьшения помехозащищенности,, в него введень: последовательный регистр, блок стробирования, блок счетчиков цифровой суммы в кодовой группе, блок контроля цифровой суммы на границах кодовых групп, блок памя

ти, параллельный регистр и блок сдви-; га, к первому входу которого Подключен первый выход формирователя синхросигнала кодовых групп, второй выход

которого подключен к первым входам блока памяти и параллельного регистра, к Остальным входам которого подключены выходы последовательного регистра, прямой и инвертирующий тактовый входы которого являются соответственно входом двоичного сигнала и входом двоичного тактового сигнала, при этом первый выход формирователя синхросигнала линейных посылок подключен к первому входу блока счетчиков цифровой суммы в кодовой группе, к второму входу которого подключен выход блока сдвига, к второму входу которого и первому входу блока стробирования подключен второй выход формирователя синхросигнала линейных посылок, а выходы параллельного регистра подключены к второму, третьему и четвертому входам преобразователя основания кода, выходы которого через блок:стро- бкрованкя подключены к входам сумма- тора и через последовательно соединенные блок c4et4HKOB цифровой суммы S кодовой группе, блок контроля цифровой суммы на границах кодовых групп и блок памяти к пятому, шестому и седьмому входам преобразователя основания кода и шестому, седьмому и восьмому входам блока контроля цифровой суммы на границах кодовых групп,

О 01 О 7 0011 1101071

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодер балансного кода 3B2Q | 1987 |

|

SU1531223A1 |

| Кодер двоичного кода 3В4В-3 | 1986 |

|

SU1444964A1 |

| Система передачи дискретной информации | 1985 |

|

SU1262741A1 |

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

| Устройство регистрации ошибок | 1985 |

|

SU1478346A1 |

| Устройство кодовой синхронизации | 1985 |

|

SU1328941A1 |

| Преобразователь двоичного кода в трехпозиционный код | 1989 |

|

SU1633499A1 |

| Система передачи цифровой информациибииМпульСНыМ СигНАлОМ | 1976 |

|

SU815953A1 |

| Устройство для контроля и идентификации пользователя | 1991 |

|

SU1833902A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

Изобретение относится к электросвязи. Повышается помехозащищенность.. Устройство содержит последовательный регистр (Р) I, формирователь синхросигнала кодовых групп 2, параллельный РЗ, формирователь синхросигнала линейных посылок 4, блок сдвига 5, преобразователь основания кода 6, блок памяти 7, блок контроля (ЛК)8 цифровой суммы на границах кодовых групп, бло.к счетчиков (ЕС) 9 цифровой в кодовой группе , блок стробирования 10 и сумматор 11j В устройстве осуществляется преобразование двоичного основания счисления в четвертичное в соответствии с табл.1. Табл.1 позволяет построить . устройство, сигнал на выходе которого является балансным, т.е. имеет ограниченную цифровз сумму на границах кодовых групп. Цель достигается введением Р 1 и 3,- блока сдвига 5, блока памяти 7, БК 8, БС 9 и блока стробирования .10. Приведены табл.истинности, в соответствии с которыми выполнены преобразователь 6, БС 9 и БК 8. 2 ил, 22 табл. W X) 9

| Левин Л.С., Плоткин М.А | |||

| Цифровые системы передачи информации, М.:- Радио и связь, 1982, с.192, 195 | |||

| Система передачи дискретной информации | 1976 |

|

SU688082A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-07-15—Публикация

1984-12-18—Подача