§

(Л

с:

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодер кода 3В2 @ | 1984 |

|

SU1244803A1 |

| Кодер балансного кода 3B2Q | 1987 |

|

SU1531223A1 |

| Устройство кодовой синхронизации | 1985 |

|

SU1328941A1 |

| Устройство регистрации ошибок | 1985 |

|

SU1478346A1 |

| Система передачи дискретной информации | 1985 |

|

SU1262741A1 |

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Устройство для приема сигналов относительной фазовой телеграфии | 1983 |

|

SU1138954A1 |

Изобретение относится к электросвязи и может найти применение в цифровых системах передачи, организованных по оптико-волоконным и радиорелейным линиям связи. Целью изобретения является повышение помехоустойчивости кодера. Устройство содержит блок 1 синхронизации, формирователь 2 выходного сигнала, элемент НЕ 3, последовательный регистр 4, формирователь 5 синхросигнала кодовых групп, параллельный регистр 6, блок 7 преобразования кода, формирователь 8 тактовой частоты, элемент , 9 управления и элемент НЕ 10, 3 з.п. ф-лы, 4 ил., 8 табл.

со

10

11444964

Изобретение относится к электросвязи и может быть использовано- для передачи цифровой информации по волоконно-оптическим и радиорелейным линиям связи.

Цель изобретения - повышение по- мехоустойчивости кодера.

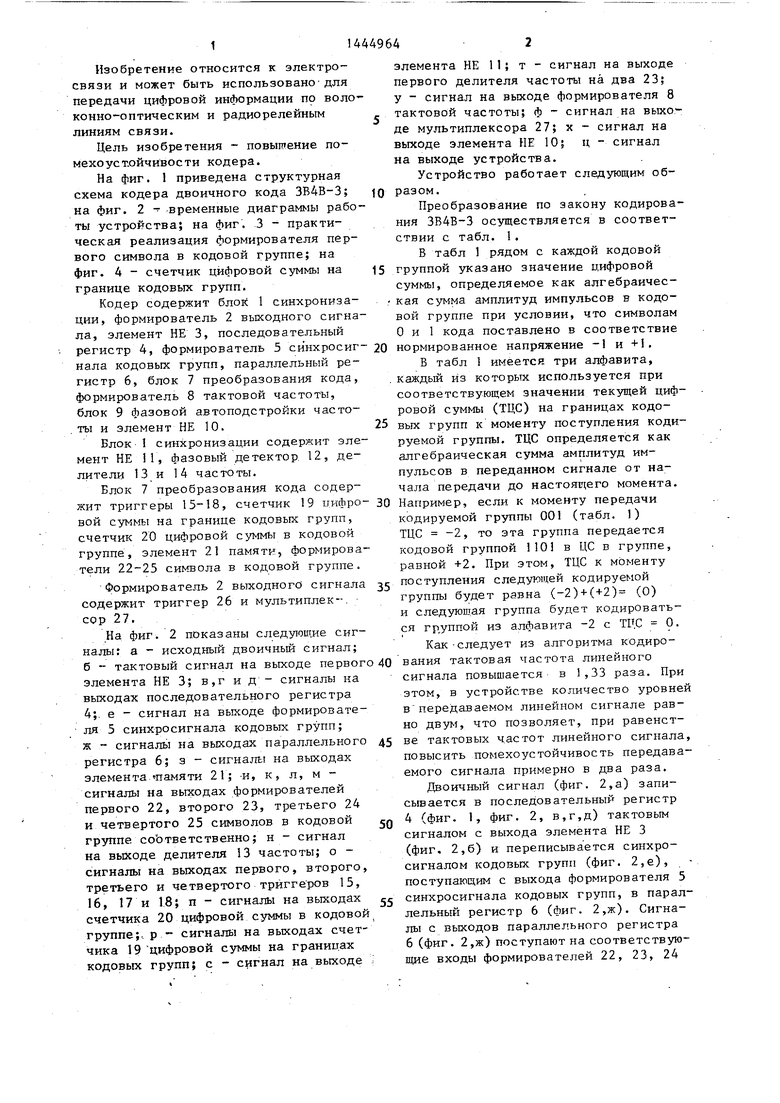

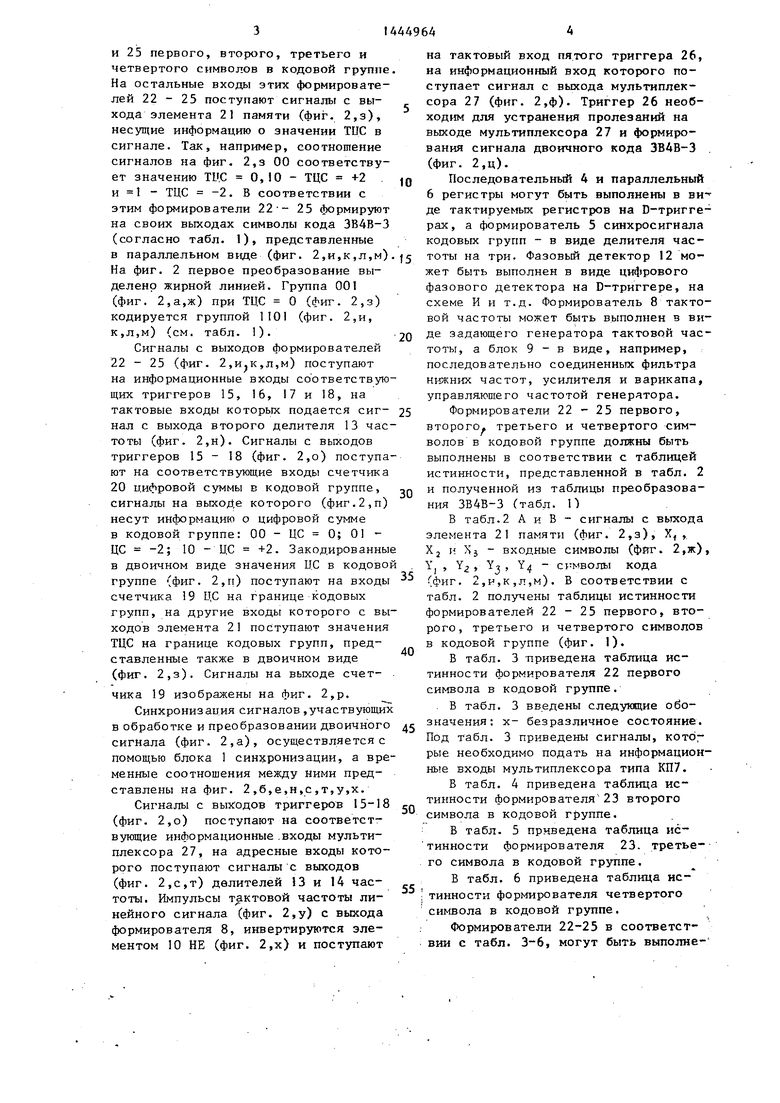

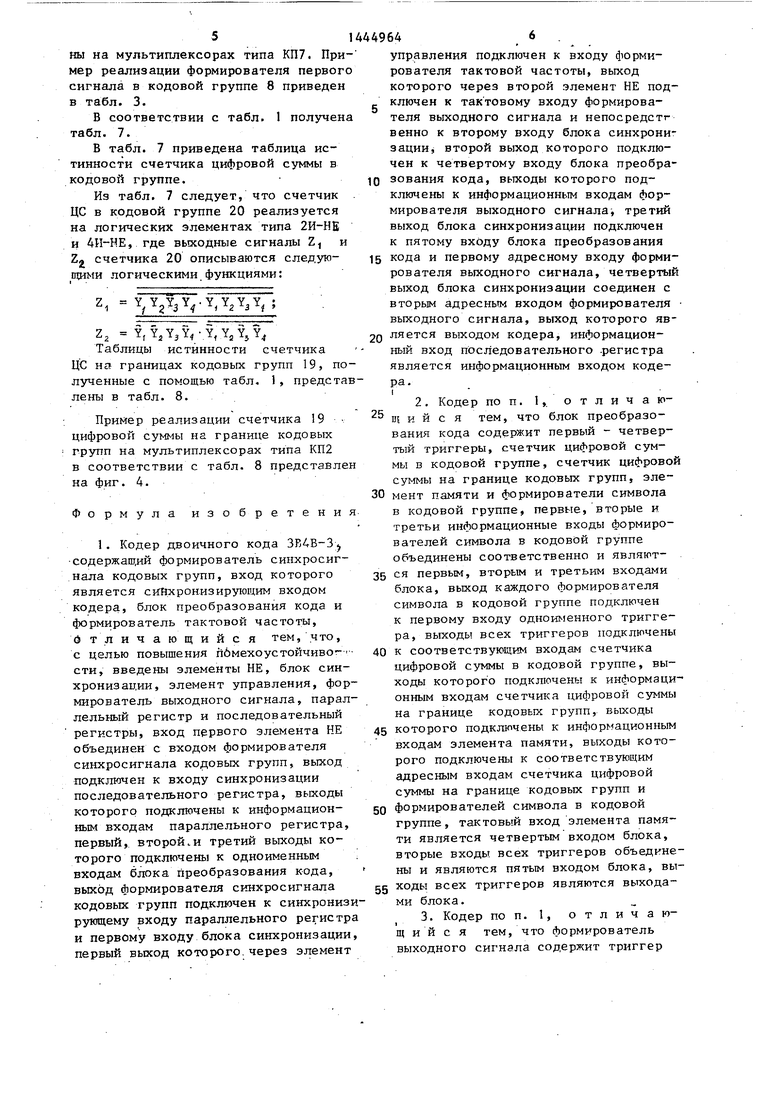

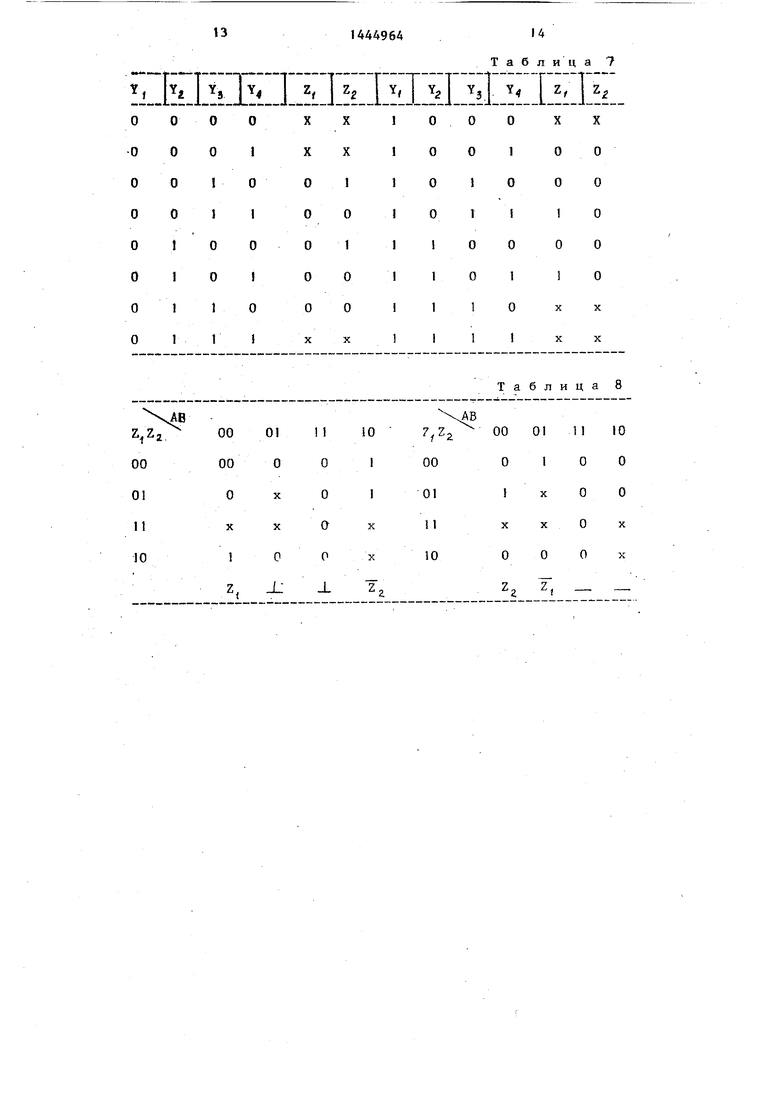

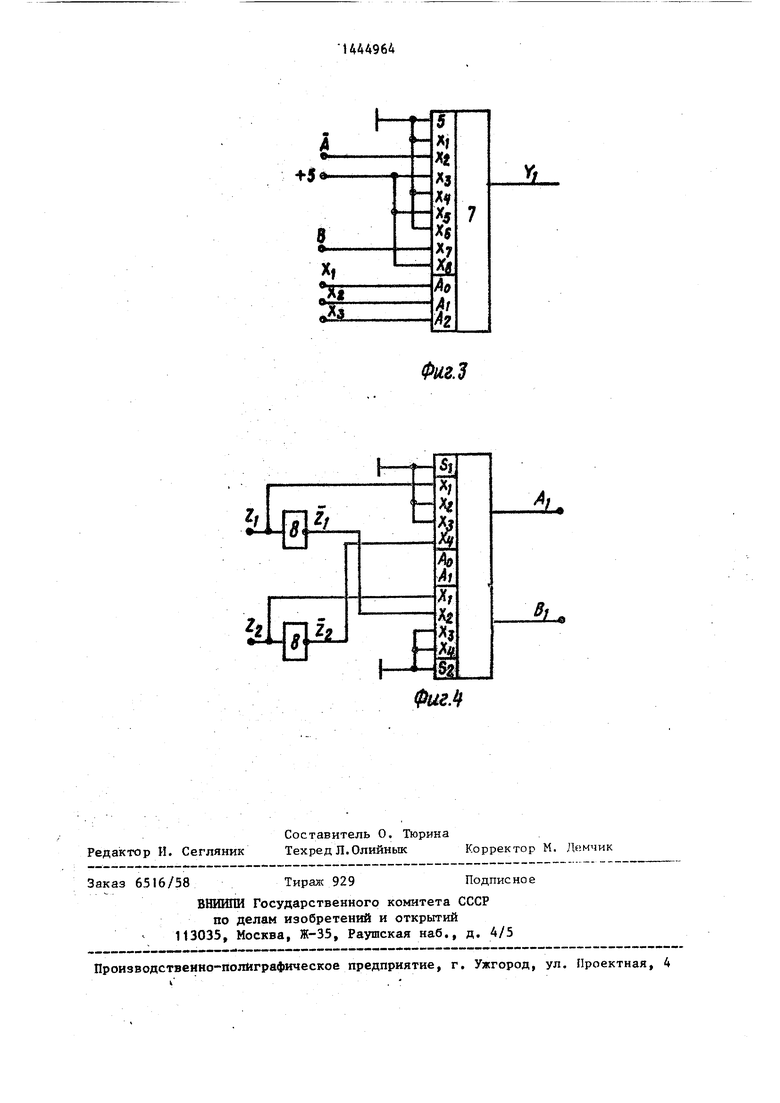

На фиг. 1 приведена структурная схема кодера двоичного кода ЗВ4В-3; на фиг. 2 - временные диаграммы работы устройства; на фиг. 3 - практическая реализация формирователя перого символа в кодовой группе; на иг. 4 - счетчик цифровой суммы на границе кодовых групп.

Кодер содержит блой 1 синхронизаии, формирователь 2 выходного сигнаа, элемент НЕ 3, последовательный регистр 4, формирователь 5 синхросигала кодовых групп, параллельный регистр 6, блок 7 преобразования кода, ормирователь 8 тактовой частоты, блок 9 фазовой автоподетройки часто- ты и элемент НЕ 10.

Блок 1 синхронизации содержит эле- ент НЕ 11, фазовый детектор 12, деители 13 и 14 частоты.

э п т д вы н

н с

15 гр

су к во но

к со ро вы ру ал пу ча

20

25

В табл имеется три алфавита, каждый из которых используется при соответствующем значении текущей ц ровой суммы (ТЦС) на границах кодо вых групп к моменту поступления ко руемой группы. ТЦС определяется ка алгебраическая сумма амплитуд импульсов в переданном сигнале от на чала передачи до настоящего момент

Блок 7 преобразования кода содержит триггеры 15-18, счетчик 19 цифре- 30 Например, если к моменту передачи вой суммы на границе кодовых групп, кодируемой группы 001 (табл. 1) счетчик 20 цифровой суммьг в кодовой группе, элемент 21 памяти, формирователи 22-25 символа в кодовой группе.

ТЦС -2, то эта группа передается кодовой группой 1101 в ЦС в группе равной +2. При этом, ТЦС к моменту поступления следующей кодируемой группы будет равна (-2)+(+2) (О) и следующая группа будет кодироват ся группой из алфавита -2 с Tl .C Как-следует из алгоритма кодир

Формирователь 2 выходного сигнала з5 содержит триггер 26 и мультиплек-. сор 27.

На фиг. 2 показаны следующие сигналы: а - исходный двоичньй сигнал; б - тактовый сигнал на выходе первого 40 вания тактовая частота линейного

ТЦС -2, то эта группа передаетс кодовой группой 1101 в ЦС в групп равной +2. При этом, ТЦС к момен поступления следующей кодируемой группы будет равна (-2)+(+2) (О и следующая группа будет кодирова ся группой из алфавита -2 с Tl .C Как-следует из алгоритма коди

элемента НЕ 3; в,г ид- сигналы на выходах последовательного регистра 4;, е - сигнал на выходе формирователя 5 синхросигнала кодовых групп; ж - сигналы на выходах параллельного регистра 6; з - сигналы на выходах элемента Памяти 21; -и, к, л, м - сигналы на выходах формирователей первого 22, второго 23, третьего 24 и четвертого 25 символов в кодовой группе cobтветственно; н - сигнал на выходе делителя 13 частоты; о - сигналы на выходах первого, второго, третьего и четвертого триггеров 15, 16, 17 и 18; п - сигналы на выходах счетчика 20 цифровой суммы в кодовой группе;., р - сигналы на выходах счетчика 19 цифровой суммы на границах кодовых групп; с - сигнал на выходе

элемента НЕ II; т - сигнал на выходе первого делителя частоты на два 23; у - сигнал на выходе формирователя 8 тактовой частоты; ф - сигнал на выходе мультиплексора 27; к - сигнал на выходе элемента НЕ 10; ц - сигнал на выходе устройства.

Устройство работает следующим образом.

Преобразование по закону кодирования ЗВ4Б-3 осуществляется в соответствии с табл. 1.

В табл 1 рядом с каждой кодовой группой указано значение цифровой

суммы, определяемое как алгебраичес- кая сумма амплитуд импульсов в кодовой группе при условии, что символам О и 1 кода поставлено в соответствие нормированное напряжение -1 и +1.

В табл имеется три алфавита, каждый из которых используется при соответствующем значении текущей цифровой суммы (ТЦС) на границах кодовых групп к моменту поступления кодируемой группы. ТЦС определяется как алгебраическая сумма амплитуд импульсов в переданном сигнале от начала передачи до настоящего момента.

Например, если к моменту передачи кодируемой группы 001 (табл. 1)

Например, если к моменту передачи кодируемой группы 001 (табл. 1)

вания тактовая частота линейного

ТЦС -2, то эта группа передается кодовой группой 1101 в ЦС в группе, равной +2. При этом, ТЦС к моменту поступления следующей кодируемой группы будет равна (-2)+(+2) (О) и следующая группа будет кодироваться группой из алфавита -2 с Tl .C 0. Как-следует из алгоритма кодиросигнала повышается в 1,33 раза. При этом, в устройстве количество уровней в передаваемом линейном сигнале равно двум, что позволяет, при равенстве тактовых частот линейного сигнала повысить помехоустойчивость передаваемого сигнала примерно в два раза.

Двоичный сигнал (фиг. 2,а) записывается в последовательный регистр 4 (фиг. 1, фиг. 2, в,г,д) тактовым сигналом с выхода элемента НЕ 3 (фиг. 2,6) и переписывается синхросигналом кодовых групп (фиг. 2,е), поступающим с выхода формирователя 5 синхросигнала кодовых групп, в параллельный регистр 6 (фиг. 2,ж). Сигналы с выходов параллельного регистра 6 (фиг. 2,ж) поступают на соответствующие входы формирователей 22, 23, 24

и 25 первого, второго, третьего и четвертого символов в кодовой группе На остальные входы этих формирователей 22 - 25 поступают сигналы с выхода элемента 21 памяти (фиг. 2,з), несуп(ие информацию о значении ТИС в сигнале. Так, например, соотношение сигналов на фиг. 2,з 00 соответствует значению ТЦС 0,10 - ТЦС +2 . и 1 - ТЦС -2. В соответствии с этим формирователи 22-- 25 формируют на своих выходах символы кода ЗВ4В-3 (согласно табл. 1), представленные в параллельном В1ще (фиг. 2,и,к,л,м) На фиг. 2 первое преобразование выделено жирной линией. Группа 001 (фиг. 2,а,ж) при ТЦС О (фиг. 2,з) кодируется группой 1101 (фиг. 2,и, к,л,м) (см. табл. 1).

Сигналы с выходов формирователей 22 - 25 (фиг. 2,,л,м) поступают на информационные входы соответствующих триггеров 15, 16, 17и18, на тактовые входы которых подается сиг- нал с выхода второго делителя 13 частоты (фиг. 2,н). Сигналы с выходов триггеров 15 - 18 (фиг. 2,о) поступают на соответствующие входы счетчика 20 цифровой суммы в кодовой группе, сигналы на выходе которого (фиг.2,п) несут информацию о цифровой сумме в кодовой группе: 00 - ЦС 0; 01 - ЦС -2; 10 - ЦС +2. Закодированные в двоичном виде значения ЦС в кодовой группе (фиг. 2,п) поступают на входы счетчика 19 ЦС на границе кодовых групп, на другие входы которого с выходов элемента 21 поступают значения

ТЦС на границе кодовых групп, представленные также в двоичном виде

(фиг. 2,з). Сигналы на выходе счетчика 19 изображены на фиг. 2,р.

Синхронизация сигналов,участвующих в обработке и преобразовании двоичного сигнала (фиг. 2,а), осуществляется с помощью блока 1 синхронизации, а временные соотношения между ними представлены на фиг. 2,б,е,и,с,т,у,X.

Сигналы с выходов триггеров 15-18 (фиг. 2,о) поступают на соответствующие информационные.входы мультиплексора 27, на адресные входы которого поступают сигналы с выходов (фиг. 2,с,т) делителей 53 и 14 частоты. Импульсы тактовой частоты линейного сигнала (фиг. 2,у) с выхода формирователя 8, инвертируются элементом 10 НЕ (фиг. 2,х) и поступают

0

j 0

5

0

5

0

0

5

на тактовый вход пятого триггера 26, на информационный вход которого поступает сигнал с выхода мультиплексора 27 (фиг. 2,ф). Триггер 26 необходим для устранения пролезаний на выходе мультиплексора 27 и формирования сигнала двоичного кода ЗВАВ-3 (фиг. 2,ц).

Последовательный 4 и параллельный 6 регистры могут быть выполнены в вн- де тактируемых регистров на D-тригге- рах, а формирователь 5 синхросигнала кодовых групп - в виде делителя частоты на три. Фазовый детектор 12 может быть выполнен в виде ци4 рового фазового детектора на D-триггере, на схеме И и т.д. Формирователь 8 тактовой частоты может быть выполнен в виде задающего генератора тактовой частоты, а блок 9 - в виде, например, последовательно соединенных фильтра нижних частот, усилителя и варикапа, управляющего частотой генератора.

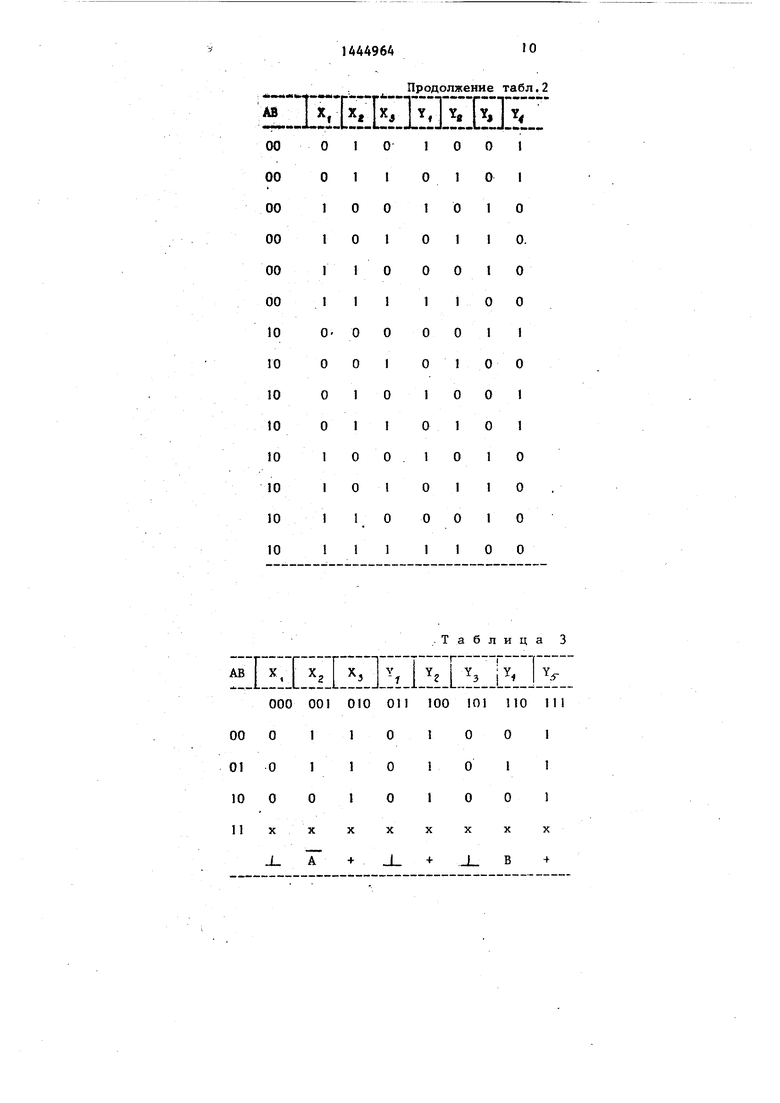

Формирователи 22-25 первого, второго, третьего и четвертого символов в кодовой группе должны быть выполнены в соответствии с таблицей истинности, представленной в табл. 2 и полученной из таблицы преобразования ЗВ4В-3 (табл. П

В табл.2 А и В - сигналы с выхода элемента 2 памяти (фиг. 2,з), X,, Xj и з - входные символы (фйг. 2,ж), YJ , Y , YJ, Y - символы кода (фиг. 2,и,к,л,м). В соответствии с табл. 2 получены таблицы истинности формирователей 22-25 первого, второго, третьего и четвертого символов в кодовой группе (фиг. 1).

В табл. 3 -приведена таблица истинности формирователя 22 первого символа в кодовой группе.

. В табл. 3 введены следующие обозначения: х- безразличное состояние. Под табл. 3 приведены сигналы, кото рые необходимо подать на информационные входы мультиплексора типа КП7.

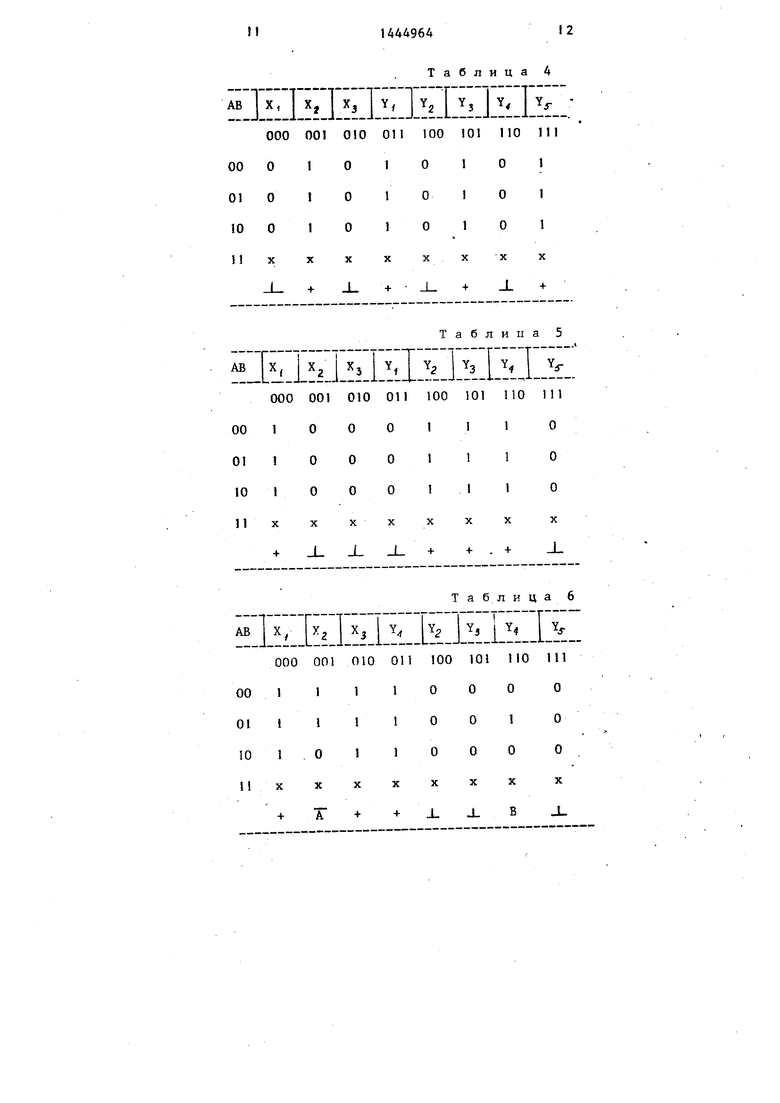

В табл. 4 приведена таблица истинности формирователя 23 второго символа в кодовой группе. : В табл. 5 приведена таблица ис- тинности формирователя 23. третьего символа в кодовой группе.

В табл. 6 приведена таблица нс- I тинности формирователя четвертого символа в кодовой группе.

Формирователи 22-25 в соответствии с табл. 3-6, могут быть выполнены на мультиплексорах типа КП7. Пример реализации формирователя первого сигнала в кодовой группе 8 приведен в табл. 3.

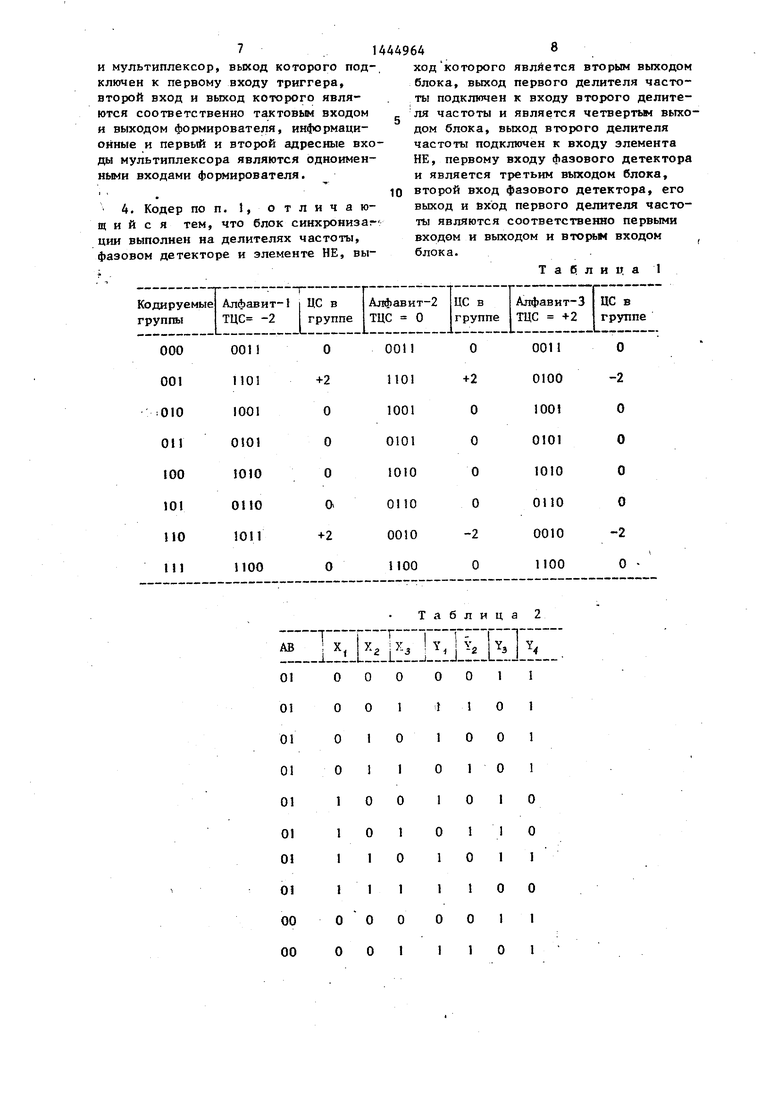

В соответствии с табл, 1 получена табл. 7.

В табл. 7 приведена таблица истинности счетчика цифровой суммы в кодовой группе.

Из табл. 7 следует, что счетчик ЦС в кодовой группе 20 реализуется на логических элементах типа 2И-НЕ И 4И-НЕ, где выходные сигналы Z Zjj счетчика 20 описываются следующими логическими.функциями:

и

/ Y,

. V V у V

Ij 12 3 t

Y, Y, Y Y, Yj Yj Y

2 Yf -2 З

Таблицы истинности

счетчика

ЦС на границах кодовых групп 19, полученные с помощью табл. 1, представлены в табл. 8.

Пример реализации счетчика 19 цифровой суммы на границе кодовых групп на мультиплексорах типа КП2 в соответствии с табл. 8 представлен на фиг. 4.

Формула изобретения

управления подключен к входу формирователя тактовой частоты, выход которого через второй элемент НЕ подключен к тактовому входу формирователя выходного сигнала и непосредстг венно к второму входу блока синхрони- зации.1 второй выход которого подключен к четвертому входу блока преобразования кода, выходы которого подключены к информационным входам формирователя выходного сигнала третий выход блока синхронизации подключен к пятому входу блока преобразования

кода и первому адресному входу формирователя выходного сигнала, четвертый выход блока синхронизации соединен с вторым адресным входом формирователя выходного сигнала, выход которого является выходом кодера, информационный вход последовательного .регистра является информационным входом кодера. I

5

2 , Кодер по п. 1,. отличаю5

0

щ и и с Я тем, что блок преобразования кода содержит первый - четвертый триггеры, счетчик цифровой суммы в кодовой группе, счетчик цифровой на границе кодовых групп, эле0 мент памяти и формирователи символа в кодовой группе, первые, вторые и третьи информационные входы формирователей символа в кодовой группе объединены соответственно и являются первым, вторым и третьим входами блока, выход каждого формирователя символа в кодовой группе подключен к первому входу одноименного триггера, выходы всех триггеров подключены к соответствующим входам счетчика цифровой суммы в кодовой группе, выходы которого подключены к информационным входам счетчика цифровой суммы на границе кодовых групп, выходы

5 которого подключены к информационным входам элемента памяти, выходы которого подключешл к соответствующим адресным входам счетчика цифровой суммы на границе кодовых групп и формирователей символа в кодовой группе, тактовы-й вход элемента памяти является четвертым входом блока, вторые входы всех триггеров объединены и являются пятым входом блока, выходы всех триггеров являются выходами блока.

0

5

и мультиплексор, выход которого под-ход которого является вторым выходом

ключей к первому входу триггера,блока, выход первого делителя частовторой вход и выход которого явля- . ты подключен к входу второго делите- ются соответственно тактовым входом ля частоты и является четвертьм выхои выходом формирователя, информаци-дом блока, выход второго делителя

онные и первый и второй адресные вхо- частоты подключен к входу элемента ды мультиплексора являются одноимен-НЕ, первому входу фазового детектора

ными входами формирователя. и является третьим выходом блока,

.,10 второй вход фазового детектора, его

Т а б. л и ц а 1

144496АJO

Продолжение табл.2

144А96412

Таблица А

.l. 001 010 on 100 101 110 111

00о 1 о 1 о 1 о 1

01о 1 о 1 о 1 о 1

10о 1 о 1 о 1 о 1

11XXXXXXXX

L +

ТаблииаЗ

.

000001010on100 101по111

001ооо1 11о

011ооо1 11о 10 1ооо111о

ПхXXXXXXX

-f +.+ J

Таблица 6

..

000001010on100 101 no111

0011110000

01I1110 0 10 10 10110 0 00 llxXXXX X XX

+ Г+ -t-j. j

и

К Л

м и

о

п

2;

- -

Лг 5г

/77 J 11 II Т- t U-J L-J I-J t1 I-I

У .. x LTijnLrxjnjT ruajrxrurL

- 1 О

- ис - -г

Фиг. г

Фиг. З

ФигЛ

| Мурадян А,Г | |||

| и Гинзбург С.А | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ приготовления строительного изолирующего материала | 1923 |

|

SU137A1 |

| Система передачи цифровой информациибииМпульСНыМ СигНАлОМ | 1976 |

|

SU815953A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-12-15—Публикация

1986-04-01—Подача