1

(21)4292889/24-24

(22)03.08.87

(46) 23.12.89. Бнш. № 47 (72) И.М.Котиков, В.Э.Черный, З.А.Вайс и П.Г.Каплунов

(53)621.394.14 (088.8)

(56)Авторское свидетельство СССР 688082, кл. К 04 L 5/00, 1976.

Авторское свидетельство СССР 1244803, кл. Н 04 L 5/00, 1984.

(54)КОДЕР БАЛАНСНОГО КОДА 332 Q

(57)Изобретение относится к электросвязи и может найти применение в цифровых системах передачи информации. Цель изобретения - повьппение быстродействия за счет одновременного преобразования основания кода и контроля

В

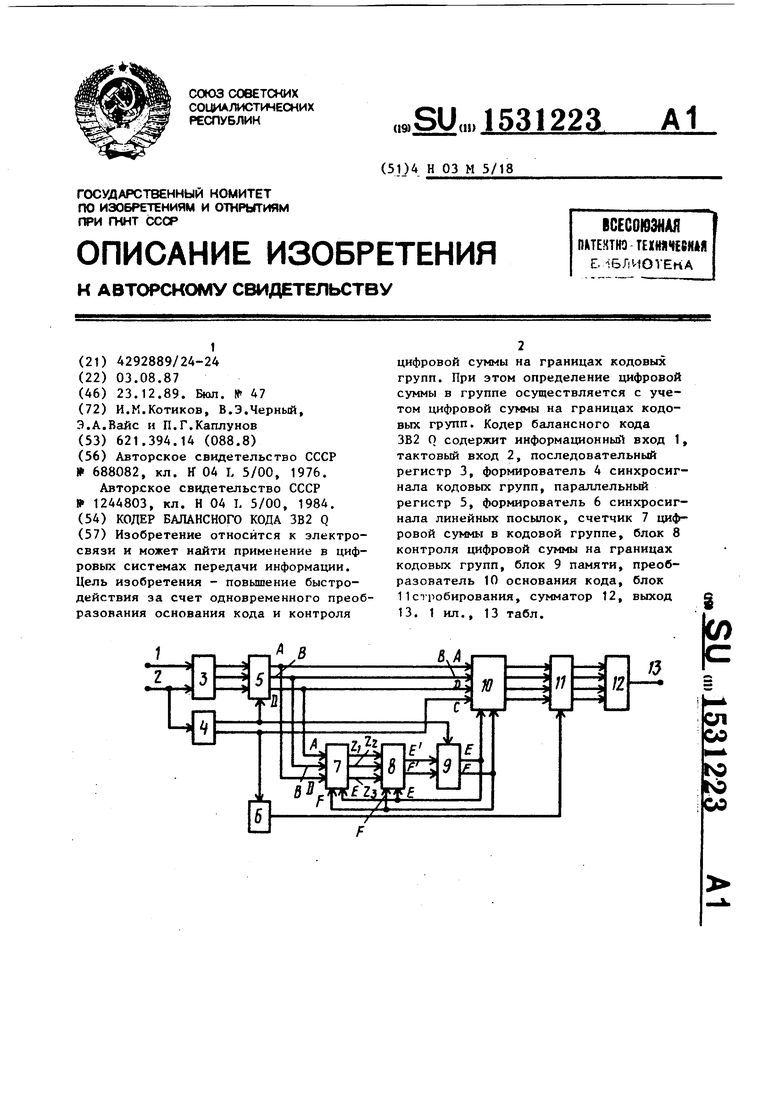

цифровой суммы на границах кодовых групп. При этом определение цифровой суммы в группе осуществляется с учетом цифровой суммы на границах кодовых групп. Кодер балансного кода ЗВ2 О содержит информационный вход 1, тактовый вход 2, последовательный регистр 3, формирователь 4 синхросигнала кодовых групп, параллельный регистр 5, формирователь 6 синхросигнала линейных посылок, счетчик 7 цифровой суммы в кодовой группе, блок 8 контроля цифровой суммы на границах кодовых групп, блок 9 памяти, преобразователь 10 основания кода, блок 11стробирования, сумматор 12, выход 13. 1 ил., 13 табл.

Ai

/5

Изобретение относится к электросзи и может быть использовано в цифровых системах передачи.

Целью изобретения является повышение, быстродействия за счет одновременного преобразования основания кода и контроля цифровой суммы на границах кодовых групп.

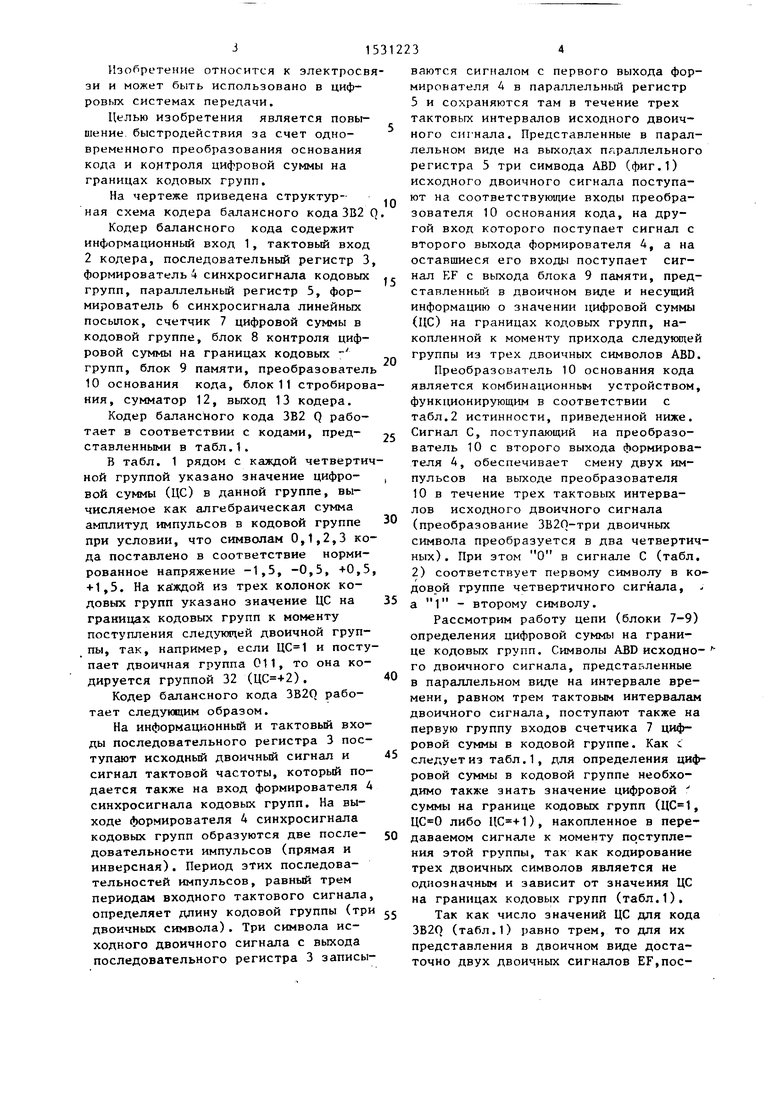

На чертеже приведена структурная схема кодера балансного кода ЗВ2

Кодер балансного кода содержит информационный вход 1, тактовый вхо 2 кодера, последовательный регистр формирователь 4 синхросигнала кодовы групп, параллельный регистр 5, формирователь 6 синхросигнала линейных посылок, счетчик 7 цифровой суммы в кодовой группе, блок 8 контроля цифровой суммы на границах кодовых - групп, блок 9 памяти, преобразовате 10 основания кода, блок 11 стробиро ния, сумматор 12, выход 13 кодера.

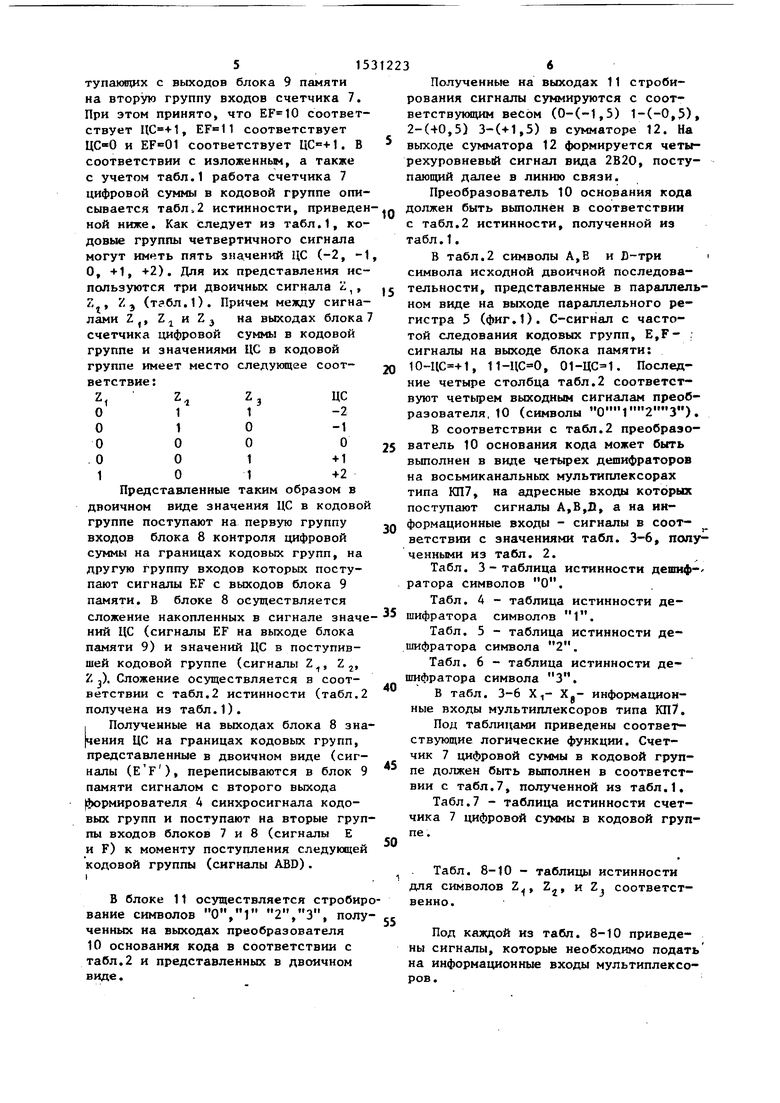

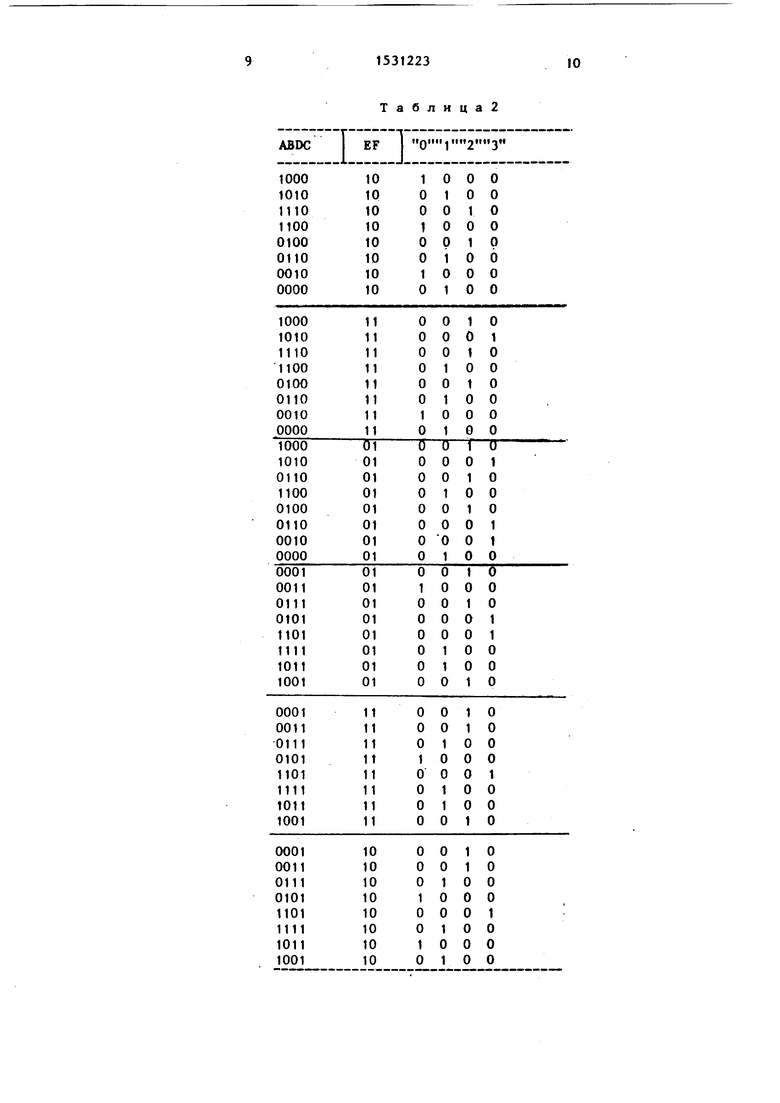

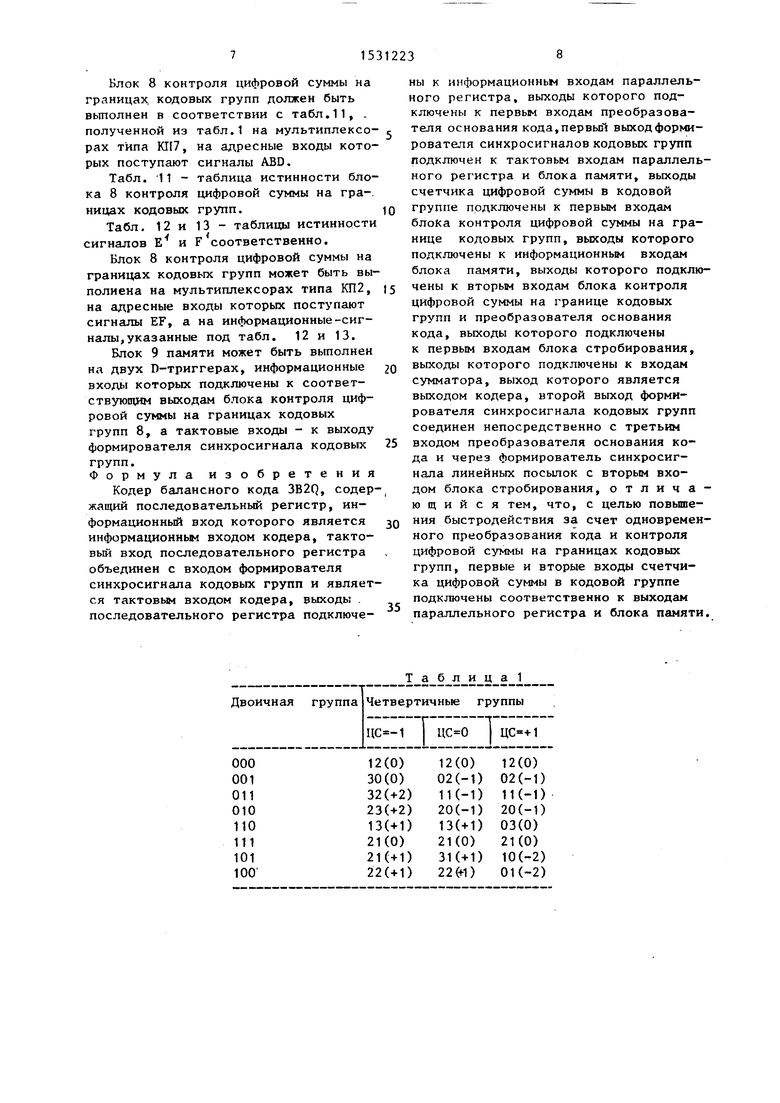

Кодер баланс 1ого кода ЗВ2 Q работает в соответствии с кодами, представленными в табл.1.

В табл. 1 рядом с каждой четвертной группой указано значение цифровой суммы (ЦС) в данной группе, вычисляемое как алгебраическая сумма амплитуд импульсов в кодовой группе при условии, что символам 0,1,2,3 кда поставлено в соответствие нормированное напряжение -1,5, -0,5, 0, ь1,5. На кагждой из трех колонок кодовых групп указано значение ЦС на границах кодовых групп к моменту поступления следующей двоичной группы, так, например, если и постпает двоичная группа 011, то она кодируется группой 32 (),

Кодер балансного кода ЗВ20 работает следующим образом.

На информационный и тактовый входы последовательного регистра 3 поступают исходный двоичный сигнал и сигнал тактовой частоты, который подается также на вход формирователя синхросигнала кодовых групп. На выходе формирователя 4 синхросигнала кодовых групп образуются две последовательности импульсов (прямая и инверсная). Период этих последовательностей импульсов, равный трем периодам входного тактового сигнала определяет длину кодовой группы (тр двоичных символа). Три символа исходного двоичного сигнала с выхода последовательного регистра 3 заттисы

0

5

0

5

0

5

0

5

0

ваются сигналом с первого выхода формирователя Д в параллельный регистр 5 и сохраняются там в течение трех тактовых интервалов исходного двоичного сигнала. Представленные в параллельном виде на выходах параллельного регистра 5 три симвода ABD (фиг.1) исходного двоичного сигнала поступают на соответствующие входы преобразователя 10 основания кода, на другой вход которого поступает сигнал с второго выхода формирователя 4, а на оставшиеся его входы поступает сигнал EF с выхода блока 9 памяти, представленный в двоичном виде и несущий информацию о значении цифровой суммы (ЦС) на границах кодовых групп, накопленной к моменту прихода следующей группы из трех двоичных символов ABD.

Преобразователь 10 основания кода является комбинационным устройством, функционирующим в соответствии с табл.2 истинности, приведенной ниже. Сигнал С, поступающий на преобразователь 10 с второго выхода формирователя 4, обеспечивает смену двух импульсов на выходе преобразователя 10 в течение трех тактовых интервалов исходного двоичного сигнала (преобразование ЗВ20-три двоичных символа преобразуется в два четвертичных) . При этом О в сигнале С (табл. 2) соответствует первому символу в кодовой группе четвертичного сигнала, а 1 - второму символу.

Рассмотрим работу цепи (блоки 7-9) определения цифровой суммы на границе кодовых групп. Символы ABD исходно- го двоичного сигнала, представленные в параллельном виде на интервале времени, равном трем тактовым интервалам двоичного сигнала, поступают также на первую группу входов счетчика 7 цифровой суммы в кодовой группе. Как с следует из табл.1, для определения цифровой суммы в кодовой группе необходимо также знать значение цифровой : суммы на границе кодовых групп (, либо ), накопленное в передаваемом сигнале к моменту прступле- ния этой группы, так как кодирование трех двоичных символов является не однозначным и зависит от значения ЦС на границах кодовых групп (табл.1).

Так как число значений ЦС для кода 3B2Q (табл.1) равно трем, то для их представления в двоичном виде достаточно двух двоичных сигналов EF,nocтупакнцих с выходов блока 9 памяти на вторую группу входов счетчика 7. При этом принято, что соответствует , соответствует ЦС-0 и соответствует . В соответствии с иэложенньм, а также с учетом табл.1 работа счетчика 7 цифровой суммы в кодовой группе опиПолученные на выходах 11 строби- рования сигналы суммируются с соот- ветствуюощм весом (0-(-1,5) 1-(-0,5) 2-(40,5) 3-(-И,5) в сумматоре 12. На выходе сумматора 12 формируется четырехуровневый сигнал вида 2В20, поступающий далее в линию связи.

Преобразователь 10 основания кода

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодер кода 3В2 @ | 1984 |

|

SU1244803A1 |

| Кодер двоичного кода 3В4В-3 | 1986 |

|

SU1444964A1 |

| Устройство регистрации ошибок | 1985 |

|

SU1478346A1 |

| Система передачи дискретной информации | 1985 |

|

SU1262741A1 |

| Устройство кодовой синхронизации | 1985 |

|

SU1328941A1 |

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| Преобразователь последовательного кода в параллельный | 1989 |

|

SU1795557A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Преобразователь двоичного кода в трехпозиционный код | 1989 |

|

SU1633499A1 |

Изобретение относится к электросвязи и может найти применение в цифровых системах передачи информации. Цель изобретения - повышение быстродействия за счет одновременного преобразования основания кода и контроля цифровой суммы на границах кодовых групп. При этом определение цифровой суммы в группе осуществляется с учетом цифровой суммы на границах кодовых групп. Кодер балансного кода 3В2 Q содержит информационный вход 1, тактовый вход 2, последовательный регистр 3, формирователь 4 синхросигнала кодовых групп, параллельный регистр 5, формирователь 6 синхросигнала линейных посылок, счетчик 7 цифровой суммы в кодовой группе, блок 8 контроля цифровой суммы на границах кодовых групп, блок 9 памяти, преобразователь 10 основания кода, блок 11 стробирования, сумматор 12, выход 13. 13 табл., 1 ил.

сывается табл.2 истинности, приведен-.g должен быть выполнен в соответствии

ной ниже. Как следует из табл.1, кодовые группы четвертичного сигнала могут иметь пять значений ЦС (-2, -1, О, -i-l, +2). Для их представления используются три двоичных сигнала L,, Z , /С, (табл.1). Причем между сигналами Z J, Z и Z 3 на выходах блока 7 счетчика цифровой суммы в кодовой группе и значениями ЦС в кодовой группе имеет место следующее соответствие:

с табл.2 истинности, полученной из табл.1.

В табл.2 символы А,В и D-три символа исходной двоичной последова J5 тельности, представленные в параллел ном виде на выходе параллельного ре гистра 5 (фиг.1). С-сигнал с частотой следования кодовых групп, E,F- сигналы на выходе блока пг1мяти: 20 10-ЦС +1, 11-ЦС 0, 01-ЦС 1. Послед ние четыре столбца табл.2 соответствуют четьфем выходным сигналам прео разователя, 10 (символы

1 1 О О

о

1 о о 1 1

ЦС -2

« 1

О

+ 1

-(2

Представленные таким образом в двоичном виде значения ЦС в кодовой группе поступают на первую группу входов блока 8 контроля цифровой суммы на границах кодовых групп, на другую группу входов которых поступают сигналы EF с выходов блока 9 памяти. В блоке 8 осуществляется сложение накопленных в сигнале значе НИИ ЦС (сигналы EF на выходе блока памяти 9) и значений ЦС в поступившей кодовой группе (сигналы Z , Z j, Z р. Сложение осуществляется в соответствии с табл.2 истинности (табл.2

получена из табл.1).

I Полученные на выходах блока 8 зна- чения ЦС на границах кодовых групп, представленные в двоичном виде (сигналы (E F ), переписываются в блок 9 памяти сигналом с второго выхода формирователя 4 синхросигнала кодовых групп и поступают на вторые группы входов блоков 7 и 8 (сигналы Е и F) к моменту поступления следующей кодовой группы (сигналы ABD).

В блоке 11 осуществляется стробироIIQll fill) «loll oil

вание символов

полученных на выходах преобразователя 10 основания кода в соответствии с табл.2 и представленных в двоичном виде.

.g должен быть выполнен в соответствии

с табл.2 истинности, полученной из табл.1.

В табл.2 символы А,В и D-три i символа исходной двоичной последова- J5 тельности, представленные в параллельном виде на выходе параллельного регистра 5 (фиг.1). С-сигнал с частотой следования кодовых групп, E,F- . сигналы на выходе блока пг1мяти: 20 10-ЦС +1, 11-ЦС 0, 01-ЦС 1. Последние четыре столбца табл.2 соответствуют четьфем выходным сигналам преобразователя, 10 (символы ).

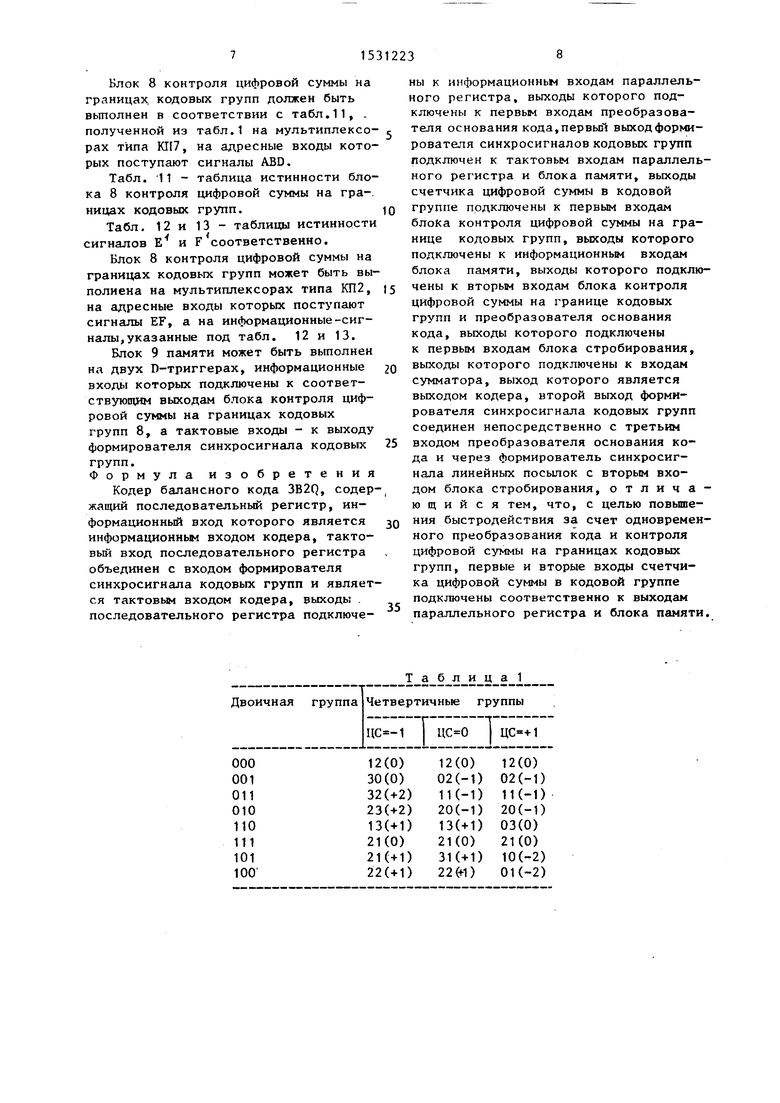

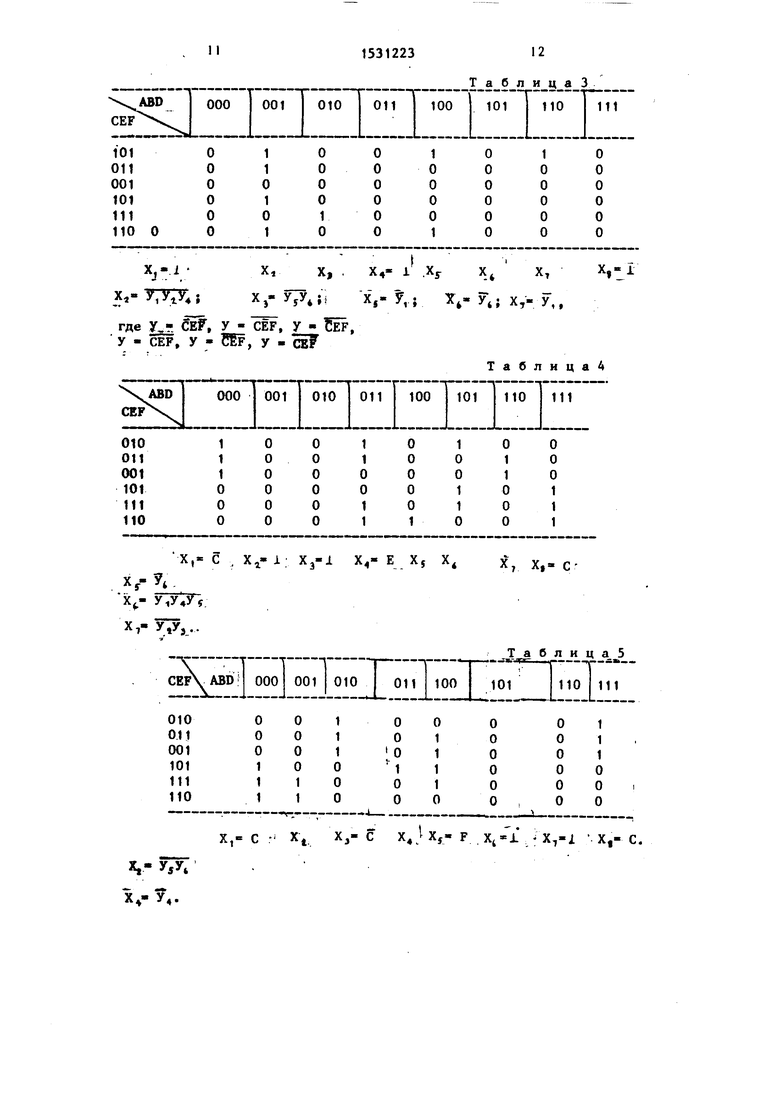

В соответствии с табл.2 преобразо- 25 ватель 10 основания кода может быть вьтолнен в виде четырех дешифраторов на восьмиканапьных мультиплексорах типа КП7, на адресные входы которых поступают сигналы А,В,Л, а на информационные входы - сигналы в соответствии с значениями табл. 3-6, полученными из табл. 2.

Табл. 3 - таблица истинности депшф- ратора символов О.

Табл. 4 - таблица истинности де- 35 шифратора символов 1.

Табл. 5 - таблица истинности дешифратора символа 2.

Табл. 6 - таблица истинности дешифратора символа 3.

В табл. 3-6 X,- Xj- информационные входы мультиплексоров типа КП7.

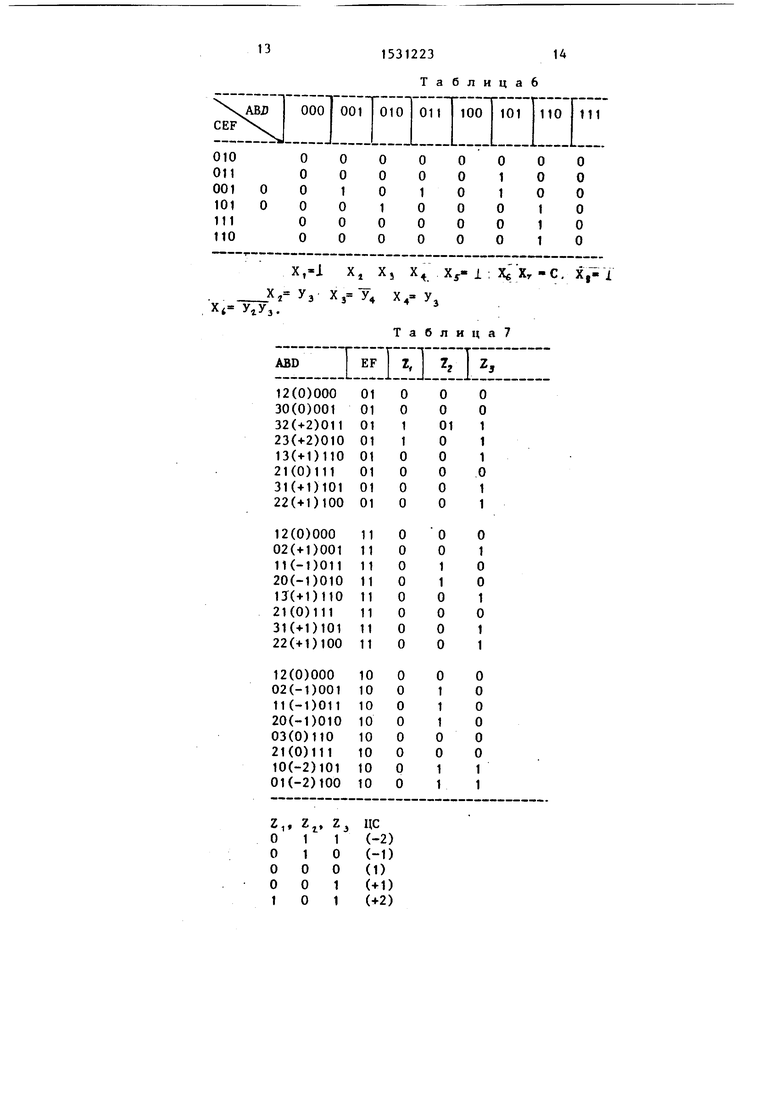

Под таблицами приведены соответствующие логические функции. Счетчик 7 цифровой суммы в кодовой группе должен быть выполнен в соответствии с табл.7, полученной из табл.1,

Табл.7 - таблица истинности счетчика 7 цифровой суммы в кодовой группе.

30

40

45

50

Табл. 8-10 - таблицы истинности

ДЛЯ символов Z венно.

1

и Z, соответст

Под казедой из табл. 8-10 приведены сигналы, которые необходимо подать на информационные входы мультиплексоров.

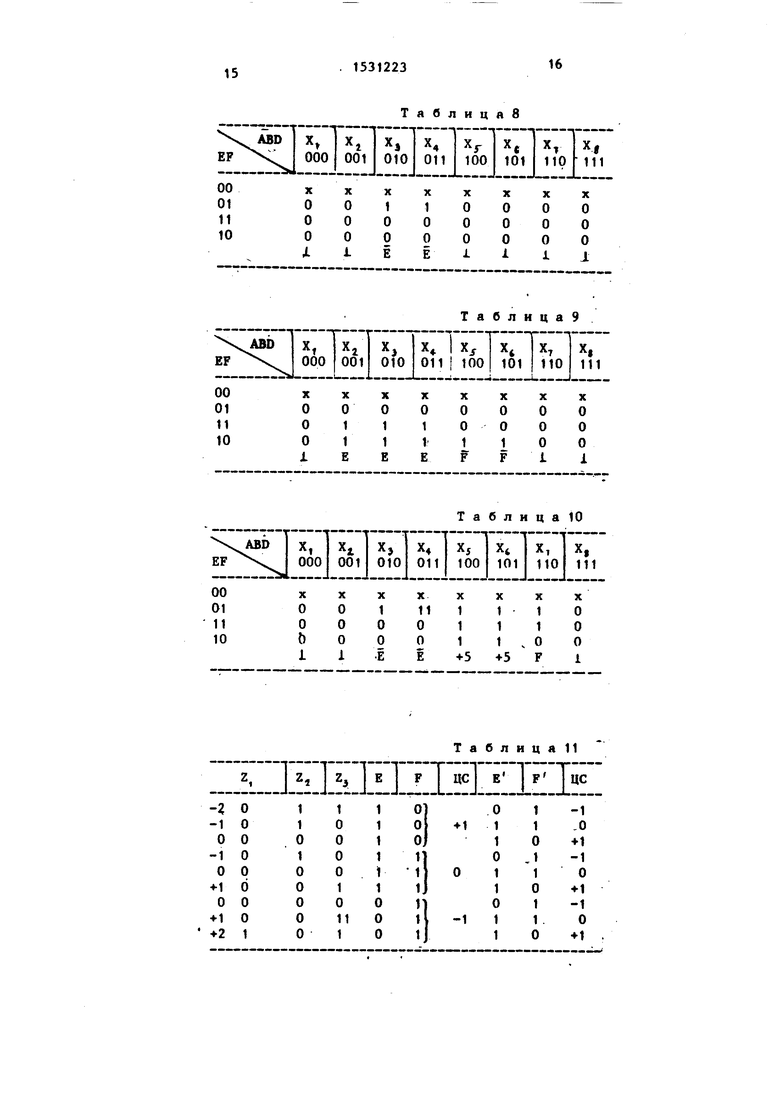

Блок 8 контроля цифровой суммы на границах, кодовых групп должен быть вьтолнен в соответствии с табл.11, . полученной из табл.1 на мультиплексо- pax типа , на адресные входы которых поступают сигналы ABD.

Табл. 11 - таблица истинности блока 8 контроля цифровой суммы на гра-. ницах кодовых групп.

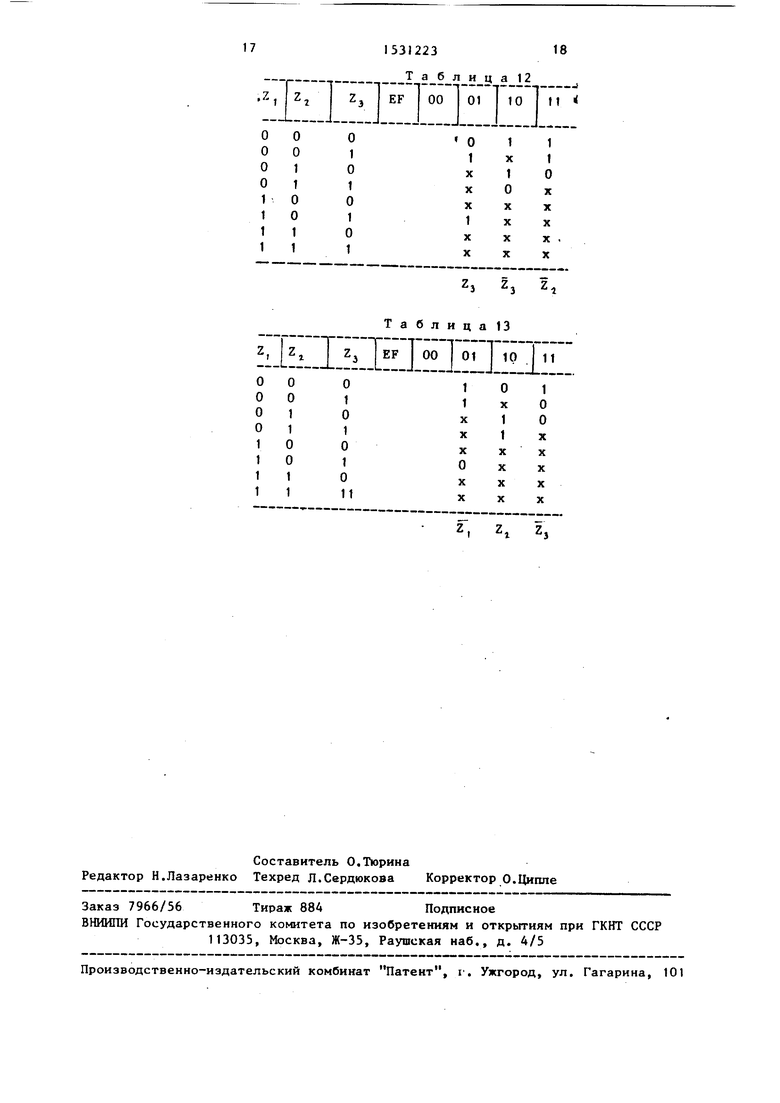

Табл. 12 и 13 - таблицы истинности сигналов Е и F соответственно.

Блок 8 контроля цифровой суммы на границах кодовых групп может быть выполнена на мультиплексорах типа КП2, на адресные входы которых поступают сигналы EF, а на информационные-сигналы, указанные под табл. 12 и 13.

Блок 9 памяти может быть выполнен на двух D-триггерах, информационные входы которых подключены к соответствующим выходам блока контроля цифровой суммы на границах кодовых групп 8, а тактовые входы - к выходу формирователя синхросигнала кодовых групп. Формула изобретения

Кодер балансного кода 3B2Q, содержащий последовательный регистр, информационный вход которого является информационным входом кодера, тактовый вход последовательного регистра объединен с входом формирователя синхросигнала кодовых групп и является тактовым входом кодера, выходы . последовательного регистра подключе

ны к информационные входам параллельного регистра, выходы которого подключены к первым входам преобразователя основания кода,первьп выход формирователя синхросигналов кодовых групп подключен к тактовым входам параллельного регистра и блока памяти, выходы счетчика цифровой суммы в кодовой группе подключены к первым входам блока контроля цифровой суммы на границе кодовых групп, выходы которого подключены к информационным входам блока памяти, выходы которого подключены к вторым входам блока контроля цифровой суммы на границе кодовых групп и преобразователя основания кода, выходы которого подключены к первым входам блока стробирования, выходы которого подключены к входам сумматора, выход которого является выходом кодера, второй выход формирователя синхросигнала кодовых групп соединен непосредственно с третьим входом преобразователя основания кода и через формирователь синхросигнала линейных посылок с вторым входом блока стробирования, отличающийся тем, что, с целью повышения быстродействия за счет одновременного преобразования кода и контроля цифровой суммы на границах кодовых групп, первые и вторые входы счетчика цифровой суммы в кодовой группе подключены соответственно к выходгш параллельного регистра и блока памяти.

Т а б л и ц а 1

Та6лица2

001

010

О О О О 1 О

J-f

Х,- ;

X,X,

X,-

где У,г. CEf, у - CEF, У - , У - СЕР, У - 15ЕР, у - СЕ

001

010

О О О О

о о

о о о о о о

X,- с

Xr-7i

Хг J. Xj-I

х, с

X,- с Х) Xj- F

- УзУ

,.

Таблица 3

100

I

101

110

111

1 О О О О

1

о о о о о о

1 о о о о о

о о о о о о

х

XT

X,- у,.

ТаблицаА

о о о о о 1

1 о о 1 1 о

о 1 1

о о о

о о о 1 1 1

Е X

5 X,

X, X,

Таблица. 5

;.

110 111

,-1 X,- с.

ABD

CEF

000 001

0 0

0 0 0 0 0 0

0 0

1

0 0 0

X,-I Xj X, X 1 ; Xg Xr -C, X,-T

АБО

IiniLlO

Таблицаб

oil

100

101

110

111

0 0

1

0 0 0

0 0 0 0 0 0

0

1 1

0 0 0

0 0 0

1 1 1

0 0 0 0 0 0

Таблица

ТаблицйЗ

Т а б л и ц а 11

Авторы

Даты

1989-12-23—Публикация

1987-08-03—Подача