1 1

Изобретение относится к контроль но-измерительной технике и может быть использовано для контроля области работоспособности электронных блоков при изменении напряжения питания

Целью изобретения является уменьшение вероятности выхода из строя контролируемого блока при испытании и сокращение времени испытаний, что достигается сокращенным перебором комбинаций испытательных сигналов, при которых произошло допустимое число сбоев или отказов, и дальнейшим исключением их из последовательности испытательных напряжений.

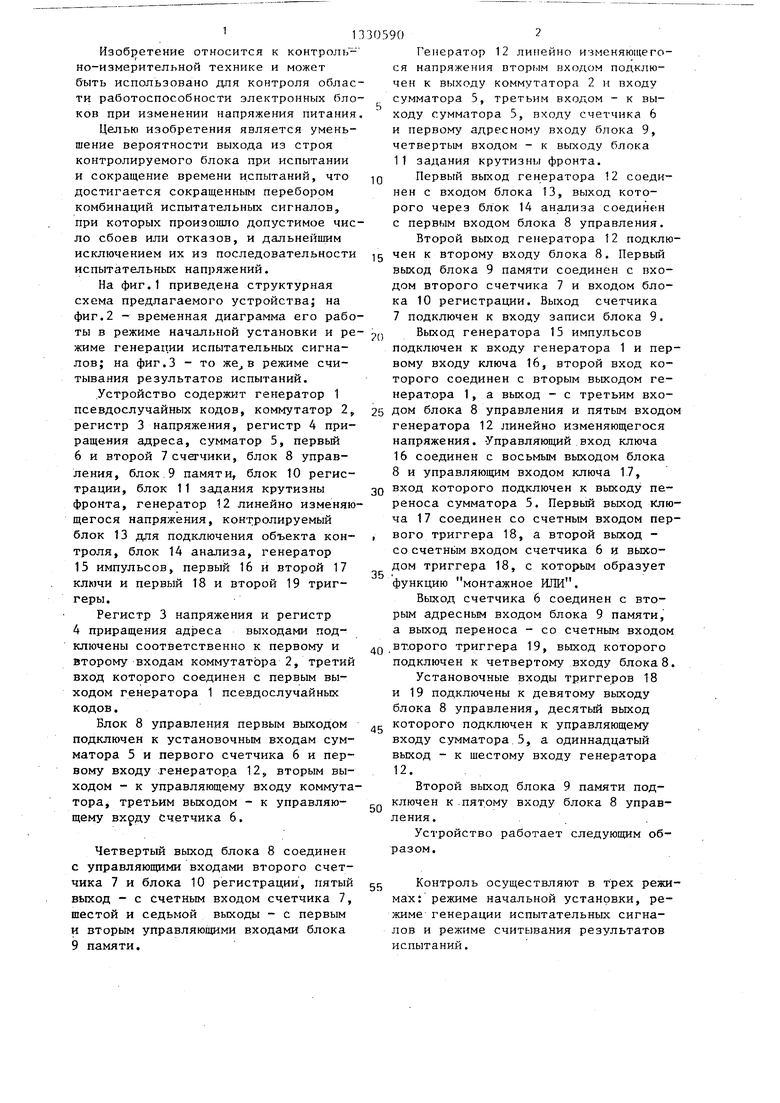

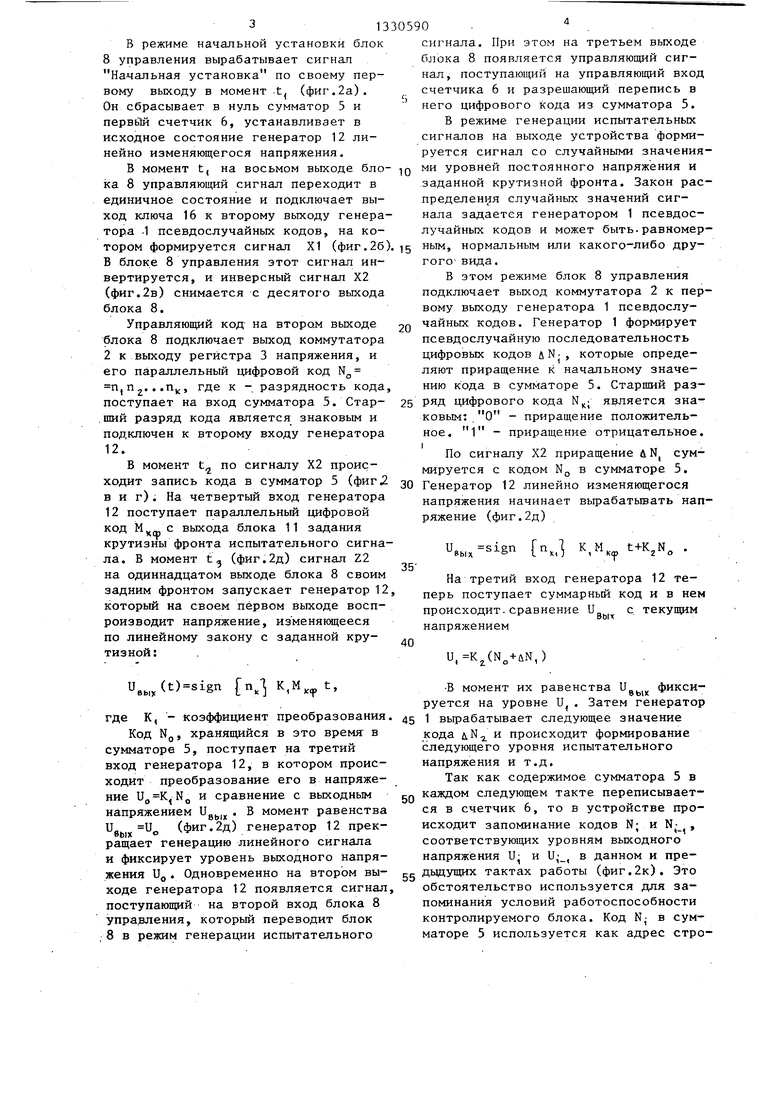

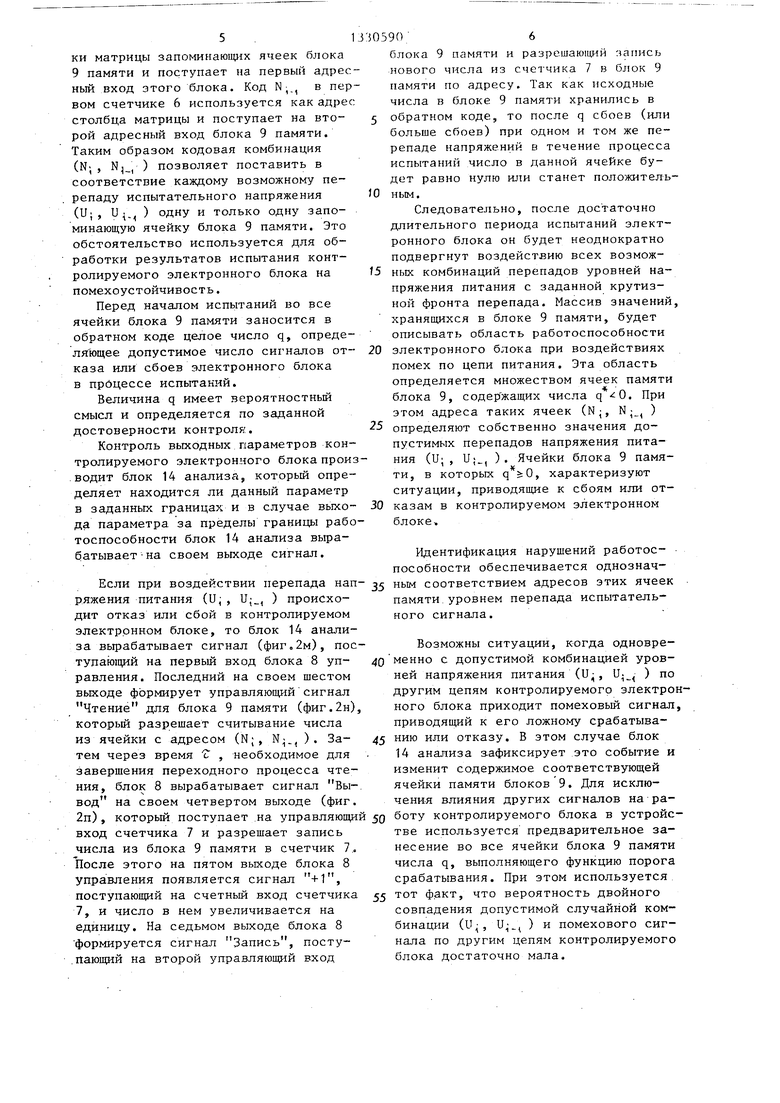

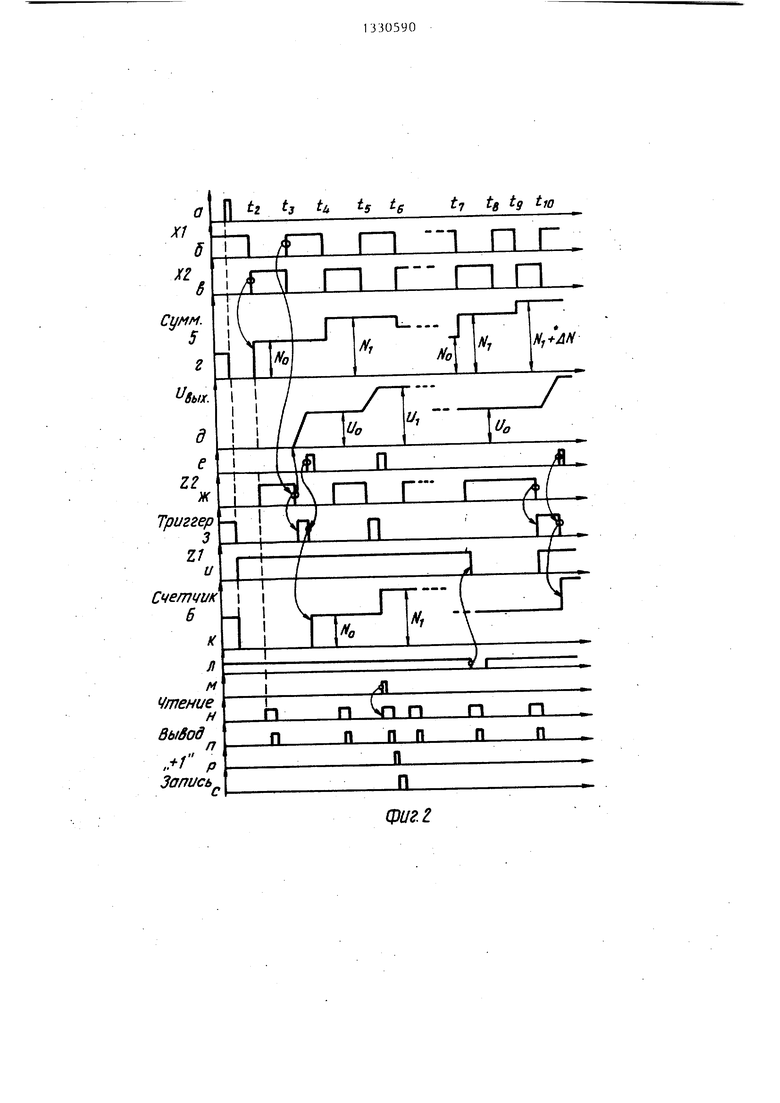

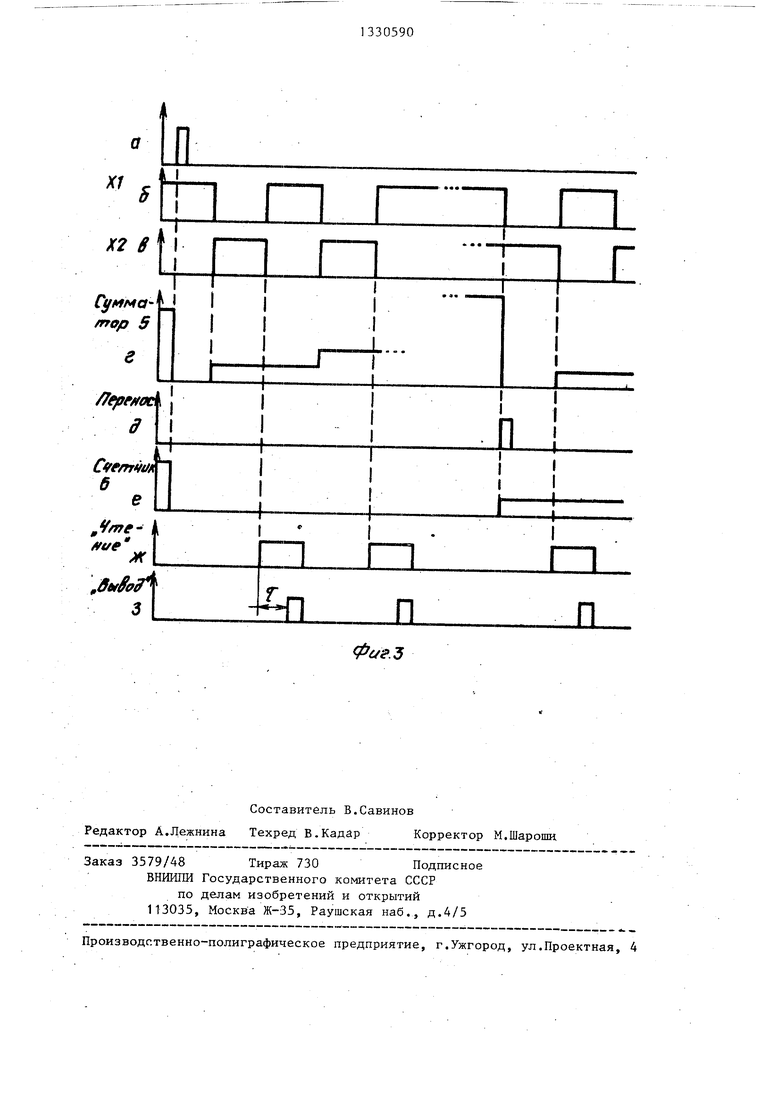

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 - временная диаграмма его работы в режиме начальной установки и режиме генерации испытательных сигналов; на фиг.З - то режиме считывания результатов испытаний.

.Устройство содержит генератор 1 псевдослучайных кодов, коммутатор 2, регистр 3 напряжения, регистр 4 приращения адреса, сумматор 5, первый 6 и второй 7 счетчики, блок 8 управления, блок 9 памяти, блок 10 регистрации, блок 11 задания крутизны фронта, генератор 12 линейно изменяющегося напряжения, контролируемый блок 13 для подключения объекта контроля, блок 14 анализа, генератор 15 импульсов, первый 16 и второй 17 ключи и первый 18 и второй 19 триггеры.

Регистр 3 напряжения и регистр 4 приращения адреса выходами подключены соответственно к первому и второму входам коммутатора 2, третий вход которого соединен с первым выходом генератора 1 псевдослучайных кодов.

Блок 8 управления первым выходом подключен к установочным входам сумматора 5 и первого счетчика 6 и первому входу .генератора 12, вторым выходом - к управляющему входу коммутатора, третьим выходом - к управляющему вхрду счетчика 6.

Четвертый выход блока 8 соединен с управляющими входами второго счетчика 7 и блока 10 регистрации, пятый выход - с счетным входом счетчика 7, шестой и седьмой выходы - с первым и вторым управляющими входами блока 9 памяти.

305902

Генератор 12 линейно изменяющегося напряжения втормм входом подключен к выходу коммутатора 2 и входу сумматора 5, третьим входом - к вы ходу сумматора 5, входу счетчика 6 и первому адресному входу блока 9, четвертым входом - к выходу блока 11 задания крутизны фронта. ig Первый выход генератора 12 соединен с входом блока 13, выход которого через блок 14 анализа соединен

с первым входом блока 8 управления.

Второй выход генератора 12 подклю- 15 чен к второму входу блока 8. Первый выход блока 9 памяти соединен с входом второго счетчика 7 и входом блока 10 регистрации. Выход счетчика

7подключен к входу записи блока 9.

20 Выход генератора 15 импульсов

подключен к входу генератора 1 и первому входу ключа 16, второй вход которого соединен с вторым выходом ге- нерат.ора 1, а выход - с третьим вхо- 25 дом блока 8 управления и пятым входом генератора 12 линейно изменяющегося напряжения. -Управляющий вход ключа 16 соединен с восьмым выходом блока

8и управляющим входом ключа 17,

3Q вход которого подключен к выходу переноса сумматора 5. Первый вькод Ключа 17 соединен со счетным входом пер, вого триггера 18, а второй выход - со счетным входом счетчика 6 и выходом триггера 18, с которым образует функцию монтажное ИЛИ.

Выход счетчика 6 соединен с вторым адресным входом блока 9 памяти, а выход переноса - со счетным входом

Q вт.орого триггера 19, выход которого подключен к четвертому входу блока 8.

Установочные входы триггеров 18 и 19 подключены к девятому выходу блока 8 управления, десятый выход

с которого подключен к управляющему входу сумматора 5, а одиннадцатый выход - к шестому входу генератора 12.

Второй выход блока 9 памяти подJ- ключен к .пятому входу блока 8 управления. ,

Устройство работает следующим образом.

55 Контроль осуществляют в трех режимах: режиме начальной установки, режиме генерации испытательных сигналов и режиме считывания результатов испытаний.

35

В режиме начальной установки блок 8 управления вырабатывает сигнал Начальная установка по своему первому выходу в момент t (фиг.2а). Он сбрасывает в нуль сумматор 5 и первый счетчик 6, устанавливает в исходное состояние генератор 12 линейно изменяющегося напряжения.

В момент t, на восьмом выходе блока 8 управляющий сигнал переходит в единичное состояние и подключает выход ключа 16 к второму выходу генератора .1 псевдослучайных кодов, на ко20

тором формируется сигнал XI (фиг.26). 15 ным, нормальным или какого-либо дру- В блоке 8 управления этот сигнал инвертируется, и инверсный сигнал Х2 (фиг,2в) снимается с десятого выхода блока 8.

Управляющий код на вторам выходе блока 8 подключает выход коммутатора 2 к выходу регистра 3 напряжения, и его параллельный цифровой код Ng п,п. ..п., где к - разрядность кода, поступает на вход сумматора 5. Стар- .ший разряд кода является знаковым и подключен к второму входу генератора 12.

В момент t по сигналу Х2 происходит запись кода в сумматор 5 (фиг 2 виг). На четвертый вход генератора 12 поступает параллельный цифровой код с выхода блока 11 задания крутизны фронта испытательного сигнала. В момент ij (фиг.2д) сигнал Z2 на одиннадцатом выходе блока 8 своим задним фронтом запускает генератор 12, который на своем первом выходе воспроизводит напряжение, из менякщееся по линейному закону с заданной крутизной:

гого- вида.

В этом режиме блок 8 управления подключает выход коммутатора 2 к первому выходу генератора 1 псевдослучайных кодов. Генератор 1 формирует псевдослучайную последовательность цифровых кодов U N., которые определяют приращение к начальному значению кода в сумматоре 5. Старший раз- 25 ряд цифрового кода является знаковым: О - приращение положительное. 1 - приращение отрицательное.

По сигналу Х2 приращение Л N суммируется с кодом N в сумматоре 5.

30

Генератор 12 линейно изменяющегося напряжения начинает вьфабатьшать напряжение (фиг.2д)

и

,,sign п, К,М

,

На третий вход генератора 12 теперь поступает суммарный код и в нем

40

происходит.сравнение U напряжением

U,K,(,)

Bblt

с текущим

и

вых

(t)sign К,М t.

где К, - коэффициент преобразования

Код Ng, хранящийся в это время в сумматоре 5, поступает на третий вход генератора 12, в котором происходит преобразование его в напряже- и сравнение с выходным

ние ,N напряжением U

еых

вых

в момент равенства (фиг.2д) генератор 12 прекращает генерацию линейного сигнала и фиксирует уровень выходного напряжения UQ. Одновременно на втором выходе генератора 12 появляется сигнал поступающий на второй вход блока 8 упра.вления, который переводит блок 8 в режим генерации испытательного

сигнала. При этом на третьем выходе блока 8 появляется управляющий сигнал , поступающий на управляющий вход счетчика 6 и разрешающий перепись в него цифрового кода из сумматора 5. В режиме генерации испытательных сигналов на выходе устройства формируется сигнал со случайными значениями уровней постоянного напряжения и заданной крутизной фронта. Закон распределения случайных значений сигнала задается генератором 1 псевдослучайных кодов и может быть.равномер

ным, нормальным или какого-либо дру-

гого- вида.

В этом режиме блок 8 управления подключает выход коммутатора 2 к первому выходу генератора 1 псевдослучайных кодов. Генератор 1 формирует псевдослучайную последовательность цифровых кодов U N., которые определяют приращение к начальному значению кода в сумматоре 5. Старший раз- ряд цифрового кода является знаковым: О - приращение положительное. 1 - приращение отрицательное.

По сигналу Х2 приращение Л N суммируется с кодом N в сумматоре 5.

30

Генератор 12 линейно изменяющегося напряжения начинает вьфабатьшать напряжение (фиг.2д)

и

,,sign п, К,М

,

На третий вход генератора 12 теперь поступает суммарный код и в нем

происходит.сравнение U напряжением

U,K,(,)

Bblt

с текущим

В момент их равенства U

вых

фикси5

0

5

руется на уровне U . Затем генератор 1 вырабатывает следующее значение кода u.N и происходит формирование следукнцего уровня испытательного напряжения и т.д.

Так как содержимое сумматора 5 в каждом следующем такте переписывается в счетчик 6, то в устройстве происходит запоминание кодов N; и , соответствующих уровням выходного напряжения U- и U,, в данном и пре- дьщущих тактах работы (фиг.2к). Это обстоятельство используется для запоминания условий работоспособности контролируемого блока. Код N в сумматоре 5 используется как адрес стро5 ,1

ки матрицы запоминающих ячеек блока 9 памяти и поступает на первый адресный вход этого блока. Код N; в первом счетчике 6 используется как адрес столбца матрицы и поступает на второй адресный вход блока 9 памяти. Таким образом кодовая комбинация (N; , N, ) позволяет поставить в соответствие каждому возможному перепаду испытательного напряжения (U; , и. ) одну и только одну запоминающую ячейку блока 9 памяти. Это обстоятельство используется для обработки результатов испытания контролируемого электронного блока на помехоустойчивость.

Перед началом испытаний во все ячейки блока 9 памяти заносится в обратном коде целое число q, определяющее допустимое число сигналов отказа или сбоев электронного блока в процессе испытаний.

Величина q имеет вероятностный смысл и определяется по заданной достоверности контроля.

Контроль выходных параметров контролируемого электронного блока производит блок 14 анализа, который определяет находится ли данный параметр в заданных границах и в случае выхода параметра за пределы границы работоспособности блок 14 анализа вырабатывает на своем выходе сигнал.

Если при воздействии перепада напряжения питания (Uj, U;, ) происходит отказ или сбой в контролируемом электронном блоке, то блок 14 анализа вьфабатывает сигнал (фиг,2м), пос- тупак)щий на первый вход блока 8 управления. Последний на своем шестом выходе формирует управляющий сигнал Чтение для блока 9 памяти (фиг.2н), который разрешает считывание числа из ячейки с адресом (N;, N. ). Затем через время с , необходимое для завершения переходного процесса чтения, блок 8 вырабатывает сигнал Вы-, вод на своем четвертом выходе (фиг. 2п), который поступает на управляющий вход счетчика 7 и разрешает запись числа из блока 9 памяти в счетчик 7.. После этого на пятом выходе блока 8 управления появляется сигнал +Г , поступаюпщй на счетный вход счетчика 7, и число в нем увеличивается на единицу. На седьмом выходе блока 8 формируется сигнал Запись, посту- .пающий на второй управляющий вход

90 6

блока 9 памяти и разрешающей запись нового числа из счетчика 7 в блок 9 памяти по адресу. Так как исходные числа в блоке 9 памяти хранились в обратном коде, то после q сбоев (или больше сбоев) при одном и том же перепаде напряжений в течение процесса испытаний число в данной ячейке будет равно нулю шш станет положительным.

Следовательно, после достаточно длительного периода испытаний электронного блока он будет неоднократно подвергнут воздействию всех возможных комбинаций перепадов уровней напряжения питания с заданной крутизной фронта перепада. Массив значений, хранящихся в блоке 9 памяти, будет описывать область работоспособности

электронного блока при воздействиях помех по цепи питания. Эта область определяется множеством ячеек памяти блока 9, содер жащих числа q . При этом адреса таких ячеек (Nj, N ; )

определяют собственно значения допустимых перепадов напряжения питания (U;, U;, ). Ячейки блока 9 памяти, в которых q 5:0, характеризуют ситуации, приводящие к сбоям или отказам в контролируемом электронном блоке.

Идентификация нарушений работос- пособности обеспечивается однознач- ным соответствием адресов этих ячеек памяти уровнем перепада испытательного сигнала.

Возможны ситуации, когда одновременно с допустимой комбинацией уровней напряжения питания (U, U ) по другим цепям контролируемого электронного блока приходит помеховый сигнал, приводящий к его ложному срабатыванию или отказу. В этом случае блок 14 анализа з.афиксирует это событие и изменит содержимое соответствующей ячейки памяти блоков 9. Для исключения влияния других сигналов на работу контролируемого блока в устройстве используется предварительное занесение во все ячейки блока 9 памяти числа q, выполняющего функцию порога срабатывания. При этом используется

тот факт, что вероятность двойного совпадения допустимой случайной комбинации (U-, и,-, ) и помехового сигнала по другим цепям контролируемого блока достаточно мала.

7, 1

Для сокращения времени испытаний в устройстве при выработке каждого нового кода анализируется произошчо ли допустимое число отка.зов для комбинации (N;, N-, ). Если получили утвердительньш ответ, то организуется приращение кода в сумматоре 5 на величину лЫд приращения адреса и для новой комбинации (N +uN, N.., ) анализ повторяется. Так продолжается до тех пор, пока не будет найдена разрешенная комбинация ( Nj+m&Np, N- ), для которой . Это означает что область допустимых параметров испытательного напряжения просматриваеся.

Временная диаграмма анализа кодов показана на фиг.2. Положим , т.е. допускается только однократный сбой для каждой комбинации испытат ельного напряжения. По переднему фронту сигнала Z2 считывается содержимое ячейки (N, , NJJ), момент t на фиг.2. Контрольный разряд г ячейки блока 9 памяти поступает на пятый вход блока 8 управления. Если г 1, то отказа или сбоя контролируемого блока прн данной комбинации кодов не было. Если т 0, то qiO и вторичная пода- напряжения Uf после действия Ug запрещена. На фиг.2м в момент t при анализе кода N, значение г,, 1 и блок 8 разрешает переход сигнала Z2 на нулевой уровень. Этот переход запускает генератор 12 на формирование уровня и, испытательного напряжения.

Предположим, что при действии U, произошел сбой (фиг.2м). Содержимое соответствующей ячейки блока 9 увеличивается на 1, т.е. q равно нулю. Следовательно, последовательная подача на контролируемый электронный блок напряжений U теперь запрещена .

Если в какой-либо момент времени после подачи кода N; генератор 1 снова вырабатывает код N, (момент t), то при считывании ячейки (N, N ) разряд Г| 0, и блок 8 управления вьщае нулевой уровень сигнала Z1 (фиг.2и). Сигнал с девятого выхода блока 8 устанавливает триггеры 18 и 19 в единичное состояние. Одновременно фиксируется высокий уровень сигнала Z2. По нулевому уровню сигнала Z1 ключ 16 подключает к своему выходу вход генератора 15 импульсов. Сигналы генератора 15 следуют с большей

0

частотой, чем импульсы генератора 1. Кроме того, ключ 17 подключает выход переноса сумматора 5 к счетному входу триггера 18. Теперь блок 8 обеспечивает приращение кода в сумматоре и запрещает изменение кода в счетчике 6. Для этого коммутатор 2 подключает к входу сумматора 5 выход

регистра 4 приращения адреса. Начинается просмотр ячеек блока 9 памяти. На фиг.2 показан случай, когда для кода N|+uNg комбинация (, N,,) разрешена. Тогда при -считывании г 1

(фиг.2л) и сигнал Z2 блока. 8 задним фронтом запускает генератор 12. Одновременно ключ 16 опять подключает генератор 1 к входу сумматора 5. В режиме считывания результатов

испытаний происхо; ит перепись содер34СИМОГО блока 9 памяти в блок 10 ре- гистрации, в качестве которого могут использоваться устройства типа ленточного перфоратора, устройства записи на магнитную ленту, а также устройства сопряжения с ЭВМ.

Режим начинается (фиг.За) с выработки сигнала Установка режима считывания на первом выходе блока 8

управления. При этом сумматор 5, счетчик 6 и генератор 12 устанавливаются в исходное состояние. В отличие от предыдущего режима в сумматоре 5 фор

мируется детерминированная последовательность кодов, позволяющая последовательно считывать одну ячейку блока 9 за другой. Для этого сигнал на втором выходе блока 8 управления подключает выход коммутатора 2 к ре- гистру 4 приращения адреса.

По сигналу Х2 (фиг.Зв) происходит последовательное увеличение адресного, кода в сумматоре 5. При этом сигнал на третьем выходе блока 8 управ- ения блокирует перепись кода из сумматора .5 в счетчик 6. В третьем режиме состояние счетчика 6 изменяется . по сигналам переноса на выходе переноса сумматора 5 в моменты когда в

нем происходит переполнение.

По сигналам Х1 (фиг.36) блок 8 управления вырабатывает управляющий сигнал Чтение (фиг.Зж) для блока 9 памяти, в результате чего на его выходе появляется код числа q в соответствующей ячейке памяти. Этот код поступает на вход 10 блока регистрации.

Сигнал Вывод на четвертом выходе блока 8 управления (фиг.Зз) показывает, что считываемый из блока 9 памяти код установился.

Таким образом последовательно считывается весь объем памяти блока 9, хранящий результаты испытания электронного блока. Последовательность поступления кодов в блок 10 регистра ции синхронизирована с порядком изменения адресов при считывании из блока 9 памяти, что позволяет построить, в блоке регистрации двумерную область работоспособности электрон- Вого блока в координатах -U;, Uj ; i, j 1,К, где К - чийло дискретных уровней напряжения питания блока. Формула изобретения

Устройство для контроля области работоспособности электронных блоков содержащее генератор линейно изменяющегося напряжения, блок анализа, вход которого соединен с выходом блока для подключения объекта контроля, блок памяти, генератор псев- дослучайньт кодов, регистр напряжения, регистр приращения адреса, сумматор, первый и второй счетчики, блок задания Крутизны фронта, блок управления, блок регистрации и коммутатор, причем выход блока анализа соединен с первым входом блока управления, выход регистра напряжения соединен с первым входом коммутатора, второй вход которого соединен с выходом регистра приращения адреса, третий вход - с первым выходом генератора псевдослучайных кодов, а уп- - равляйщий вход - с вторым выходом блока управления, -информационный вход сумматора соединен с выходом коммутатора и вторым входом генератора линейно изменяющегося напряжения, пергый выход которого соединен с входом блока подключения объекта контроля, информационньм вход перого счетчика соединен с выходом сумматора, третьим входом генератора линейно изменяющегося напряжения и первым адресным входом блока памяти, управляющий вход - с третьим выходом блока управления, установочный вход - с первым выходом блока управления.

5

5

5

0

5

0

5

0

5

первым входом генератора линейно изменяющегося напряжения и установочным входом сумматора, а первый выход - с вторым адресным входом блока памяти, информационный вход второго счетчика соединен с первым выходом блока памяти и информационным входом блока регистрации, управляющий вход - с четвертым выходом блока управления и управляющим входом блока регистрации, счетный вход - с пятым выходом блока управления, а выход - с входом записи блока памяти, первый и второй управляющие входы которого соединены с шестым и седьмым вькодами блока управления соответственно, выход блока задания крутизны фронта соединен с четвертьп входом генератора линейно изменяющегося напряжения, второй выход которого соединен с вторым входом блока управления, отличаю-ще- е с я тем, целью повышения быстродействия и обеспечения неразрушающего контроля, в него введены генератор импульсов, первый и второй ключи, первый и втарой триггеры, причем выход генератора импульсов подключен к входу генератора псевдослучайных кодов и первому входупервого ключа, второй вход которого соединен с вторым выходом генератора псевдослучайных кодов, управляющий вход - с восьмым выходом блока управления и управляющим входом второго ключа, а выход- с третьим входом блока управления и пятым входом генератора линейно изменяющегося напряжения, вход второго ключа соединен с выходом переноса сумматора, первый выход - со счетным входом первого триггера, а второй вькод - со счетным входом первого счетчика и выходом первого триггера, выход переноса первого счетчика соединен Со счетным входом второго триггера, выход которого подключен к четвертому входу блока управления, а установочные Ёходы первого и второго триггеров соединены с девятым выходом блока управления, десятый вькод которого подключен к управляющему входу сумматора, а одиннадцатый выход - к шестому входу генератора линейно изменяющегося напряжения, второй выход блока памяти соединен с пятым входом блока управления.

tz t,

t-f te tg tio

XI

Сумма- /пор 5

г

(x

д

Cvfmwk

mf- V

ffft//ffff 3

Составитель В.Савинов Редактор А.Дежнина Техред В.Кадар Корректор М.Шароши

Заказ 3579/48 Тираж 730Подписное

ВНИИЖ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва Ж-35, Раушская наб., д.4/3

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Фс1.Ъ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля области работоспособности электронных блоков | 1984 |

|

SU1228056A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1987 |

|

SU1540025A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство телеконтроля линейных трактов цифровых систем передачи | 1986 |

|

SU1385303A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1983 |

|

SU1172056A1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Устройство для определения области работоспособности радиоэлектронных схем | 1986 |

|

SU1386947A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Генератор испытательных последовательностей | 1987 |

|

SU1543396A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

Изобретение позволяет уменьшить . вероятность выхода из строя контролируемого блока при испытании и сократить время испытаний. Устройство содержит генератор 1 псевдослучайньк кодов, коммутатор 2, регистр 3 напряжения, регистр приращения адреса, сумматор 5, счетчики 6 и 7, блок 8 управления, блок 9 памяти, блок 10 регистрации, блок 11 задания крутизны фронта, генератор 12 линейно из- меняющегося напряжения и блок 14 анализа. Введение генератора 15 импульсов, ключей 16 и 17, триггеров 19 и , 18 сокращает переборы комбинации испытательных сигналов, при которых произошло допустимое число сбоев или отказов, и исключает их из последовательности испытательньлх напряжений. 3 ил. О) со 00 о ел со

| Устройство для измерения области работоспособности электронных схем | 1975 |

|

SU555353A1 |

| Устройство для контроля области работоспособности электронных блоков | 1984 |

|

SU1228056A1 |

Авторы

Даты

1987-08-15—Публикация

1985-11-04—Подача