Изобретение относится к иьтульс- ной технике и может быть использовано в системах передачи информации.

Цель изобретения - расширение функциональных возможностей за счет управления периодом генерируемых последовательностей.

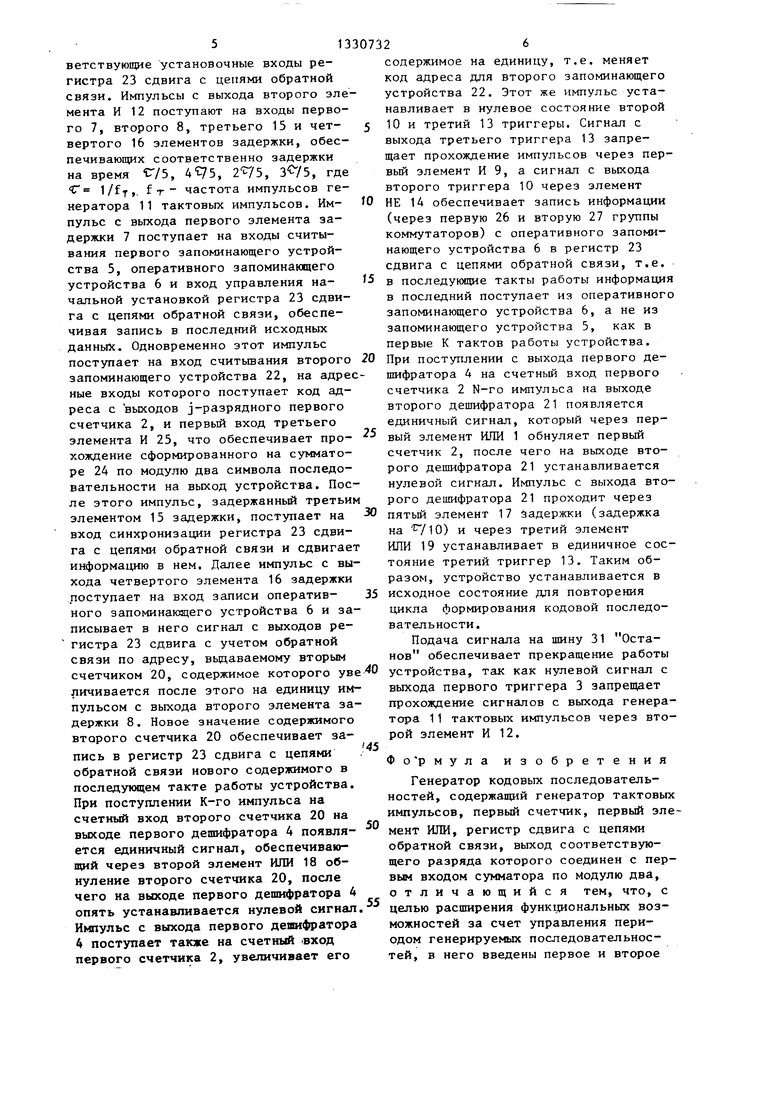

На чертеже представлена структурная схема генератора кодовых последовательностей.

Генератор кодовых последовательностей содержит первый элемент ИЛИ1, первый счетчик 2, первый триггер 3, первый дешифратор 4, первое запоминающее устройство 5, оперативное запоминающее устройство 6, первый 7 и второй 8 элементы задержки, первый элемент И 9, второй триггер 10, генератор 11 тактовых импульсов, второй элемент И 12, третий триггер 13, элемент НЕ 14, третий 15, четвертый 16 и пятый 17 элементы задержки, второй 18 и третий 19 элементы ИЛИ, вто30

35

40

рой счетчик 20, второй дешифратор 21, 25 запоминающих устройств соединены межвторое запоминающее устройство 22, регистр 23 сдвига с цепями обратной связи, сумматор 24 по модулю два, третий элемент И 25, первую 26 и вторую 27 группы коммутаторов, шину 28 Пуск, первую 29 и вторую 30 группы кодовых шин, шину 31 Останов, соединенную с первым установочным входом первого триггера 3, второй установочный вход которого соединен с первым входом третьего элемента ИЛИ 19, первым входом первого элемента ИЛИ 1 и первым входом второго элемента ИЛИ 18, выход которого соединен с входом установки второго счетчика 20,выходы которого соединены с соответствующими входами первой группы адресных входов первого запоминающего устройства 5, адресными входами оперативного запоминающего устройства 6 и с входами первого дешифратора 4, выход которого соединен с вторым входом второго элемента ИЛИ 18, первым установочным входом второго триггера 10 и первым установочным входом третьего триггера 13, выход которого соединен с первым входом первого элемента И 9, выход которого соединен с вторым установочным входом второго триггера 10, выход которого соединен с первыми объединенными входами первой 26 и второй 27 групп коммутаторов и входом элемента НЕ 14, выход которого соединен с втоду собой и с входом управления регистра 23 сдвига с цепями обратной связи, выходом первого элемента задержки 7 и первым входом третьего элемента И 25, второй вход которого соединен с выходом сумматора 24 по модулю два, второй вход которого соединен с выходом второго запоминающего устройства 22, адресные входы которого соединены с соответствующими выходами первого счетчика 2 и второго дешифратора 21, выход которого соединен с входом пятого элемента задержки 17 и вторым входом первого элемента ИЛИ 1, выход которого соединен с входом установки первого счетчика 2, счетный вход которого соединен с первым входом установки третьего триггера 13, второй вход ус- g тановки которого соединен с выходом третьего элемента ИЛИ 19, второй вход которого соединен с выходом пятого элемента задержки 17. Счетный вход второго счетчика 20 соединен с выходом второго элемента 8 задержки, вход которого соединен с входом первого элемента 7 задержки, выход второго элемента И 12, вторым входом первого элемента И 9 и входами третьего 15 и четвертого 16 элементов задержки, выходы которых соединены соответственно с входом синхронизации регистра 23 сдвига с цепями обратной связи и входом записи опера50

55

рыми объединенными входами первой 26 и второй 27 групп коммутаторов, выходы которых соединены с соответствующими входами регистра 23 сдвига с цепями обратной связи, выходы которого соединены с соответствующими входами оперативного запоминающего устройства 6, выходы которого соединены с третьими входами соответствующих коммутаторов первой 26 и второй 27 групп коммутаторов, четвертые входы коммутаторов которой соединены с соответствуюпщми шинами второй

группы 30 кодовых шин. Шины первой группы 29 кодовых шин соединены с соответствующими входами второй группы адресных входов первого запоминающего устройства 5, выходы которого

соединены с четвертыми входами со- ответствуюш 1х коммутаторов первой группы 26 коммутаторов. Входы считывания оперативного запоминающего устройства 6, первого 5 и второго 22

запоминающих устройств соединены между собой и с входом управления регистра 23 сдвига с цепями обратной связи, выходом первого элемента задержки 7 и первым входом третьего элемента И 25, второй вход которого соединен с выходом сумматора 24 по модулю два, второй вход которого соединен с выходом второго запоминающего устройства 22, адресные входы которого соединены с соответствующими выходами первого счетчика 2 и второго дешифратора 21, выход которого соединен с входом пятого элемента задержки 17 и вторым входом первого элемента ИЛИ 1, выход которого соединен с входом установки первого счетчика 2, счетный вход которого соединен с первым входом установки третьего триггера 13, второй вход ус- тановки которого соединен с выходом третьего элемента ИЛИ 19, второй вход которого соединен с выходом пятого элемента задержки 17. Счетный вход второго счетчика 20 соединен с выходом второго элемента 8 задержки, вход которого соединен с входом первого элемента 7 задержки, выход второго элемента И 12, вторым входом первого элемента И 9 и входами третьего 15 и четвертого 16 элементов задержки, выходы которых соединены соответственно с входом синхронизации регистра 23 сдвига с цепями обратной связи и входом записи опера

тивного запоминающего устройства 6. Выход генератора 11 тактовых импульсов соединен с первым входом второго элемента И 12, второй вход которого соединен с выходом первого триггера 3. Выход соответствующего разряда регистра 23 с цепями обратной связи соединен с первым входом сумматора 24 по модулю два.

Генератор кодовых последовательностей работает следующим образом.

В процессе работы генератор формирует кодовые последовательности длины М KN, где N 2 - 1, j - произвольное целое положительное число, К 2L (L - объем исходной системы кодовых последовательностей длины). Кодовые последовательности длины М формируются из элементов К различных кодовых последовательностей исходной системы с использованием метода чередования (перемешивания) . Формирование К различных кодовых последовательностей исходной системы обеспечивается занесением в га-разрядный регистр 23 сдвига с цепями обратной связи информации на первых К тактах работы устройства. На п

разрядов регистра 23 сдвига с цепями ЗО гой группы из К различных последоваобратной связи информация поступает из первого запоминающего устройства 5, а на остальные разряды - с шин второй группы 30 кодовых, шин, определяющих

номер формируемой кодовой последова- группы 29 кодовых шин. В начальном

тельности длины М. В первом запоминающем устройстве 5, адресация страничная - на 1 адресных входов второй группы входов () подается адрес

состоянии первый триггер 3 находитс в нулевом состоянии. Сигнал, поступающий по шине 28 Пуск на второй вход установки первого триггера 3,

страницы с внешних шин первой группы 40 устанавливает его в единичное сос- 29 кодовых шин, а адрес слова на тояние и через второй элемент ИЛИ 18,

третий элемент ИЛИ 19 и первый элемент ИЛИ 1 устанавливает в нулевое

состояние второй п-разрядный счетстранице подается на входы первой группы входов первого запоминающего устройства 5 с выходов второго счетчика 20. С выходов первого запоминаю-45 ик 20, первый j-разрядный счетчик 2, щего устройства 5 на К первых тактаха третий триггер 13 - в единичное работы устройства в регистр 23 сдви-состояние. Последний разрешает при га с цепями обратной связи заносятсяэтом прохождение импульсов генерато- К различных комбинаций, что в сочета-ра 1 1 тактовых импульсов через первый НИИ с кодом номера кодовой последова- Q элемент И 9 (второй элемент И 12 оттельности на шинах второй группы 30 кодовых шин обеспечивает подготовку устройства к формированию К различных кодовых последовательностей исходной системы.

Формирование кодовой последователь ности длины М К(2 - 1) происходит следующим образом. После формирования каждого i-ro символа последователькрыт) . Первый из этих импульсов устанавливает в единичное состояние второй триггер 10, сигнал с выхода ко-, торого поступает на объединенные пер- gg вые входы первой 26 и второй 27 групп коммутаторов, подготавливая их к передаче информации с выходов первого запоминающего устройства 5 и с шин второй группы 30 кодовых шин на соотности (i 1,Й), получаемого суммированием по модулю два содержимого старшего разряда регистра 23 сдвига с цепями обратной связи и содержимого выхода второго запоминающего устройства 22, хранящего порождающий многочлен исходного кода, на сумматоре 24 по модулю два, осуществляется сдвиг

в регистре 23 сдвига с цепями обратной связи, информация с которого запоминается в оперативном запоминающем устройстве 6, после чего адрес первого запоминающего устройства

5 и оперативного запоминающего устройства 6 увеличивается на единицу. Затем в регистр 23 сдвига с цепями обратной связи заносятся новые данные из первого запоминающего устройства 5

(на первых К тактах формирования) или из оперативного запоминающего ,уст- ройства 6 (на последующих К(2 -2) тактах формирования). Изменение номера кодовой последовательности на шинах второй группы 30 кодовых шин приводит к изменению всех К комби11аций, заносимых в регистр 23 сдвига с цепями обратной связи, т.е. последний подготавливается к формированию друтельностей. Дпя изменения структуры формируемых кодовых последовательностей необходимо изменить код номера формируемой системы на шинах первой

группы 29 кодовых шин. В начальном

состоянии первый триггер 3 находится в нулевом состоянии. Сигнал, поступающий по шине 28 Пуск на второй вход установки первого триггера 3,

состояние второй п-разрядный счет ик 20, первый j-разрядный счетчик а третий триггер 13 - в единичное состояние. Последний разрешает при этом прохождение импульсов генерато ра 1 1 тактовых импульсов через перв элемент И 9 (второй элемент И 12 от

ик 20, первый j-разрядный счетчик 2, а третий триггер 13 - в единичное состояние. Последний разрешает при этом прохождение импульсов генерато- ра 1 1 тактовых импульсов через первый элемент И 9 (второй элемент И 12 открыт) . Первый из этих импульсов устанавливает в единичное состояние второй триггер 10, сигнал с выхода ко-, торого поступает на объединенные пер- вые входы первой 26 и второй 27 групп коммутаторов, подготавливая их к передаче информации с выходов первого запоминающего устройства 5 и с шин второй группы 30 кодовых шин на соот

ветствующие установочные входы регистра 23 сдвига с цепями обратной связи. Импульсы с выхода второго элемента И 12 поступают на входы первого 7, второго 8, третьего 15 и четвертого 16 элементов задержки, обеспечивающих соответственно задержки на время Г/З. ч1Ъ, , , где Г l/ff,, fr частота импульсов генератора 11 тактовых импульсов. Импульс с выхода первого элемента задержки 7 поступает на входы считывания первого запоминающего устройства 5, оперативного запоминающего устройства 6 и вход управления начальной установкой регистра 23 сдвига с цепями обратной связи, обеспечивая запись в последний исходных данных. Одновременно этот импульс поступает на вход считьшания второго запоминающего устройства 22, на адре ные входы которого поступает код адреса с выходов j-разрядного первого счетчика 2, и первый вход третьего элемента И 25, что обеспечивает прохождение сформированного на сумматоре 24 по модулю два символа последовательности на выход устройства. После этого импульс, задержанный третьи элементом 15 задержки, поступает на вход синхронизации регистра 23 сдвига с цепями обратной связи и сдвигае информацию в нем. Далее импульс с выхода четвертого элемента 16 задержки поступает на вход записи оператив- ного запоминающего устройства 6 и записывает в него сигнал с выходов регистра 23 сдвига с учетом обратной связи по адресу, вьщаваемому вторым счетчиком 20, содержимое которого ув личивается после этого на единицу импульсом с выхода второго элемента задержки 8. Новое значение содержимого второго счетчика 20 обеспечивает запись в регистр 23 сдвига с цепями обратной связи нового содержимого в последующем такте работы устройства. При поступлении К-го импульса на счетный вход второго счетчика 20 на выходе первого дешифратора 4 появляется единичный сигнал, обеспечивающий через второй элемент ИЛИ 18 обнуление второго счетчика 20, после чего на выходе первого дешифратора 4 опять устанавливается нулевой сигнал Импульс с выхода первого дешифратора А поступает также на счетный «ход первого счетчика 2, увеличивает его

fO

5

20

25

35 40

07326

содержимое на единицу, т.е. меняет код адреса для второго запоминающего устройства 22. Этот же импульс устанавливает в нулевое состояние второй 10 и третий 13 триггеры. Сигнал с выхода третьего триггера 13 запрещает прохождение импульсов через первый элемент И 9, а сигнал с выхода второго триггера 10 через элемент НЕ 14 обеспечивает запись информации (через первую 26 и вторую 27 группы коммутаторов) с оперативного запоминающего устройства 6 в регистр 23 сдвига с цепями обратной связи, т.е. в последующие такты работы информация в последний поступает из оперативного запоминающего устройства 6, а не из запоминающего устройства 5, как в первые К тактов работы устройства. При поступлении с выхода первого дешифратора 4 на счетный вход первого счетчика 2 N-ro импульса на выходе второго дешифратора 21 появляется единичный сигнал, который через первый элемент ИЛИ 1 обнуляет первый счетчик 2, после чего на выходе второго дешифратора 21 устанавливается нулевой сигнал. Импульс с выхода второго дешифратора 21 проходит через пятьм элемент 17 Задержки (задержка на /10) и через третий элемент ИЛИ 19 устанавливает в единичное состояние третий триггер 13. Таким образом, устройство устанавливается в исходное состояние для повторения цикла формирования кодовой последовательности.

Подача сигнала на шину 31 Останов обеспечивает прекращение работы устройства, так как нулевой сигнал с выхода первого триггера 3 запрещает прохождение сигналов с выхода генератора 11 тактовых импульсов через второй элемент И 12.

45

35 40

50

55

Фо рмула изобретения

Генератор кодовых последовательностей, содержащий генератор тактовых импульсов, первый счетчик, первый элемент ИЛИ, регистр сдвига с цепями обратной связи, выход соответствующего разряда которого соединен с первым входом сумматора по Модулю два, отличающийся тем, что, с целью расширения функциональных возможностей за счет управления периодом генерируемых последовательностей, в него введены первое и второе

запоминающие устройства, оперативное запоминающее устройство, первый, второй и третий триггеры, первый и второй дешифраторы, второй счетчик, пер- вый, второй, третий, четвертый и пятый элементы задержки, элемент НЕ, второй и третий элементы ИЛИ, первый, второй и третий элементы И, первую и вторую группу коммутаторов, первую и вторую группы кодовых шин, шину Пуск и щину Останов, соединенную с первьм установочным входом первого триггера, второй установочный вход

которого соединен с первым входом тре-15 дом первого элемента задержки и пертьего элемента ИЛИ, первым входом пе вого элемента ИЛИ и первым входом второго элеме нта ИЛИ, выход которого соединен с входом установки второго счетчика, выходы которого соединены с соответствующими входами первой группы адресных входов первого запоминающего устройства, адресными входами оперативного запоминающего устройства и с входами первого дешифрато- ра, выход которого соединен с вторым входом второго элемента ИЛИ,первым установочным входом второго триггера и первым установочным входом третьего

триггера,выход которого соединен с пер- 30 ра, второй вход установки которого вым входом первого элемента И, вы- соединен с выходом третьего элемента ход которого соединен с вторым уста- ШТИ, второй вход которого соединен с новочным входом второго триггера, выход которого соединен с первыми объе35

диненными входами первой и второй групп коммутаторов и входом элемента НЕ, выход которого соединен с вторыми объединенными входами первой и второй групп коммутаторов, выходы которых соединены с соответствуюш 1ми входами регистра сдвига с цепями обратной связи, выходы которого соединены с соответствующими входами оперативного запоминающего устройства, выходы которого соединены с третьими входами соответствующих коммутаторов первой группы коммутаторов и второй группы коммутаторов, четвертые входы коммутаторов которой соединены с соответвыходом пятого элемента задержки, счетный вход второго счетчика соединен с выходом второго элемента задержки, вход которого соединен с вхо дом первого элемента задержки, выходом второго элемента И, вторым входом первого элемента И и входами третьег

40 и четвертого элементов задержки, выходы которых соединены соответственно с входом синхронизации регистра сдвига с цепями обратной связи и входом записи оперативного запоминающего

45 устройства, выход генератора тактовых импульсов соединен с первым входом второго элемента И, второй вход которого соединен с выходом первого триггера.

Редактор Н.Киштулинец

Составитель Ю.Бурмистров Техред И. Верес

Заказ 3591/55

Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ствующими шинами второй группы кодовых шин, шины первой группы кодовых шин соединены с соответствующими входами второй группы адресных входов первого запоминающего устройства, выходы которого соединены с четвертыми входами соответствующих коммутаторов первой группы ком гутаторов, входы считывания оперативного запоминающего устройства, первого и второго запо- минаю11шх устройств соединены между собой и с входом управления регистра сдвига с цепями обратной связи, выховым входом третьего элемента И, второй вход которого соединен с выходом сумматора по модулю два, второй вход которого соединен с выходом второго запоминающего устройства, адресные входы которого соединены с соответствующими выходами первого счетчика и второго де1иифратора, выход которого соединен с входом пятого элемента задержки и вторым входом первого элемента ИЛИ, выход которого соед инен с входом установки первого счетчика, счетньш вход которого соединен с первым входом установки третьего триггера, второй вход установки которого соединен с выходом третьего элемента ШТИ, второй вход которого соединен с

выходом пятого элемента задержки, счетный вход второго счетчика соединен с выходом второго элемента задержки, вход которого соединен с входом первого элемента задержки, выходом второго элемента И, вторым входом первого элемента И и входами третьего

и четвертого элементов задержки, выходы которых соединены соответственно с входом синхронизации регистра сдвига с цепями обратной связи и входом записи оперативного запоминающего

устройства, выход генератора тактовых импульсов соединен с первым входом второго элемента И, второй вход которого соединен с выходом первого триг гера.

Корректор А.Обручар

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Генератор псевдослучайных последовательностей | 1988 |

|

SU1626345A2 |

| Устройство для передачи и приема сигналов | 1978 |

|

SU765855A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Селектор импульсных сигналов | 1982 |

|

SU1058043A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Генератор псевдослучайных сигналов | 1986 |

|

SU1347166A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Устройство записи-воспроизведения многоканальной цифровой информации на магнитный носитель | 1991 |

|

SU1777176A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

Изобретение относится к импульсной технике и может быть использовано в системе передачи информации. Изобретение позволяет расширить функциональные возможности генератора путем управления периодом генерирования коЯВЗД УУ/ СЖ f9 JO довьгх последовательностей. Генератор содержит элементы ИЛИ 1, 18 и 19, счетчики 2, 20, триггеры 3, 10 и 13, дешифраторы 4 и 21, запоминающие устройства 5 и 22, оперативное запоминающее устройство 6, элементы 7, 8, 15, 16 и 17 задержки, элементы И 9, 12 и 25, генератор 11 тактовых импульсов, элемент НЕ 14, регистр 23 сдвига с цепями обратной связи, сумматор 24 по модулю два, первую 26 и вторую 27 группы коммутаторов, шину 28 Пуск, первую 29 и вторую 30 группы кодовых шин, шину 31 Останов. Генератор формирует кодовые последовательности длины М KN, где N 2- - 1, j - произвольное целое положительное число, К 2L, где L - объем исходной системы кодовых последовательностей длины. 1 ил. с S (Л т Ьа DO О со hO вш.

| Варакин Л.Е | |||

| Теория сложных сигналов | |||

| М.: Сов | |||

| радио, 1970, с | |||

| Вагонетка для кабельной висячей дороги, переносной радиально вокруг центральной опоры | 1920 |

|

SU243A1 |

| Генератор псевдослучайных последовательностей импульсов | 1981 |

|

SU984001A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-08-15—Публикация

1985-12-12—Подача