11

Изобретение относится к вычислительной технике, предназначено для иснользования в цифровых диф(1)еренци-- альных анализаторах и является усовершенствованием устройства по авт. св. № 1027725.

Цель изобретения - обеспечение работоспособности при переполнении разрядной сетки.

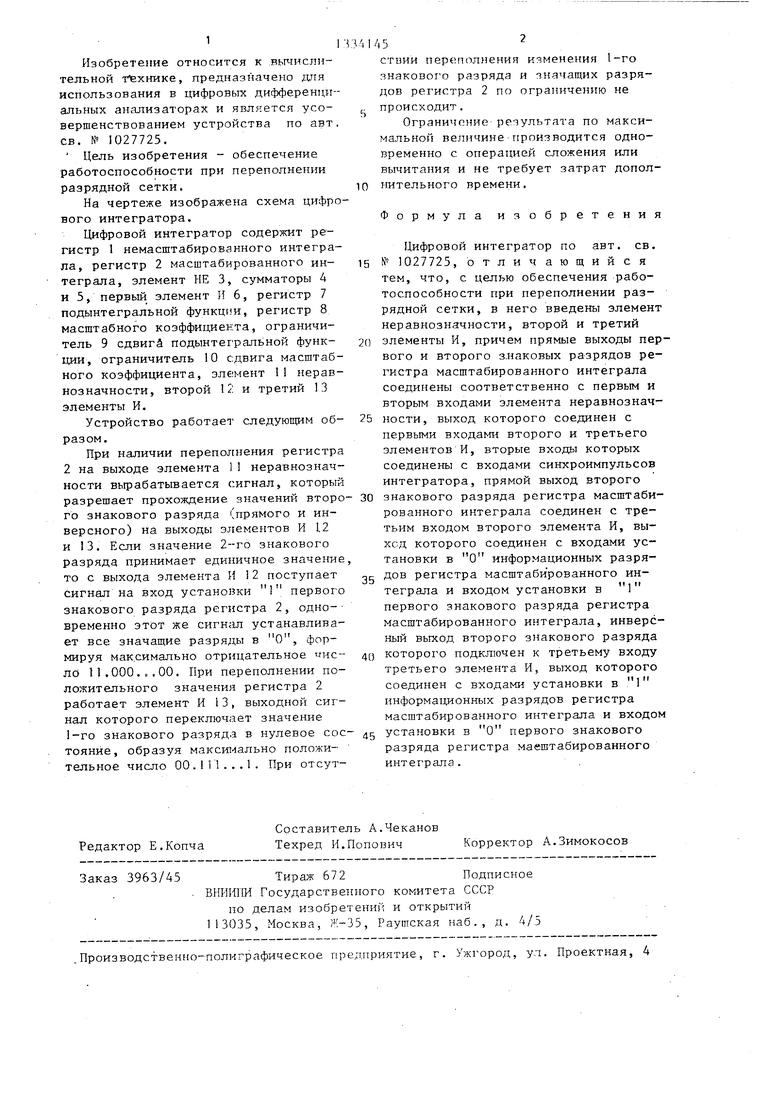

На чертеже изображена схема цифрового интегратора.

Цифровой интегратор содержит регистр 1 немасштабированного интеграла, регистр 2 масштабированного интеграла, элемент НЕ 3, сумматоры 4 и 5, первьш элемент И 6, регистр 7 подынтегральной функции, регистр 8 масштабного коэффициента, ограничитель 9 сдвиги подынтегральной функции, ограничитель 10 сдвига масштабного коэффициента, элемент 11 неравнозначности, второй 12; и третий 13 элементы И.

Устройство работает следуюш 1м образом.

При наличии переполнения регистра 2 на выходе элемента 1 неравнозначности вьфабатывается сигнал, который разрешает прохождение значений второго знакового разряда (прямого и инверсного) на выходы элементов И 1.2 и 13. Если значение 2--го знакового разряда принимает единичное значение то с выхода элемента И 12 поступает сигнал на вход устаноззки 1 первого знакового разряда регистра 2, одно- временно этот же сигн;ш устанавливает все значашие разряды в О, формируя максимально отрицательное чис-- ло 11.000...00. Нри переполнении положительного значения регистра 2 работает элемент И 13, выходной сигнал которого переключает значение 1-го знакового разряда в нулевое состояние, образуя макси1 1ально положительное число 00 . 111 ... 1. При отсутРедактор Е.Копча

Составитель А.Чеканов Техред И.Попович

3963/45

Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб. , д. 4/5

.Производственно-полиграфическое пред.приятие, г. Ужгород, ул. Проектная, 4

45

ствии переполнения изменения 1-го знакового разряда и значащих разрядов регистра 2 по ограничению не происходит.

Ограничение результата по максимальной величине производится одновременно с операцией сложения или вычитания и не требует затрат дополнительного времени.

Формула изобретения

Цифровой интегратор по авт. св.

№ 1027725, отличающийся тем, что, с целью обеспечения работоспособности при переполнении разрядной сетки, в него введены элемент неравнозначности, второй и третий

элементы И, причем прямые выходы первого и второго знаковых разрядов регистра масштабированного интеграла соединены соответственно с первым и вторым входами элемента неравнозначности, выход которого соединен с первыми входами второго и третьего элементов И, вторые входы которых соединены с входами синхроимпульсов интегратора, прямой выход второго

знакового разряда регистра масштабированного интеграла соединен с третьим входом второго элемента И, вы- хсд которого соединен с входами установки в О информационных разрядов регистра масштаби рованного интеграла и входом установки в 1 первого знакового разряда регистра масштабированного интеграла, инверсный выход второго знакового разряда

которого подключен к третьему входу третьего элемента И, выход которого соединен с входами установки в 1 информационных разрядов регистра масштабированного интеграла и входом

установки в О первого знакового разряда регистра масштабированного интеграла.

Корректор А.Зимокосов

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1982 |

|

SU1027725A1 |

| Устройство масштабирования цифрового дифференциального анализатора | 1983 |

|

SU1156069A1 |

| Параллельный цифровой интегратор с пла-ВАющЕй зАпяТОй | 1977 |

|

SU828199A1 |

| Устройство для анализа и обработки знаковых разрядов | 1980 |

|

SU962921A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1064280A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых дифференциальных анализаторах. Целью изобретения является обеспечение работоспособности при переполнении разрядной сетки. Интегратор содержит регистр 1 немасштабированного интеграла, регистр 2 масштабированного интеграла, элемент НЕ 3, сумматоры 4 и 5, элементы И 6, 12, 13, регистр 7 подынтегральной функции, регистр 8 масштабного коэффициента, ограничитель 9 сдвига подынтегральной функции, ограничитель 10 сдвига масштабного коэффициента, элемент неравнозначности 1 1 . При переполнении разрядной сетки в переходном процессе в регистр масштабированного интеграла записывается в зависимости от знака наибольшее или наименьшее значение, что устраняет переполнение и переход интегратора в релейный режим. 1 ил. (Л с 00 со . NU СП 14)

| Цифровой интегратор | 1982 |

|

SU1027725A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-30—Публикация

1986-02-19—Подача