1

Изобретение относится к вьиисли- тельной технике и автоматике и может быть использовано в качестве системы контроля и управления нижнего уровня в специализированных программных контрольно-проверочных и управляющих комплексах для АСУ ТП.

Цепь изобретения - повьт ение оперативности и достоверности контроля,

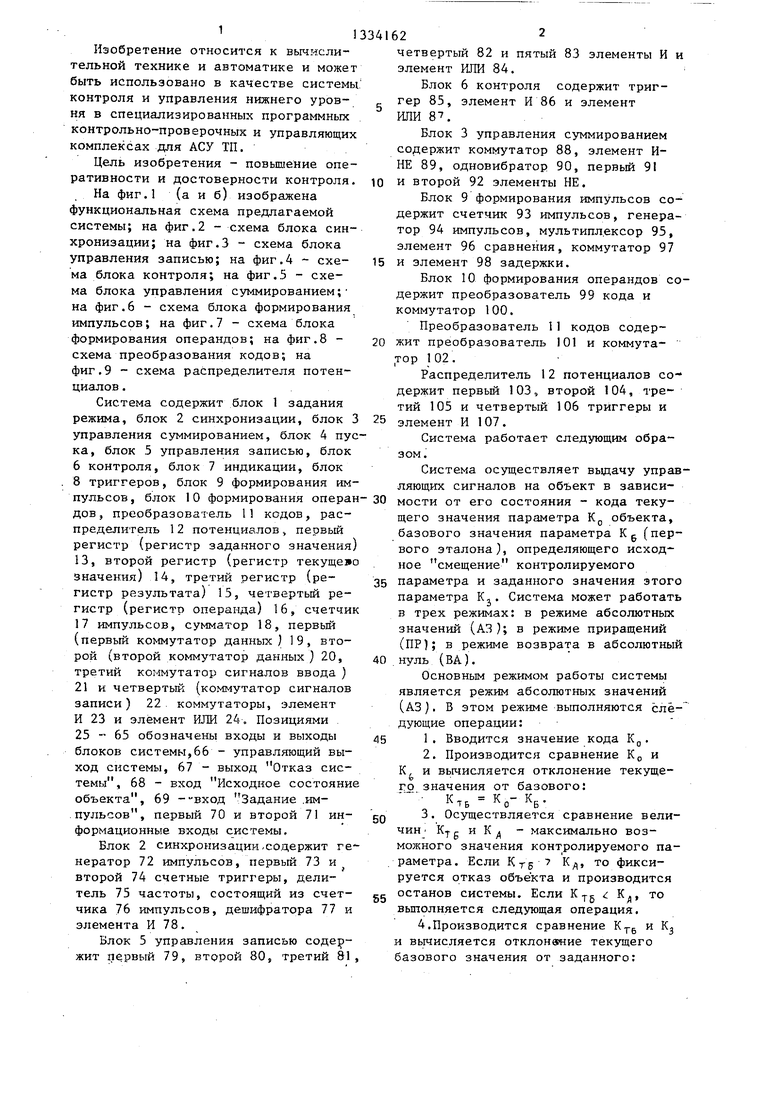

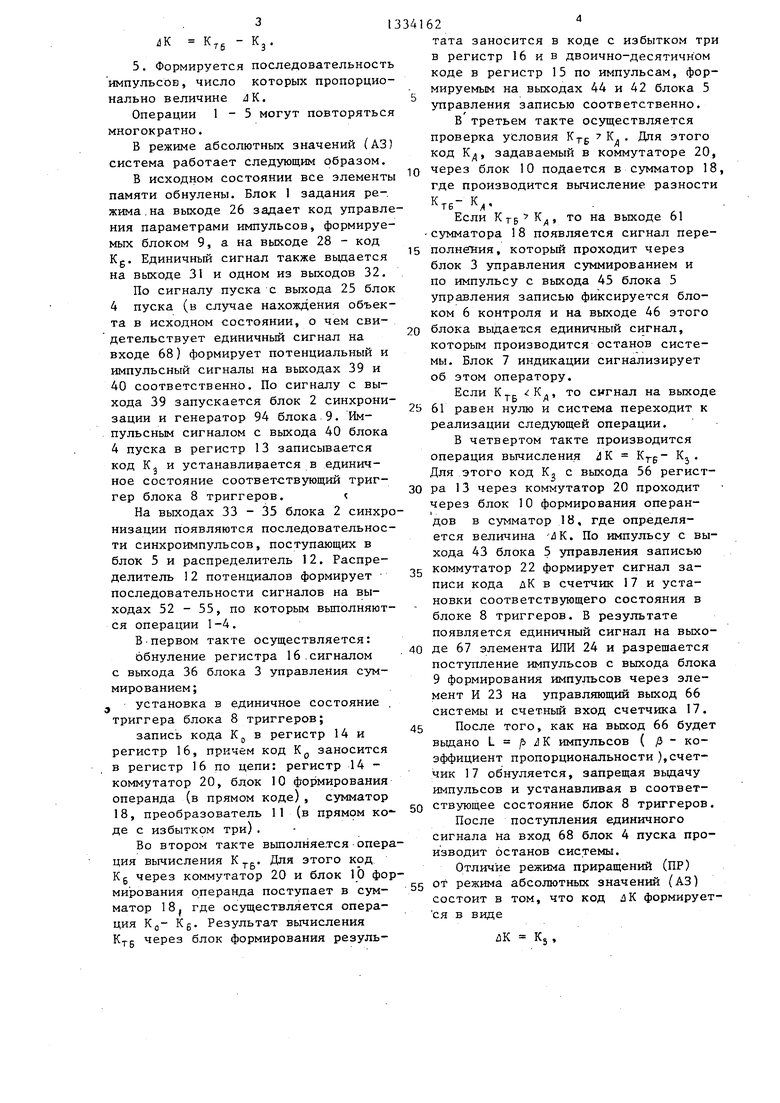

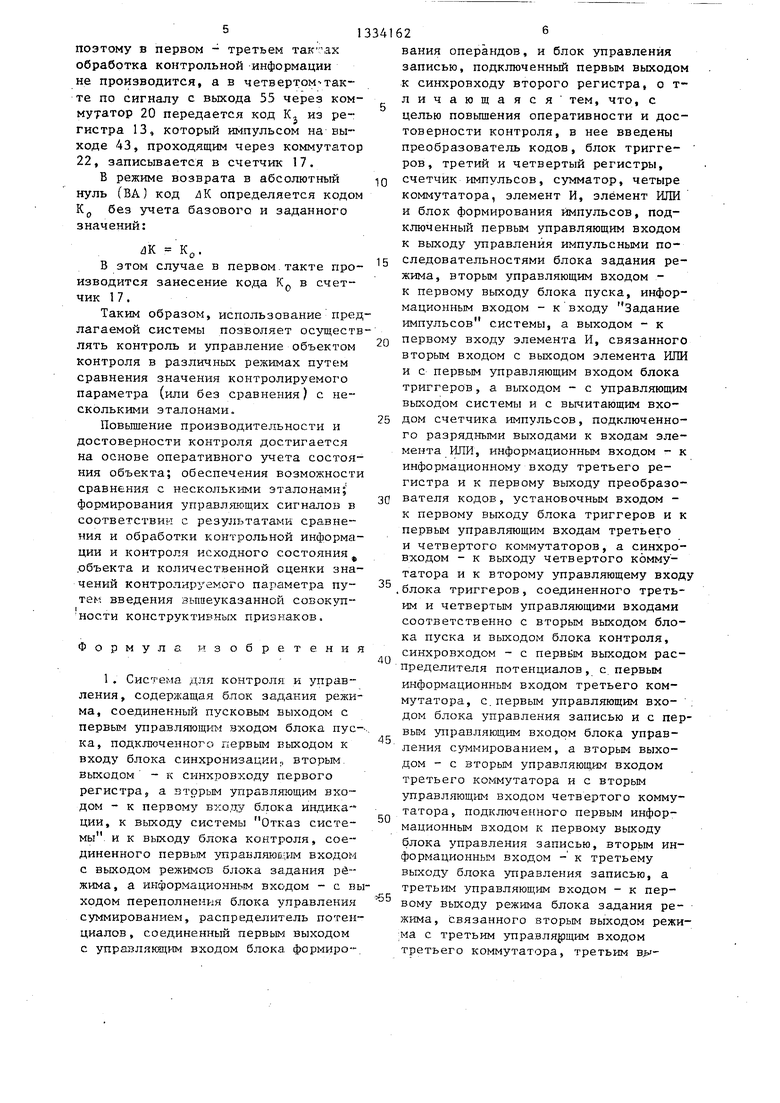

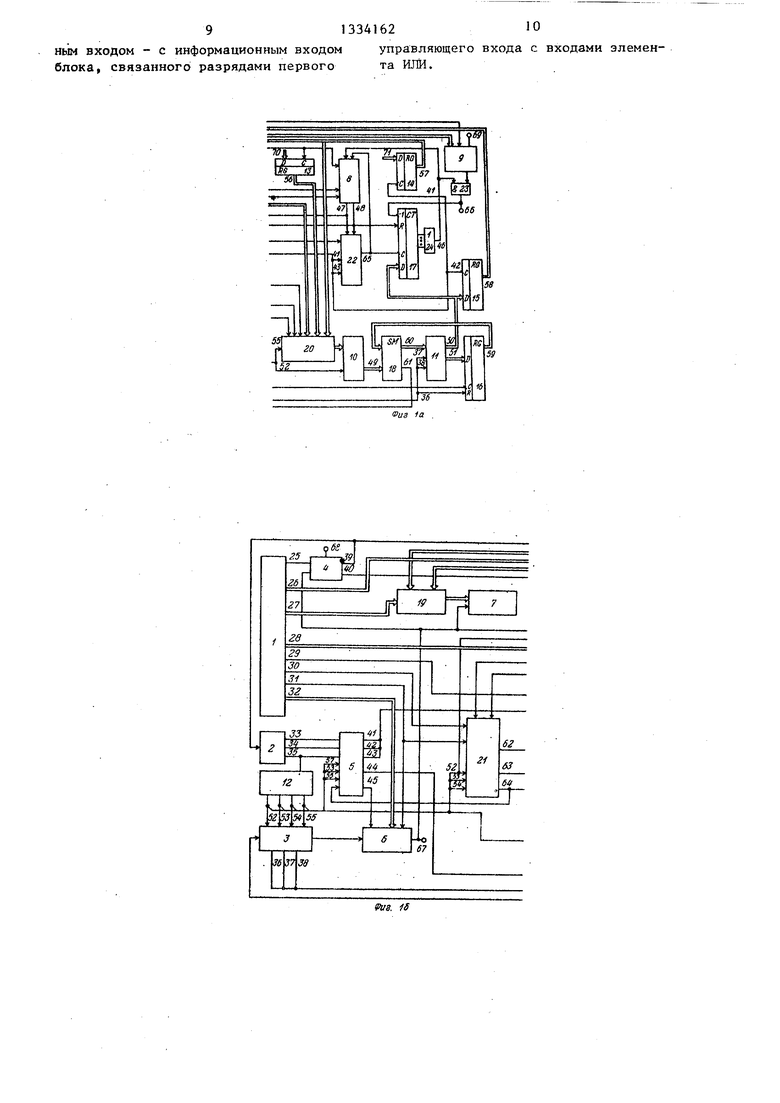

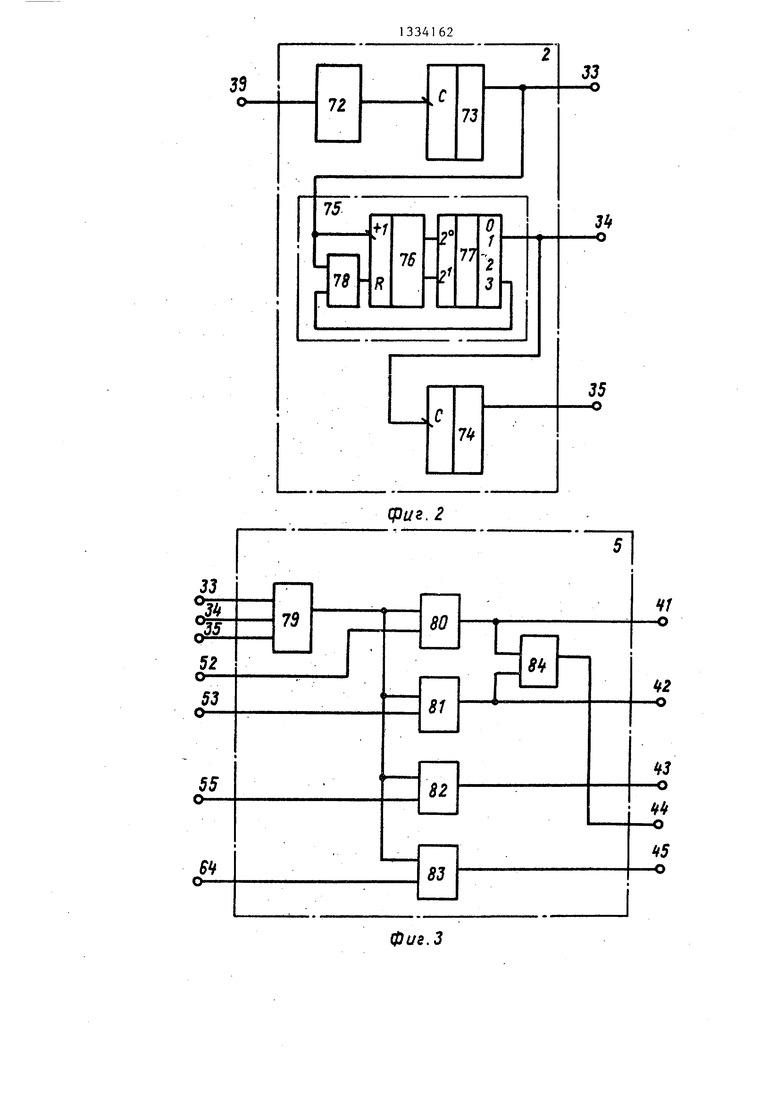

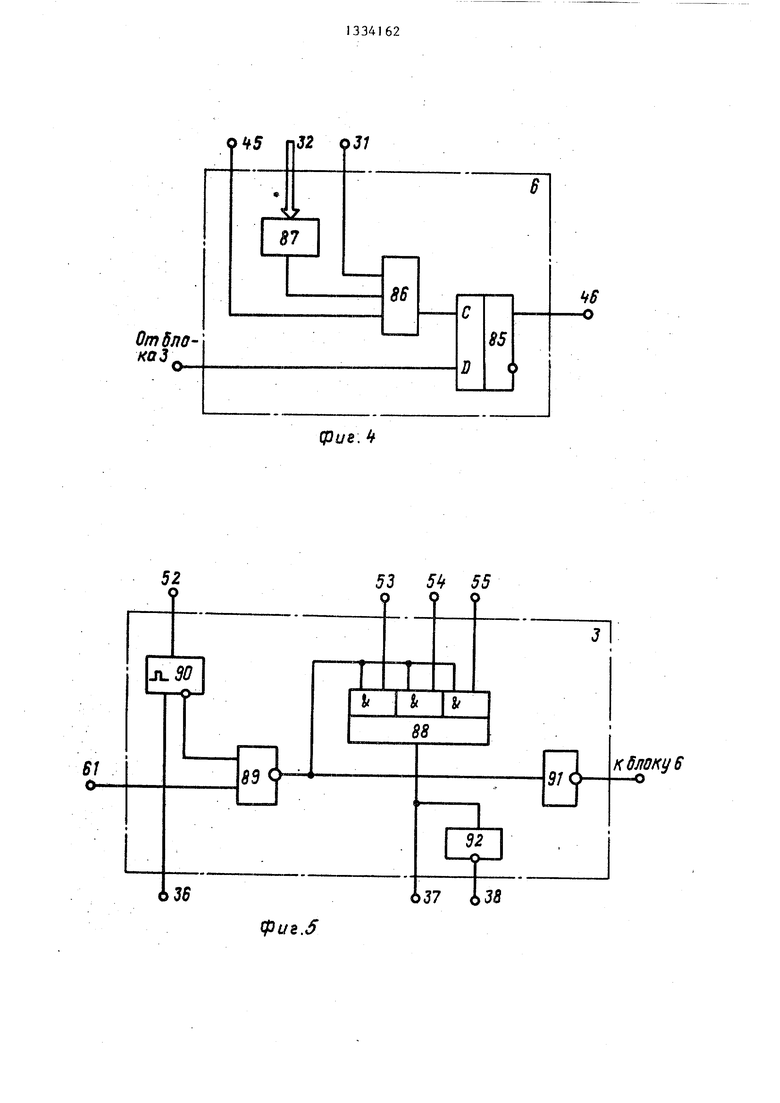

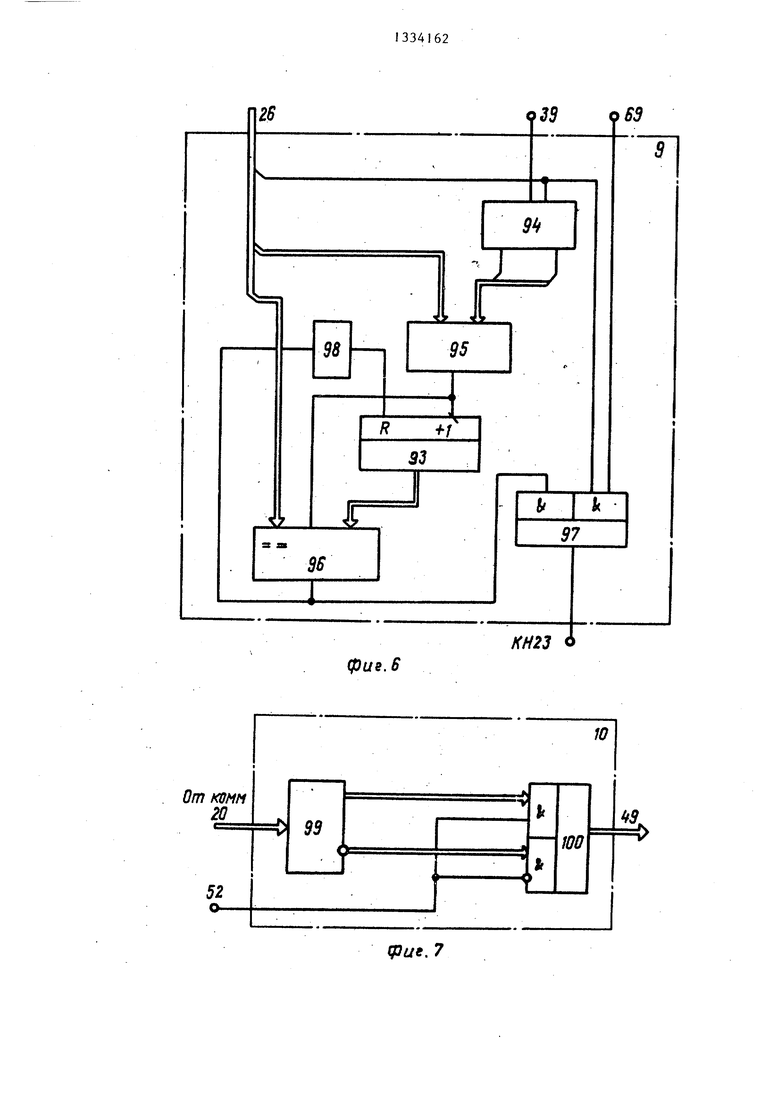

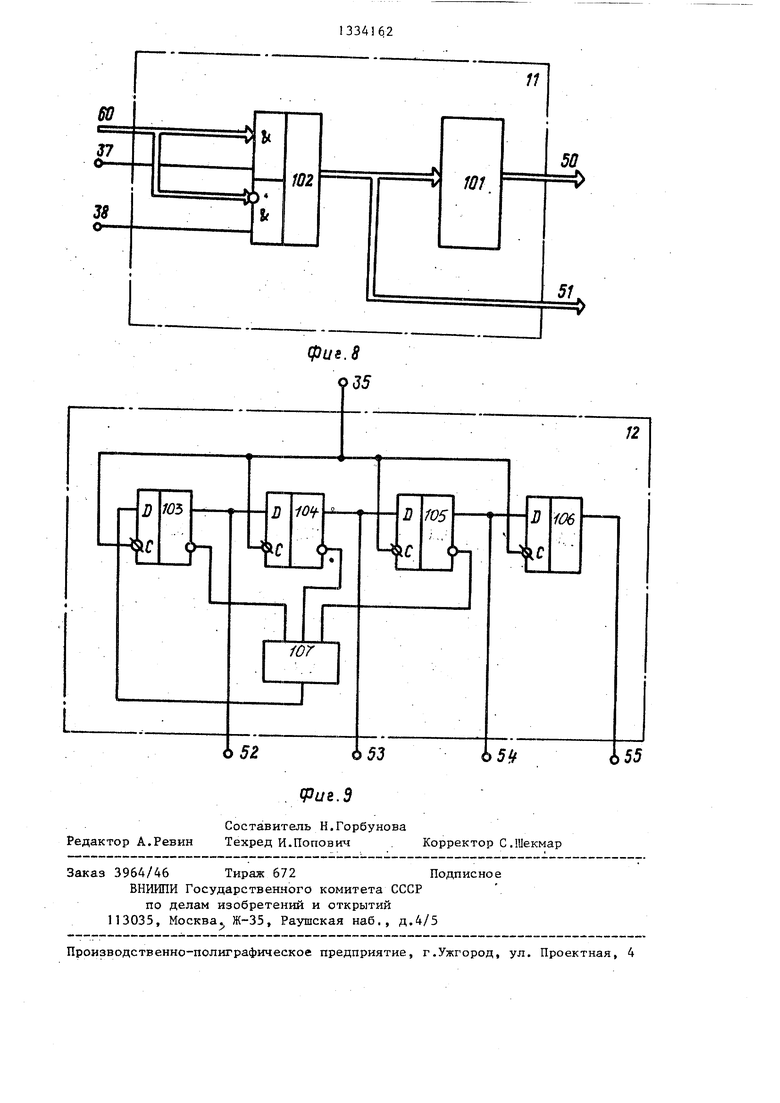

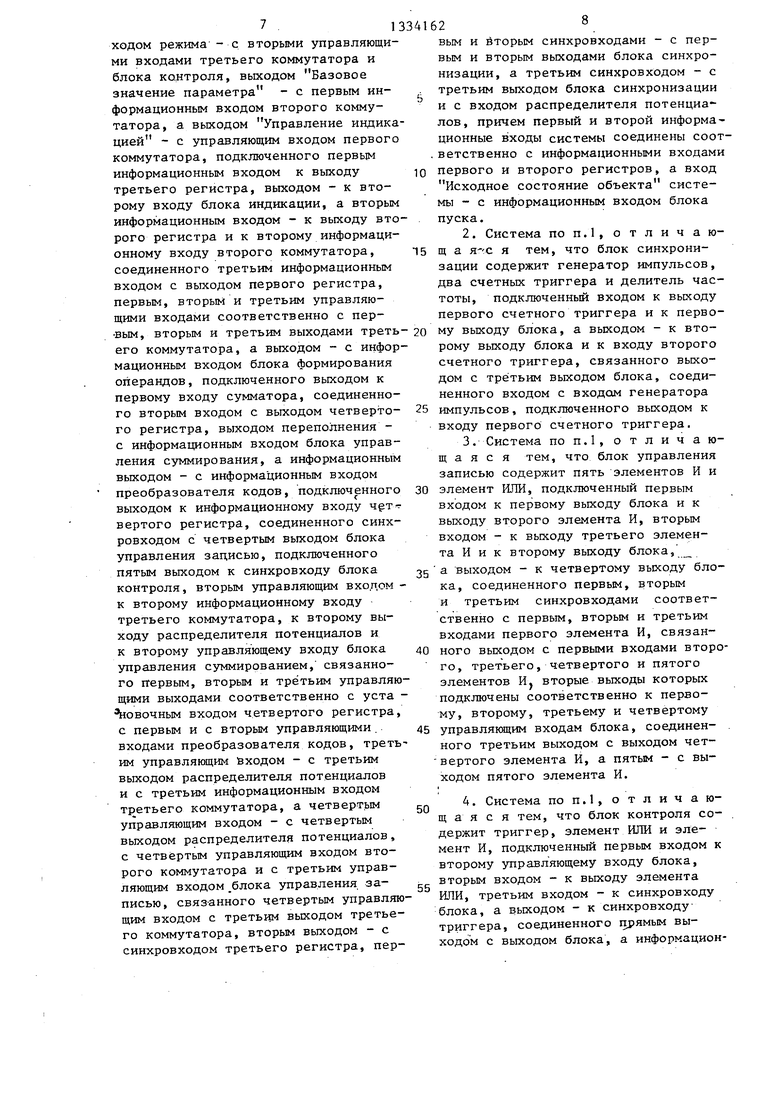

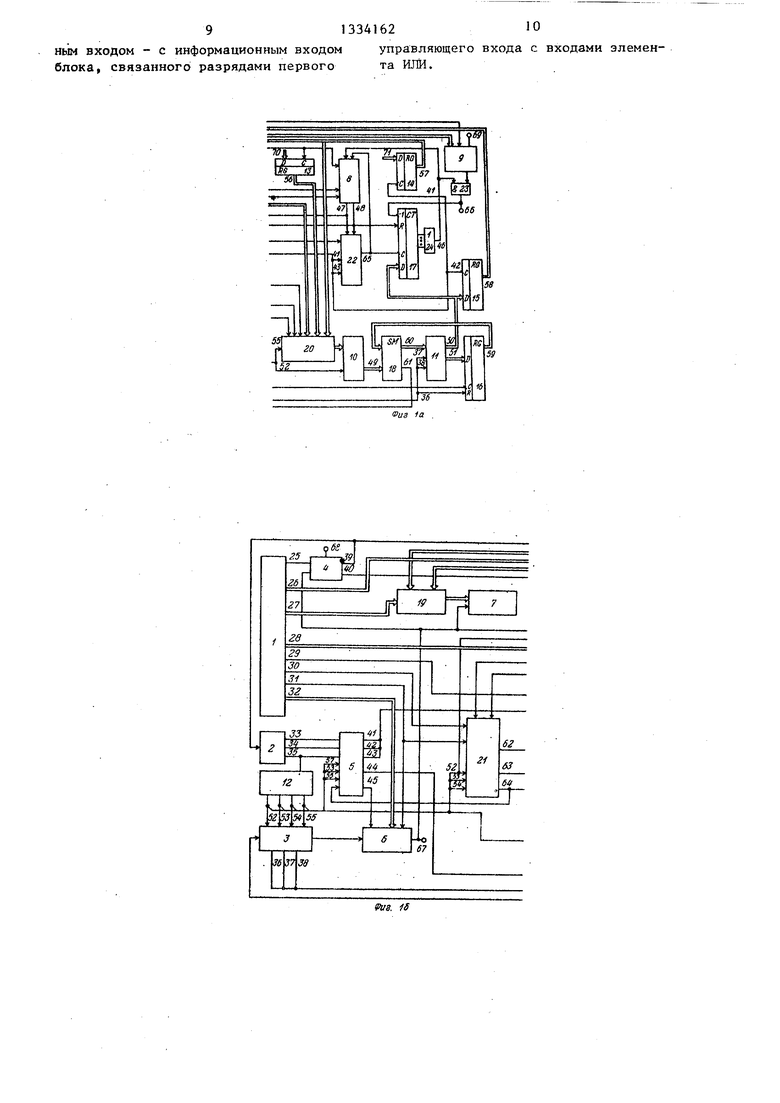

На фиг.1 (а и б) изображена функциональная схема предлагаемой системы; на фиг.2 - схема блока синхронизации; на фиг.З - схема блока управления записью; на фиг.4 - схе- ма блока контроля; на фиг.5 - схема блока управления суммированием; на фиг.6 - схема блока формирования импульсов; на фиг.7 - схема блока формирования операндов; на фиг.8 - схема преобразования кодов; на фиг.9 - схема распределителя потенциалов .

Система содержит блок 1 задания режима, блок 2 синхронизации, блок 3 управления суммированием, блок 4 пуска, блок 5 управления записью, блок 6 контроля, блок 7 индикации, блок 8 триггеров, блок 9 формирования импульсов, блок 10 формирования операн дов, преобразователь 1 кодов, распределитель 12 потенциалов, первый регистр (регистр заданного значения) 13, второй регистр (регистр текущего значения) 14, третий регистр (регистр результата) 15, четвертьш регистр (регистр операнда) 16, счетчик 17 импульсов, сумматор 18, первый (первый коммутатор данных) 19, второй (второй коммутатор данных } 20, третий коммутатор сигналов ввода ) 21 и четвертый (коммутатор сигналов записи) 22 коммутаторы, элемент И 23 и элемент ИЛИ 24, Позициями 25 - 65 обозначены входы и выходы блоков системы,66 - управляющий выход системы, 67 - выход Отказ системы , 68 - вход Исходное состояние объекта, 69 Задание .импульсов, первый 70 и второй 7 ин- формационные входы системы,

Блок 2 синхронизации.содержит генератор 72 импульсов, первый 73 и второй 74 счетные триггеры, делитель 75 частоты, состоящий из счет- чика 76 импульсов, дешифратора 77 и элемента И 78,

Блок 5 управления записью содержит первый 79, второй 80, третий 81

0

5 О Q

622

четвертый 82 и пятый 83 элементы И и элемент ИЛИ 84,

Блок 6 контроля содержит триггер 85, элемент И 86 и элемент ИЛИ ,

Блок 3 управления суммированием содержит коммутатор 88, элемент И- НЕ 89, одновибратор 90, первый 91 и второй 92 элементы НЕ,

Блок 9 формирования импульсов содержит счетчик 93 импульсов, генератор 94 импульсов, мультиплексор 95, элемент 96 сравнения, коммутатор 97 и элемент 98 задержки.

Блок 10 формирования операндов содержит преобразователь 99 кода и коммутатор 100,

Преобразователь 11 кодов содержит преобразователь 101 и коммутатор 1 02,

Распределитель 12 потенциалов содержит первый ЮЗ, второй 104, третий 105 и четвертый 106 триггеры и элемент И 107,

Система работает следующим образом.

Система осуществляет вьщачу управляющих сигналов на объект в зависимости от его состояния - кода текущего значения параметра К, объекта, базового значения параметра К (первого эталона), определяющего исходное смещение контролируемого 5 параметра и заданного значения этого параметра К,, Система может работать в трех режимах: в режиме абсолютных значений (A3); в режиме приращений (ПР); в режиме возврата в абсолютный нуль (ВА),

Основным режимом работы системы является режим абсолютных значений (A3). В этом режиме выполняются слё- дующие операции:

1,Вводится значение кода К,

2,Производится сравнение К и К, и вычисляется отклонение текуще- г.о значения от базового:

К,, К,- Kg.

3,Осуществляется сравнение вели0

5

чин

КГБ и к

- максимально возможного значения контролируемого параметра. Если Кт5 Кд, то фиксируется отказ объекта и производится останов системы. Если ; К, то выполняется следующая операция,

4,Производится сравнение К. и вычисляется отклонение текущего базового значения от заданного:

Т6 и Кз

К - - Kj.

10

15

20

25

5. Формируется последовательность импульсов, число которых пропорционально величине JK.5

Операции 1 - 5 могут повторяться многократно.

В режиме абсолютных значений (A3) система работает следующим образом,

В исходном состоянии все элементы памяти обнулены. Блок 1 задания режима, на выходе 26 задает код управления параметрами импульсов, формируемых блоком 9, а на выходе 28 - код Kg. Единичный сигнал также выдается на выходе 31 и одном из выходов 32.

По сигналу пуска с выхода 25 блок 4 пуска (в случае нахождения объекта в исходном состоянии, о чем сви- детельствует единичный сигнал на входе 68) формирует потенциальный и импульсный сигналы на выходах 39 и 40 соответственно. По сигналу с выхода 39 запускается блок 2 синхронизации и генератор 94 блока 9. Импульсным сигналом с выхода 40 блока 4 пуска в регистр 13 записывается код Kj и устанавливается в единичное состояние соответствующий триггер блока 8 триггеров. .

На выходах 33 - 35 блока 2 синхронизации появляются последовательности синхроимпульсов, поступающих в блок 5 и распределитель 12. Распределитель 12 потенциалов формирует 35 последовательности сигналов на выходах 52 - 55, по которым вьшолняют- ся операции 1-4.

В первом такте осуществляется:

обнуление регистра 16.сигналом с выхода 36 блока 3 управления суммированием;

установка в единичное состояние . триггера блока 8 триггеров;

запись кода К в регистр 14 и регистр 16, причем код К., заносится в регистр 16 по цепи: регистр 14 - коммутатор 20, блок 10 формирования операнда (в прямом коде), сумматор 18, преобразователь 11 (в прямом ко- 50 де с избытком три).

Во втором такте вьшолняе.тся операция вычисления К . Для этого код Kg через коммутатор 20 и блок 10 формирования операнда поступает в сум- 5 матор 18 J где осуществляется операция Kg- Kg. Результат вычисления через блок формирования резуль0

5

0

5

5

0

5

тата заносится в коде с избытком три в регистр 16 и в двоично-десятичном коде в регистр 15 по импульсам, формируемым на выходах 44 и 42 блока 5 управления записью соответственно.

В третьем такте осуществляется проверка условия К. . Для этого код Кд, задаваемый в коммутаторе 20, через блок 10 подается в сумматор 18, где производится вычисление разности КТБ К,

Если , то на выходе 61 сумматора 18 появляется сигнал переполнения, которьш проходит через блок 3 управления суммированием и по импульсу с выхода 45 блока 5 управления записью фиксируется блоком 6 контроля и на выходе 46 этого блока выдается единичный сигнал, которым производится останов системы. Блок 7 индикации сигнализирует об этом оператору.

Если , то сигнал на выходе 61 равен нулю и система переходит к реализации следующей операции.

В четвертом такте производится операция вычисления JK Kj. Для этого код К с выхода 56 регистра 13 через коммутатор 20 проходит через блок 10 формирования операндов в сумматор 18, где определяется величина 4К. По импульсу с выхода 43 блока 5 управления записью коммутатор 22 формирует сигнал записи кода дК в счетчик 17 и установки соответствующего состояния в блоке 8 триггеров. В результате появляется единичный сигнал на выходе 67 элемента РШИ 24 и разрешается поступление импульсов с выхода блока 9 формирования импульсов через элемент И 23 на управляющий выход 66 системы и счетный вход счетчика 17.

После того, как на выход 66 будет вьщано L jb К импульсов ( ft - коэффициент пропорциональности ),счетчик 17 обнуляется, запрещая вьщачу импульсов и устанавливая в соответствующее состояние блок 8 триггеров.

После поступления единичного сигнала на вход 68 блок 4 пуска производит останов системы.

Отличие режима приращений (ПР) от режима абсолютных значений (A3) состоит в том, что код jK формирует- ся в виде

дК Ко ,

поэтому в первом - третьем таксах обработка контрольной информации не производится, а в четвертом такте по сигналу с выхода 55 через коммутатор 20 передается код Kj из регистра 13, который импульсом на выходе 43, проходящим через коммутатор 22, записывается в счетчик 17.

В режиме возврата в абсолютный нуль (ВА) код AV. определяется кодом Кр без учета базового и заданного значений:

4К К,.

В этом случае в первом.такте производится занесение кода Кр в счетчик 17,

Таким образом, использование предлагаемой системы позволяет осуществлять контроль и управление объектом контроля в различных режимах путем сравнения значения контролируемого параметра (или без сравнения) с несколькими эталонами.

Повьшение производительности и достоверности контроля достигается на основе оперативного учета состояния объекта; обеспечения возможности сравнения с несколькими эталонами; формирования управляющих сигналов в соответствии с. результатами сравнения и обработки контрольной информации и контроля исходного состояния .объекта и количественной оценки значений контролируемого параметра путем введения вьпиеуказанной совокуп- ности конструктивных признаков.

Формул

изобретения

1. Система для контроля и управления, содержащая блок задания режима, соединенный пусковь№1 выходом с первым управляющим входом блока пуска, подключенного первым выходом к входу блока синхронизации,, вторым- выходом - к синхровходу первого регистра, а вторым управляющим входом - к первому входу блока индикации, к выходу системы Отказ системы, и к выходу блока контроля, соединенного первым управляюп.;им входом с выходом режимов блока задания режима, а информационньм входом - с выходом переполнения блока управления суммированием, распределитель потенциалов , соединенный первым выходом с упрагзлякщим входом блока, формиро10

334162

вания операндов, и блок управления записью, подключенный первым выходом к синхровходу второго регистра, о т- личающаяся тем, что, с целью повьппения оперативности и достоверности контроля, в нее введены преобразователь кодов, блок триггеров, третий и четвертый регистры, счетчик импульсов, сумматор, четыре

15

20

25

30

35

40 .

-.. .

45.

50

«5

коммутатора, элемент И, элемент ИЛИ и блок формирования импульсов, подключенный первым управляющим входом к выходу управления импульсными последовательностями блока задания режима, вторым управляющим входом - к первому выходу блока пуска, информационным входом - к входу Задание импульсов системы, а выходом - к первому входу элемента И, связанного вторым входом с выходом элемента ИЛИ и с первым управляющим входом блока триггеров, а выходом - с управляющим выходом системы и с вычитающим входом счетчика импульсов, подключенного разрядными выходами к входам элемента ИЛИ, информационным входом - к информационному входу третьего регистра и к первому выходу преобразователя кодов, установочным входом - к первому выходу блока триггеров и к первым управляющим входам третьего

и четвертого коммутаторов, а синхро- входом - к выходу четвертого коммутатора и к второму управляющему входу блока триггеров, соединенного третьим и четвертым управляющими входами соответственно с вторым выходом блока пуска и выходом блока контроля, синхровходом: - с перввм выходом распределителя потенциалов, с первым информационным входом третьего коммутатора, с. первым управляющим вхо- ; дом блока управления записью и с первым управляющим входом блока управления суммированием, а вторым выходом - с вторым управляющим входом третьего коммутатора и с вторым управляющим входом четвертого коммутатора, подключенного первым информационным входом к первому выходу блока управления записью, вторым информационным входом - к третьему выходу блока управления записью, а третьим управляющим входом - к первому выходу режима блока задания ре- жима. Связанного вторым выходом режи- ;ма с третьим управля рщим входом третьего коммутатора, третьим Bjy

1 1

ходом режима - с вторыми управляющими входами третьего коммутатора и блока контроля, выходом Базовое значение параметра - с первым информационным входом второго коммутатора, а выходом Управление индика цией - с управляющим входом первого коммутатора, подключенного первым информационным входом к выходу третьего регистра, выходом - к второму входу блока индикации, а вторым

информационным входом - к выходу ВТО

рого регистра и к второму информационному входу второго коммутатора, соединенного третьим информационньм входом с выходом первого регистра, первым, вторым и третьим управляющими входами соответственно с первым, вторым и третьим выходами треть его коммутатора, а вьпсодом - с информационным входом блока формирования операндов, подключенного вьпсодом к первому входу сумматора, соединенного вторым входом с выходом четвертого регистра, выходом переполнения - с информационным входом блока управления суммирования, а информационным выходом - с информационным входом преобразователя кодов, подключенного выходом к информационному входу чрт вертого регистра, соединенного синх- ровходом с четвертым выходом блока управления задисью, подключенного пятым выходом к синхровходу блока контроля, вторым управляющим входом - к второму информационному входу третьего коммутатора, к второму выходу распределителя потенциалов и к второму управляющему входу блока управления суммированием, связанного ггервым, вторым и третьим управляющими выходами соответственно с уста - %овочньм входом четвертого регистра, с первым и с вторым управляющими.. входами преобразователя кодов, третьим управляющим йходом - с третьим выходом распределителя потенциалов и с третьим информационным входом третьего коммутатора, а четвертьм управляющим входом - с четвертым выходом распределителя потенциалов, с четвёртым управляющим входом второго коммутатора и с третьим управляющим входом блока управления записью, связанного четвертьм управляющим входом с третьим выходом третьего коммутатора, вторым выходом - с синхровходом третьего регистра, пер

5

34162«

вым и вторым синхровходами - с первым и вторым выходами блока синхронизации, а третьим синхровходом - с третьим выходом блока синхронизации и с входом распределителя потенциалов, причем первый и второй информа ционные входы системы соединены соот- .ветственно с информационными входами 10 первого и второго регистров, а вход Исходное состояние объекта системы - с информационным входом блока пуска.

2.Система поп.1, о тлич а ю- 15 щ а я- С я тем, что блок синхронизации содержит генератор импульсов, два счетных триггера и делитель частоты, подключенный входом к выходу первого счетного триггера и к перво20 му выходу блока, а выходом - к второму выходу блока и к входу второго счетного триггера, связанного выходом с третьим выходом блока, соединенного входом с входам генератора 25 импульсов, подключенного выходом к входу первого счетного триггера.

3.Система поп.1, о тлич а ю- щ а я с я тем, что блок управления записью содержит пять элементов И и

30 элемент ИЛИ, подключенный первым входом к первому выходу блока и к выходу второго элемента И, вторым входом - к выходу третьего элемента И и к второму выходу блока,

35 а выходом - к четвертому выходу блока, соединенного первым, вторым и третьим синхровходами соответственно с первым, вторым и третьим входами первого элемента И, связан40 ного выходом с первыми входами второго, третьего, четвертого и пятого элементов И, вторые выходы которых подключены соответственно к первому, второму, третьему и четвертому

45 управляющим входам блока, соединенного третьим выходом с выходом чет- вертого элемента И, а пятым - с выходом пятого элемента И.

50

55

4. Система поп.1, отличающаяся тем, что блок контроля со- держит триггер, элемент ИЛИ и элемент И, подключенный первым входом к второму управляющему входу блока, вторым входом - к выходу элемента ИЛИ, третьим входом - к синхровходу блока, а выходом - к синхровходу триггера, соединенного прямым выходом с выходом блока, а информацион9133416210

HbiM входом - с информационным входом управляющего входа с входами элемен- блока, связанного разрядами первого та ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1287161A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для имитации объекта контроля | 1984 |

|

SU1188743A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

| Устройство для синхронизации вычислительной системы | 1985 |

|

SU1684785A1 |

| Устройство для отладки вычислительной системы | 1986 |

|

SU1336015A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано в качестве системы контроля и управления нижнего уровня в сп ециализированных -программных контрольно-проверочных и управляющих комплексах для АСУТП. Цель изобретения - повьшение оперативности и достоверности контроля. Цель достигается за счет оперативного учета состояния объекта и автоматического формирования в соответствии с ним управляющих воздействий; учета исходного состояния объекта и формирования в зависимости от этого сигнала пуска, а также за счет количественного контроля параметров обыекта управления. Система для контроля и управления содержит блок задания режима, блок синхронизации, блок управления сум;мированием, блок пуска, блок управления записью, блок контроля, блок индикации, блок триггеров, блок формирования импульсов, блок формирования операндов, преобразователь кодов распределитель потенциалов, четыре регистра, счетчик импульсов, сумма;тор, первый, второй, третий и четвертый коммутаторы, злемент И, злемент ИЛИ. 3 з.п.ф-лы,-.9 ил. § (Л

да

п

ш

б9

по

57 11

1в

к

66

55Р

4

го

г

17

2

15

58

ь

«#

SM6017

61

Я

п S9

Фаз 1ц

33

:j«

35

73

52 о-

53

55

Btt

(pus. 2

Г E

8fy

41 -о

«2 о

43 -о

fit -о

83

«5 -о

фиг.З

J2 031

Д7

87

Отбло- °

52 о

КЙ

86

6 -о

S5

53 5 55 о о о

i/ &

S/

61 ь

кдлокуб -ю

6J5

fJpLfe.S

6J7 6Jfi

5-

фие.6

(Рие.7

652

Редактор А.Ревин

, fpus.9

Составитель Н.Горбунова

Техред И.Попович . Корректор С.Шекмар

Заказ 3964/46 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва., Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

| Устройство для контроля дискретных объектов управления | 1977 |

|

SU690499A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля схем цифровых вычислительных машин | 1977 |

|

SU693384A2 |

Авторы

Даты

1987-08-30—Публикация

1985-09-30—Подача