S

ч

L

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретное устройство синхронизации | 1979 |

|

SU786034A1 |

| Формирователь сложного сигнала с частотной и частотно-фазовой манипуляцией | 1982 |

|

SU1136323A1 |

| УСТРОЙСТВО для ПРИЕМА ШИРОКОБАЗОВЫХ СИГНАЛОВ | 1973 |

|

SU363183A1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Имитатор дискретного канала связи | 1981 |

|

SU964651A2 |

| Устройство тактовой синхронизациии РЕгЕНЕРАции | 1979 |

|

SU809620A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1265769A1 |

ДИСКРЕТНОЕ УСТРОЙСТВО СИНХРОНИЗАЦИИ по авт. св. № 786034, отличающееся тем, что, с целью повьппения точности фазирования , введен дополнительный элемент И, причем выход элемента ИЛИ через дополнительный элемент И подключен к входу записи управляемого делителя, а к второму входу дополнительного элемента И подключен выход задакще го генератора.

СО

со

NS

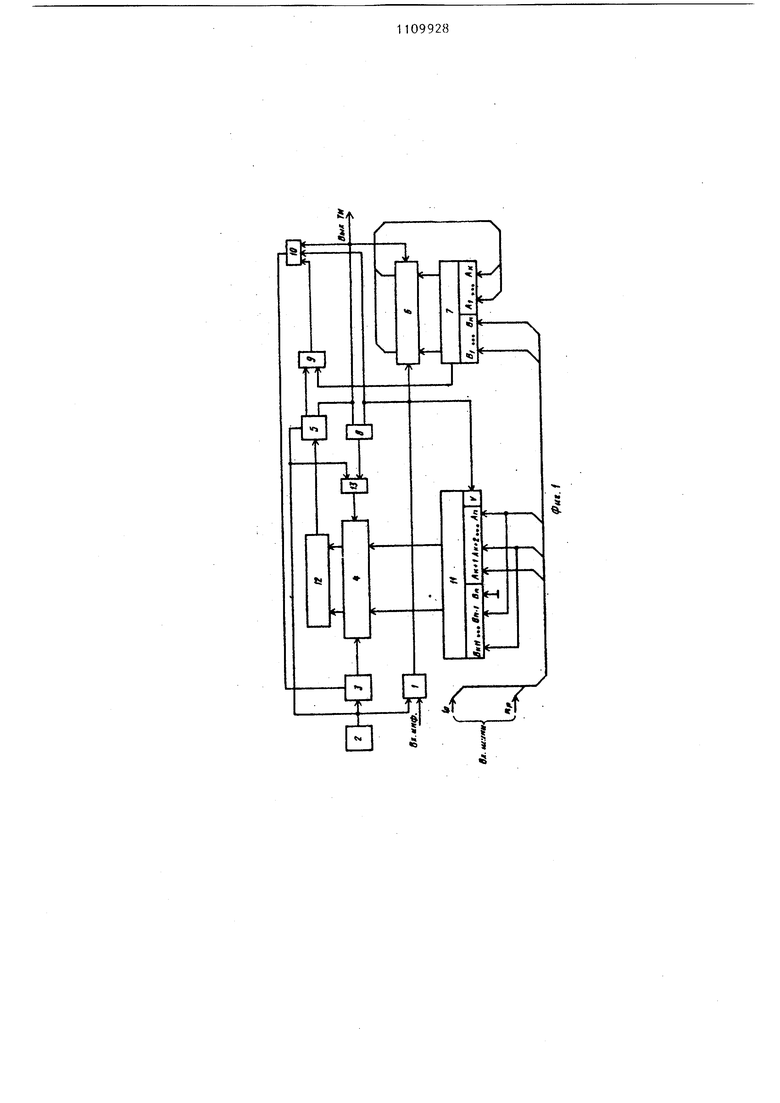

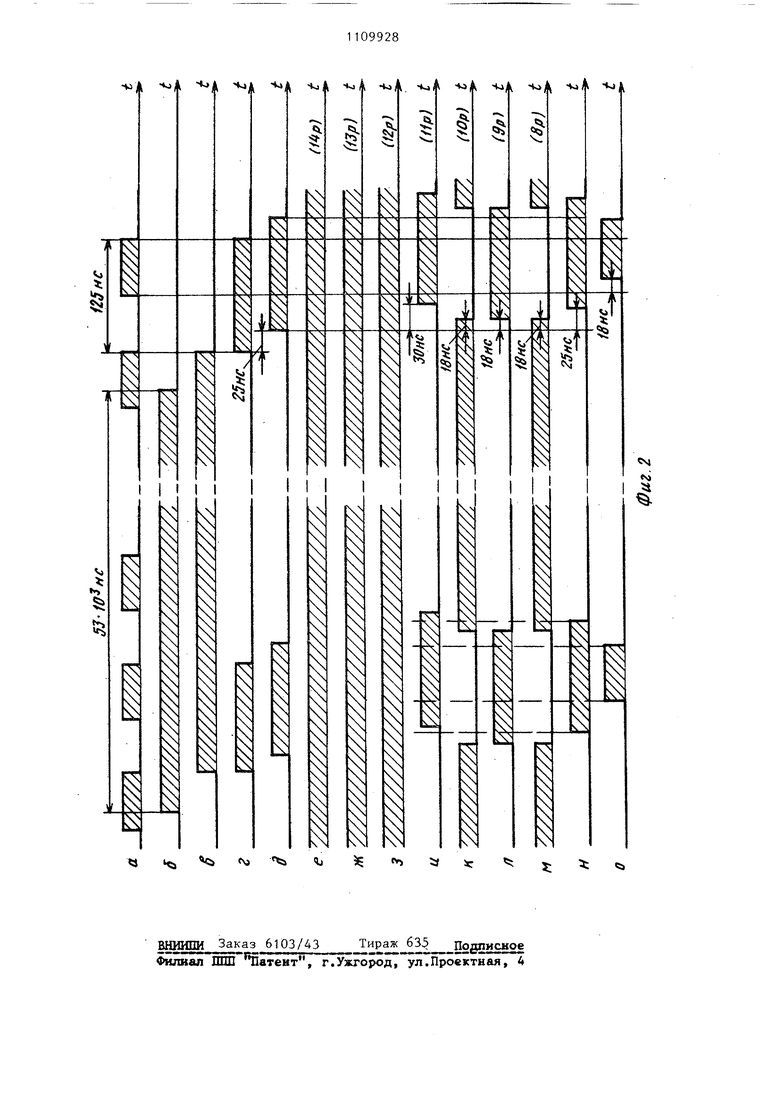

00 Изобретение относится к технике связи, а именно к технике передачи дискретных данных, и может быть исполь зовано в устройствах автоматической подстройки частоты для обеспечения синхронной работы в системах передачи - приема дискретной информации. По основному авт. св. № 736034 известно дискретное устройство синхронизации, содержащее блок выделения фронтом сигнала и последовательно соединенные задающий генератор, блок управления и управляемьш делитель, а также регистр задержки, регистр памяти, сумматор, элементы ИЛИ, И, ИЛИ-НЕ, коммутатор и дешифратор, выкод которого через последовательно соединенные регистр задержки, элементы И и ИЛИ-НЕ подключен к второму входу блока управления, причем выход блока вьщеления фронтов сигнала подключен к первому входу регистра памяти и соответственно через коммутатор и через элемент ИЛИ к соответствующим входам управляемого дели теля, выход которого подключен к входам дешифратора, причем выходы регистра памяти подключены к входам сумматора, первый выход которого под ключен к второму входу элемента И, а вторые выходы - к вторым входам регистра памяти, третий вход которого соединен с вторым входом элемента ИЛИ-НЕ, вторым входом элемента ИЛИ и вторым выходом регистра задержки, второй вход которого соединен с выходом задающего генератора и входом блока вьщеления фронтов сигнала, выход которого подключен к третьему входу элемента ИЛИ-НЕ, при этом вторые входы сумматора и коммутатора объединены Cl . Однако известное устройство имеет недостаточную точность фазирования с приходом входной посыпки инфор мации, так как время действия инверс ного кода полупериода тактовой пос(Ледовательности на вмходнах шинах ко мутатора определяется тем же импульсом, которым производится запись это го кода в управляемый делитель. Поэтому из-за разброса временных характеристик схемы коммутатора и элемента ИЛИ возможна запись ложной величи ны значения инверсного кода полупери ода тактовой последовательности в управляемый делитель. По этой причине импульс на выходе устройства може сместиться по времени на край элементарной посылки принимаемой информации, что повлечет за собой сбой синхронизации. Цель изобретения - повышение точности фазирования. Для достижения цели в дискретное устройство синхронизации, содержащее блок вьщеления фронтов сигнала и последовательно соединенные задающий генератор, блок управления и управляемый делитель, а также регистр задержки, регистр пaмяtи, сумматор, элементы ИЛИ, И, ИЛИ-НЕ, коммутатор и дешифратор, выход которого через последовательно соединенные регистр задержки, элементы И и ИЛИ-НЕ подключен к второму входу блока управления, причем вькод блока вьщеления фронтов сигнала подключен к первому входу регистра памяти и через коммутатор к соответствующим входам управляемого делителя и первому входу эле.мента ИЛИ, при этом выходы управляемого делителя подключены к входам деишфратора, а выходы регистра памяти подключены к входам сумматора, первый выход которого подключен к второму входу элемента И, а вторые выходы - к вторым входам регистра памяти, третий вход которого соединен с вторым входом элемента ИЛИ-НЕ, вторым входом элемента ИЛИ и вторым выходом регистра задержки, второй вход которого соединен с выходом задающего генератора и входом блока вьщеления фронтов сигнала, выход которого подключен к третьему входу элемента ИЛИ-НЕ, причем вторые входы сумматора и коммутатора объединены, введен дополнительный элемент И, причем выход элементу ИЛИ через дополнительньй элемент И подключен к входу записи управляемого делителя, а к второму входу дополнительного элемента И подключен выход задающего генератора. На фиг. 1 приведена структурная электрическая схема дискретного устройства синхронизации; на фиг. 2 временные диаграммы, поясняющие его работу. Дискретное устройство синхронизации содержит блок 1 вьщеления фронтов сигнала, задающий генератор 2, блок 3 управления, управляемый делитель 4, регистр 5 задержки, регистр 6 памяти, сумматор 7, элемент ИЛИ 8, элемент И 9, элемент ИПИ-НЕ 10, коммутатор 11, дешифратор . 12 и дополнительный элемент И 13. Дискретное устройство синхронизации работает следующим образом. На входных шинах устанавливается двоичный код периода тактовой последовательности входной информации. Входной сигнал (фиг. 2б) поступает в блок 1 вьщеления фронтов сигнала, где осуществляется привязка информации к частоте задающего генератора 2 (фиг. 2а,в) и производится формирование импульсов, соответствую щих переднему и заднему фронтам посы лок принимаемого сигнала, для организации подсинхронизации устройства (фиг. 2г). С выхода блока 1 вьщеления фронтов сигнала (фиг. 2д) эти импульсы, несколько задержанные отно сительно импульсов (фиг. 2г), посту пают на вход V коммутатора 11 и эле мент ИЛИ 8 (величина задержки определяется элементами схемы блока 1 выделения фронтов сигнала). При этом на выходных шинах коммутатора 11 устанавливается инверсный код полупериода тактовой последовательности входной информации. Поскольку при формировании кода полупериода произ водится сдвиг кода периода на один разряд в сторону младшего только на время действия импульсов с выхода блока 1 вьщеления фронтов сигнала (фиг. 2д), то на выходных шинах ком мутатора 11 значение разрядов кода. разрядах 8-11 будет иметь импульсны характер (фиг. 2м,л,к,и) и эти импульсы задержатся относительно импульсов с. выхода блока 1 вьщеления фронтов сигнала (величина задержки определяется элементами схемы комму татора) , а значение разрядов кода в разрядах 12-14 будет иметь потен- циальный характер (фиг. 2з,ж,е). Импульс с выхода элемента ИПИ 8 (фиг. 2н) задерживается также относительно импульсов с выхода блока 1 выделения фронтов сигнала (фиг. 2д) на величину, определяемую элементом ИЛИ 8, а импульс, вьщеленный дополнительным элементом И 13 (фиг. 2о), хотя и задерживается относительно импульса с выхода задающего генератора 2 (фиг. 2а) на величину, определяемую дополнительным элементом И 13, однако находится по времени в площади импульсов разрядов параллельного кода, т.е. его передний фронт отстает от передних фронтов 8 импульсов параллельного кода, а задний фронт будет опережать- задние фронты импульсов параллельного кода (фиг. 2и,к,л,м,о). Этим импульсом (фиг. 2о) переписывается инверсный код полупериода тактовой последовательности входной информации в управляемьй делитель и импульс, сформи рованный на выходе устройства, по времени располагается практически в середине первого элементарного импульса входной информации. Дальнейшее соблюдение этого условия обеспечивает стабильность задающего генердтора 2 и путем исключения импульсов задающего генератора 2 на входе управляемого делителя А. Если производить запись кода полупериода в управляемый делитель 4 импульсом с выхода элемента ИЛИ 8 (фиг. 2н), как в известном устройстве, и если учесть, что запись производится по заднему фронту импульса, то в этом случае в управляемый делитель 4 запишется ложный код, а именно 1111101 вместо действительного значения 1111010, и первьй импульс, сформированный на выходе ycтpoйcтвa окажется смещенным в сторону опережения на край элементарного импульса входной информации, т.е. произойдет сбой синхронизации из-за неточности начальной установки фазы первого выходного импульса. Одновременно импульс с блока 1 вьщеления фронтов сигнала сбрасьгоает в ноль регистр 6 памяти и через элемент ИПИ-НЕ 10 поступает на блок 3 управления, где производится исключение одного импульса задающего генератора 2 на входе управляемого делителя 4. Таким образом, в управляемом делителе 4 устанавливается код, равный разности емкости управляв емого делителя 4 и инверсного кода половинного значейия периода. Далее подсчитывается количество поступающих эталонных импульсов и при достижении в управляемом делителе 4 значения кода, равного 11...101, на дешифраторе 12 вырабатывается импульс, который с выхода дешифратора 12 поступает на вход регистра 5 задержки. Сдвиг регистра 5 задержки производится импульсами задающего генератора 2. С выхода первого разряда регистра 5 задержки импульс поступает на выход устройства, располагается по времени практически в середине элементарной посылки принимаемой информации и переписывает по переднему фронту значение кода сумматора 7 в регистр 6 памяти, выходы которого соединены с одноименными входами А сумматора 7. При этом на выходе сумматора 7 появится результат сложения остатка Лt, подключенного к входам В, и значения кода, записанного в регистр 6 памяти. Этот же импульс поступает на элемент ИЛИ 8, т.е. производится аналогичная предыдущей запись в управляемый делитель 4 установленного на выходе коммутатора 11 кода, но соответствующего уже тактовой последовательности в дискретах задающего генератора 2. Этот же импульс поступает на элемент ИЛИ-НЕ 10, т.е. производится исключение одного импульса задающего генератора 2 на входе управляемого делителя 4. Импульс с последнего разряда регистра 5 задержки не проходит через элемент И 9, закрытый низким потенциалом с |выхода переноса .сумматора 7. Поскольку в процессе работы управляемого делителя 4 производится исключение импульса на его входе каждым выходным импульсом и выходной импульс дополнит льно задерживается на один дискрет задающего генератора 2, дешифратор 12 собирается на число 11...101 и выполняется с помощью ячейки совпадения на (k+1),...,п входов.

Последующие импульсы на выходе устройства появляются с опережением относительно действительного значения на величину остатка &t. Это рас со -ласование растет с каждым периодом, а при достижении или превышении значения дискрета задающего генера;тора 2 с сумматора 7 поступит сигнал переноса как разрешение на прохождение импульса с последнего разряда- регистра 5 задержки через элемент И 9 на элемент ИЛИ-НЕ 10. В результате исключается один импульс задающего генератора 2 на входе управляемого делителя 4. При этом обеспечивается синфазность выходных импульсов.

Разрешающий потенциал с выхода

переноса держится до появления импульса на выходе устройства, которьй перепишет значение кода на выходе ;сукпчатора 7 как остаток &t в регистр ;6 памяти, а на выходе сумматора 7 поле этого появится сумма ut + At и :снимется сигнал переноса. Следующее исключение импульса на входе управляемого делителя 4 произойдет, когда новая сумма превысит значение дискрета задающего генератора 2. Задержка импульсов относительно выходных импульсов выбирается, исходя из быстродействия работы сумматора 7 и регистра 6 памяти.

Таким образом, после начальной установки импульсы на выходе устройства смещаются в сторону опережения относительно действительного значения периода тактовой последовательности на величину не более чем дискрет задающего генератора.

Кроме того, дискретное устройство синхронизации обеспечивает работу с входными сигналами, имеющими большую скважность и разные номиналы пе-/ риода тактовой последовательности, как кратные, так и не кратные периоду задающего генератора в пределах емкости управляемого делителя.

Предлагаемое устройство обладает высокой точностью фазирования.

Vi Cxj 5

Ij

CM «s

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дискретное устройство синхронизации | 1979 |

|

SU786034A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-08-23—Публикация

1982-08-23—Подача