Изобретение относится к автоматике и вычислительной технике и может использоваться для поиска неисправностей в цифровых устройствах.

Целью изобретения является повышение достоверности контроля за счет исключения ложного инвертирования сигналов при наличии импульсных помех.

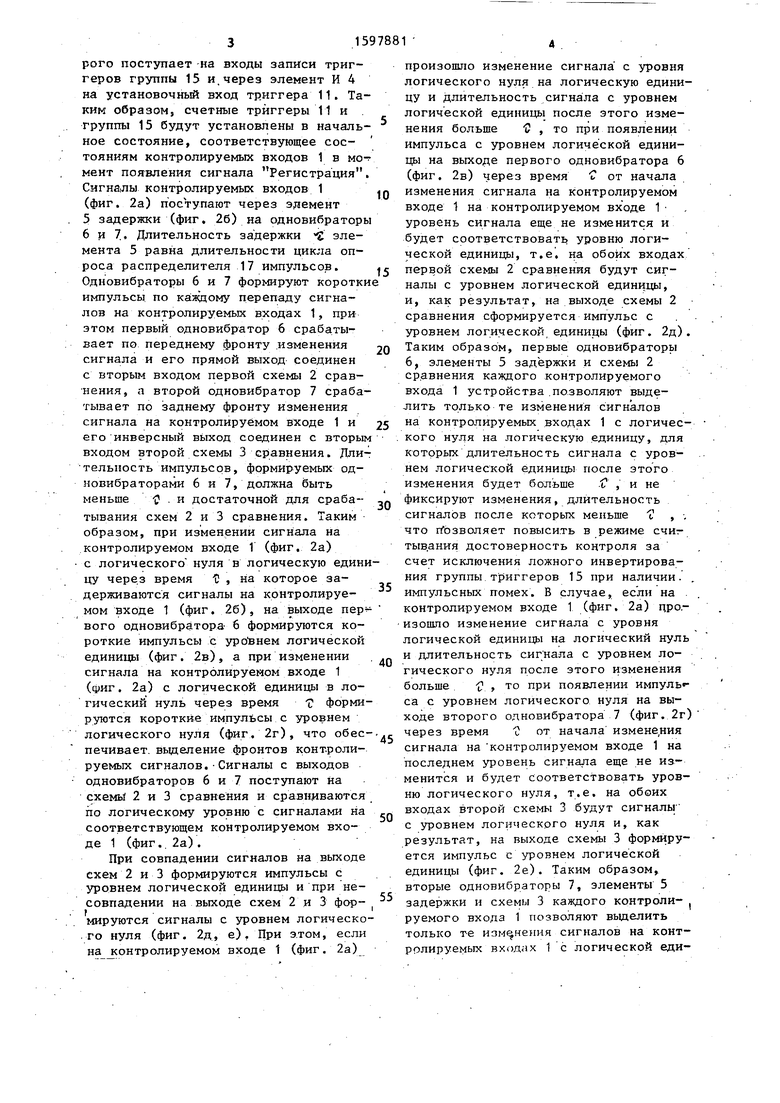

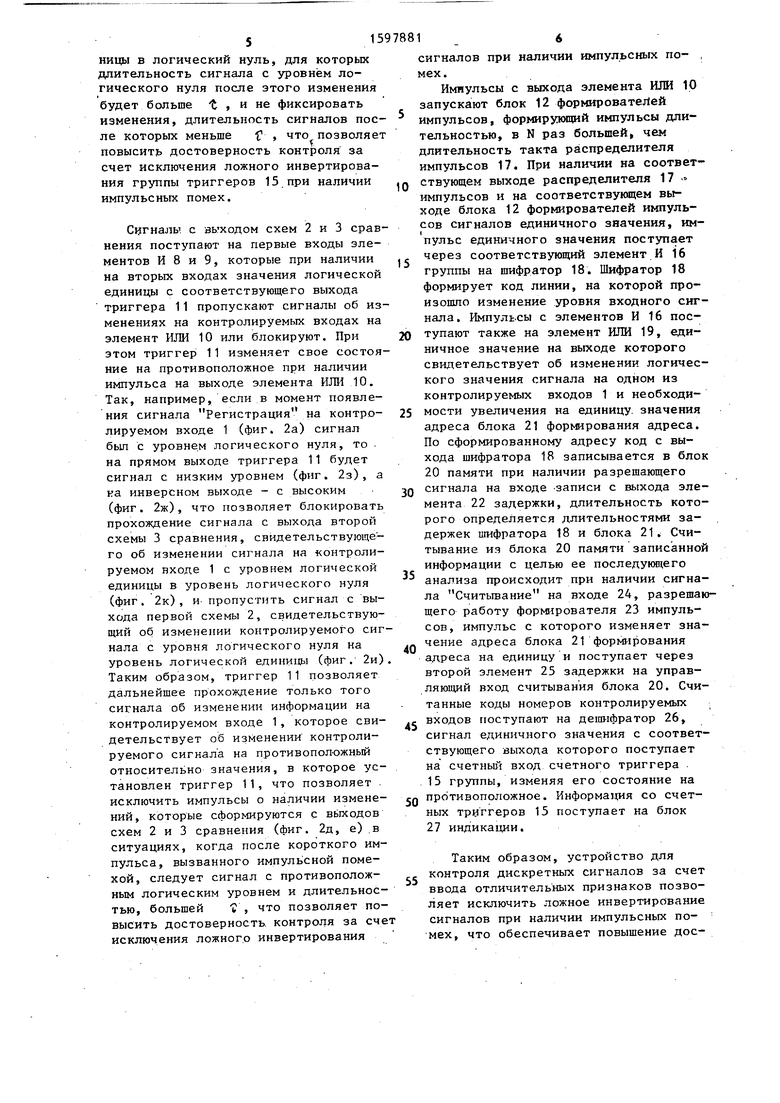

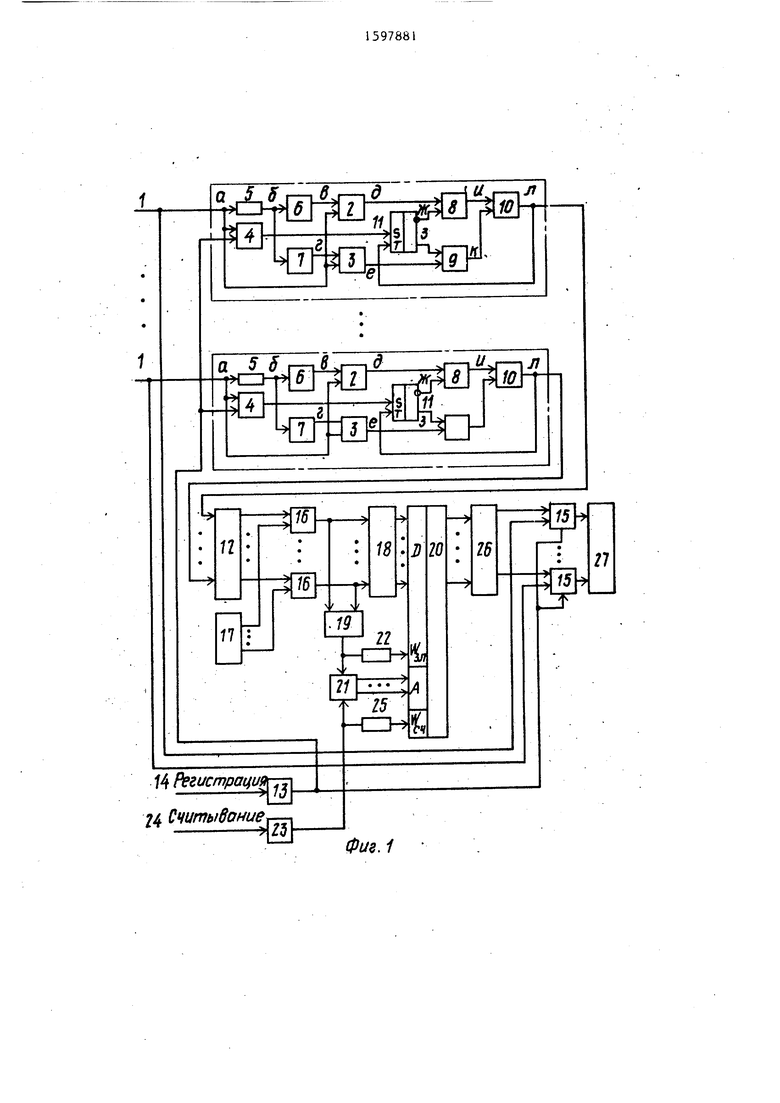

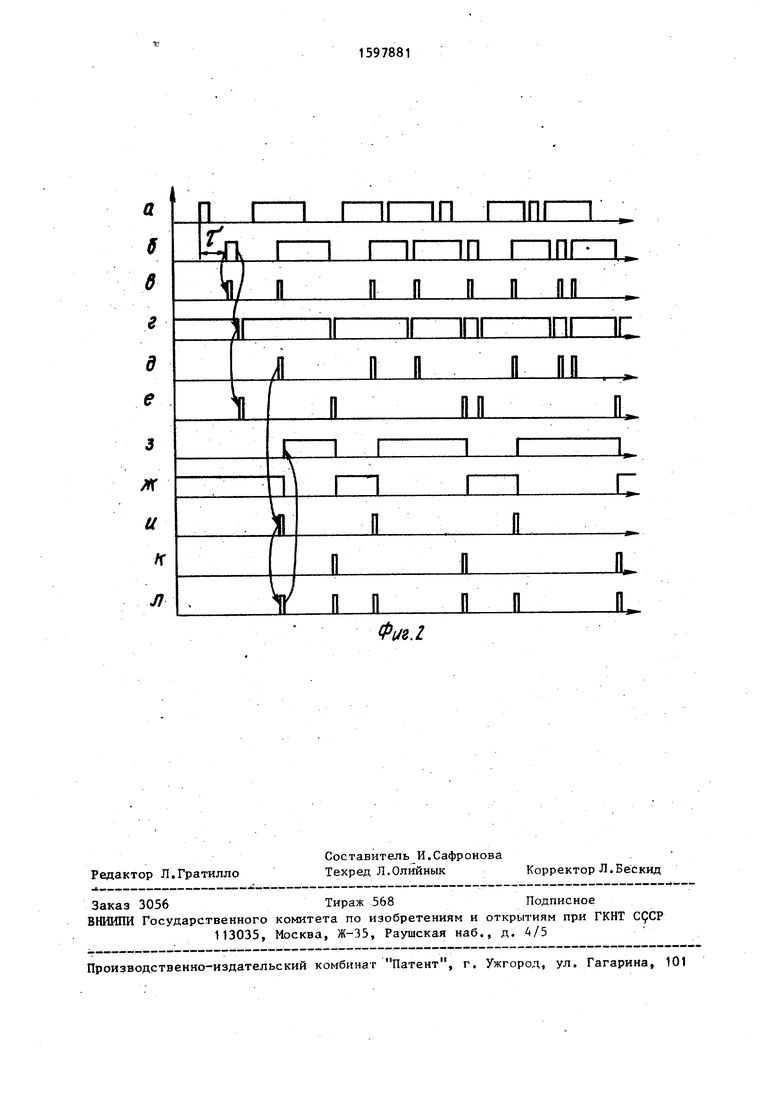

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - диаграмма его работы.

Устройство содержит группу 1 входов контролируемых сигналов, п каналов, включаюпщх первую схему 2 сравнения, вторую схему 3 сравнения, третий элемент И 4, элемент 5 з-адерж- ки, первый одновибратор 6, второй одновибратор 7, первый элемент И 8, второй элемент И 9, элемент ИЛИ 10, триггер 11, блок 12 формирователей импульсов, второй формирователь 13 импульсов, вход 14 задания режима регистрации устройства, группу 15 триггеров, группу 16 элементов И,

.распределитель 17 импульсов, шифратор 18, элемент ИЛИ 19, блок 20 памяти, блок 21 формирования адреса, первый элемент 22 задержки, первый формирователь 23 импульсов, вход 24 задания режима считывания, второй элемент 25 задержки, дешифратор 26, блок 27 индикации.

На фиг. 2 даны следующие обозначения: а - вход 1 контролируемых сигналов; б - выход элемента 5 задержки; в - выход первого одновибратора 6; г - выход второго одновибратора 7; д - выход первой схемы 2 сравнения; е - выход второй схемы 3 сравнения; ж - инверсный выход триггера 11; з - прямой вЬкод триггера 11; и - выход первого элемента И 8; к - выход второго элемента И 9; л - выход элемента ИЛИ 10.

Устройство работает следующим образом.

При появлении сигнала Регистрация на входе 14 запускается формирователь 13 импульсов, сигнал с котос

ф

ел

с:

СП

со

00 00

рого поступает на входы записи триггеров группы 15 и.через элемент И 4 на установочный вход триггера 11. Таким образом, счетные триггеры 11 и . группы 15 будут установлены в началь- ное состояние, соответствующее состояниям контролируемых входов 1 в момент появления сигнала Регистрация Сигналы контролируемых входов 1 (фиг. 2а) поступают через элемент

5задержки (фиг. 26) на одновибраторы

6и 7, Длительность задержки элемента 5 равна длительности цикла опроса распределителя 17 импульсов. Одновибраторы 6 и 7 формируют коротки импульсы по ка;зодому перепаду сигналов на контролируемых входах 1, при этом первый одновибратор 6 срабатывает по переднему фронту изменения сигнала и его прямой выход соединен

с вторым входом первой схемы 2 срав- нения, а второй одновибратор 7 срабатывает по заднему фронту изменения сигнала на контролируемом входе 1 и его инверсный выход соединен с вторым входом второй схемы 3 сравнения. Дпи- тельность импульсов, формируемых од- новибраторами 6 и 7, должна быть меньше С и достаточной для сраба- тывания схем 2 и 3 сравнения. Таким образом, при изменении сигнала на контролируемом входе 1 (фиг, 2а) с логического нуля в логическую единицу через время Ц , на которое задерживаются сигналы на контролируемом входе 1 (фиг. 26), на выходе пер вого одновибратора- 6 формируются короткие импульсы с уро внем логической единицы (фиг. 2в), а при изменении сигнала на контролируемом входе 1 (фиг. 2а) с логической единицы в логический нуль через время Т формируются короткие импульсы с уровнем логического нуля (фиг. 2г), что обес печивает. вьщеление фронтов контролируемых сигналов,Сигналы с выходов одновибраторов 6 и 7 поступают На схемы 2 и 3 сравнения и сравниваются по логическому уровню с сигналами на соответствующем контролируемом входе 1 (фиг.. 2а).

При совпадении сигналов на выходе схем 2 и 3 формируются импульсы с уровнем логической единицы и при несовпадении на выходе схем 2 и 3 фор- г .

мируются сигналы с уровнем логическо. го нуля (фиг. 2д, е), При э.том, если на контролируемом входе 1 (фиг. 2а)

.

е

Q „

5

произошло изменение сигнала с уровня логического нуля на логическую единицу и длительность сигнала с уровнем логической единицы после этого изменения больше и , то при появлении импульса с уровнем логической единицы на выходе первого одновибратора 6 (фиг. 2в) через время С от начала изменения сигнала на контролируемом входе 1 на контролируемом вх оде 1 уровень сигнала еще не изменится и будет соответствовать уровню логической единицы, т.е, на обоих входах первой схемы 2 сравнения будут сигналы с уровнем логической един1 ;цы, и, как результат, на выходе схемы 2 сравнения сформируется импульс с уровнем логической, единицы (фиг. 2д). Таким образом, первые одновибраторы 6, элементы 5 задержки и схемы 2 сравнения каждого контролируемого входа 1 устройства .позволяют выделить только те изменения сигналов на контролируемых входах 1 с логического нуля на логическую единицу, для которых длительность сигнала с уровнем логической единицы после этого изменения будет больше .( , и не фиксируют изменения, длительность сигналов после которых меньше с , , что п озволяет повысить в режиме счи- тыв.ания достоверность контроля за счет исключения ложного инвертирования группы триггеров 15 при наличии, импульсных помех. В случае, если на контролируемом входе 1 (фиг. 2а) цро- изошло изменение сигнала с уровня логической единицы на логический нуль и длительность сиг нала с уровнем логического нуля после этого изменения

больше

то при появлении импуль«

са с уровнем логического нуля на вы- хо;з,е второго одновибратора 7 (фиг. 2г) через время t от начала измене,ния сигнала на контролируемом входе 1 на последнем уровень сигна.па еще не изменится и будет соответствовать уровню логического нуля, т.е. на обоих входах второй схемы 3 будут сигналы с уровнем логического нуля и, как результат, на выходе 3 формируется импульс с уровнем логической единицы (фиг. 2е). Таким образом, вторые одновибраторы 7, элементы 5 задержки и схемы 3 каждого контроли- руемого входа 1 позволяют вьщелить только те изм неиня сигналов на контролируемых входах 1 с логической еди5159

ницы в логический нуль, для которых длительность сигнала с уровнем логического нуля после этого изменения будет больше t , и не фиксировать изменения, длительность сигналов после которых меньше f

что позволяет повысить достоверность контроля за счет исключения ложного инвертирования группы триггеров 15 при наличии импульсных помех.

20

25

30

Сигналы с выходом схем 2 и 3 сравнения поступают на первые входы элементов И 8 и 9, которые при наличии на вторых входах значения логической единицы с соответствующего выхода триггера 11 пропускают сигналы об изменениях на контролируемых входах на элемент ИЛИ 10 или блокируют. При этом триггер 11 изменяет свое состояние на противоположное при наличии импульса на выходе элемента ИЛИ 10. Так, например, если в момент появления сигнала Регистрация на контролируемом входе 1 (фиг. 2а) сигнал был с уровнем логического нуля, то . на прямом выходе триггера 11 будет сигнал с низким уровнем (фиг. 2з), а на инверсном выходе - с высоким (фиг. 2ж), что позволяет блокировать прохождение сигнала с выхода второй схемы 3 сравнения, свидетельствующего об изменении сигнала на контролируемом входе 1 с ypoBFieM логической единицы в уровень логического нуля (фиг. 2к), и пропустить сигнал с выхода первой схемы 2, свидетельствующий об изменении контролируемого сигнала с уровня логического нуля на уровень логической единицы (фиг. 2и). Таким образом, триггер 11 позволяет дальнейшее прохождение только того сигнала об изменении информации на контролируемом входе 1, которое свидетельствует об изменении контролируемого сигнала на противоположный относительно значения, в которое установлен триггер 11, что позволяет исключить импульсы о наличии изменений, которые сформируются с вьгходов схем 2 и 3 сравнения (фиг. 2д, е) ,в ситуациях, когда после короткого импульса, вызванного импульсной помехой, следует сигнал с противополож- ным логическим уровнем и длительностью, большей f , что позволяет повысить достоверность, контроля за счет исключения ложного инвертирования

и .Q ., CQ

35

40

0

5

0

сигналов при наличии импульсных по- , мех.

Имнульсы с выхода элемента ИЛИ 10 запускают блок 12 формирователей импульсов, формирующий импульсы длительностью, в N раз большей, чем длительность такта распределителя импульсов 17. При наличии на соответ- ствующем выходе распределителя 17 импульсов и на соответствующем выходе блока 12 формирователей импульсов сигналов единичного значения, импульс единичного значения поступает через соответствующий элемент И 16 группы на шифратор 18. Шифратор 18 формирует код линии, на которой произошло изменение уровня входного сигнала. Импульсы с элементов И 16 поступают также на элемент ИЛИ 19, единичное значение на выходе которого свидетельствует об изменении логического значения сигнала на одном из контролируемых входов 1 и необходимости увеличения на единицу, значения адреса блока 21 формирования адреса. По сформированному адресу код с выхода шифратора 18 записывается в блок 20 памяти при наличии разрешающего сигнала на входе -записи с выхода элемента 22 задержки, длительность которого определяется длительностями за- . держек шифратора 18 и блока 21. Считывание из блока 20 памяти записанной информации с целью ее последуюп1его анализа происходит при наличии сигнала Считьтание на входе 24, разрешающего работу формирователя 23 импульсов, импульс с которого изменяет значение адреса блока 21 формирования адреса на единицу и поступает через второй элемент 25 задержки на управляющий вход считывания блока 20. Считанные коды номеров контролируемых ., входов поступают на дешифратор 26, сигнал единичного значения с соответствующего выхода которого поступает на счетньй вход счетного триггера 15 группы, изменяя его состояние на CQ противоположное. Информация со счетных триггеров 15 поступает на блок 27 индикации.

35

40

Таким образом, устройство для контроля дискретных сигналов за счет ввода отличительных признаков позволяет исключить ложное инвертирование сигналов при наличии импульсных помех, что обеспечивает повышение достоверности контроля сигналов контролируемых входов.

Формулаизобретения

Устройство для контроля дискретных сигналов, содержащее блок питания, два элемента задержки, элемент ИЛИ, блок формирования адреса-, два формирователя импульсов, блок формирователей импульсов, блок индикации, распределитель импульсов, группу элементов И, шифратор, дешифратор, группу триггеров, причем выходы распределителя импульсов подключены к первым входам элементов И группы, выходы которых соединены с соответствующими входами элемента ИЛИ и входами шифратора, группа выходов которого соединена с группой информационных входов блока памяти, группа адресных входов которого соединена с группой выходов блока формирования адреса, первый и второй входы синхронизации которого соединены соответственно с выходом элемента ИЛИ и выходом пер- .вого формирователя импульсов, выходы элемента ИЛИ и первого формирователя импульсов через первый и второй эле- .менты задержки соединены соответственно с входаш записи и чтения.блока памяти, группа выходов которого соединена с группой входов дешифра- тора, выходы которого соединены со счетными входами соответствующих триггеров группы, информационные входы которых соединены с входами контролируемых сигналов устройства, входы записи триггеров группы соединены с выходом, второго формирователя импульсов, входы первого и второго формирователей импульсов являются

соответственно входами задания режимов считывания и регистрации устройства, выходы триггеров группы соединены с группой входов блока индикации, о тл и ч ающе е с я тем, что, с целью повышения достоверности контроля, выходы блока формирователей импульсов соединены с вторыми входами

Эилементов И группы, в устройство введены п каналов (п - число контролируемых сигналов), казкдый из которых содержит элемент задержки, три элемента И, элемент ИЛИ две схемы сравC нения, два одновибратора, триггер, причем в каждом канале информационный вход устройства подключен к первому входу первого элемента И и через элемент задержки к входам первого и втоQ рого одновибраторов, выходы которых соединены с первыми входами соответствующих схем сравнения, выходы которых соединены с первыми входами соответственно второго и третьего элемент

5 тов И, выходы которых подключены к входам элемента ИЛИ, выход которого соединен с тактовым входом, триггера и соответствуюш м входом блока формирователей импульсов, установочньй

0 вход триггера подключен к выходу первого элемента И, инверсный и прямой выходы триггера соединены с вторыми входами второго и третьего элементов И соответственно, выход второго формирователя импульсов соединен с вторым входом первого элемента И каждого канала, вход второго формирователя импульсов подключен к входу задания режима регистрации устройства, втол рые входы первой и второй схем сравнения каждого канала подключены к соответствующему информационному вхо- :ду устройства.

5

С

16

/ф

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дискретных сигналов | 1987 |

|

SU1499347A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Двухканальное устройство для акустико-эмиссионного контроля | 1988 |

|

SU1508140A1 |

| Логический анализатор | 1987 |

|

SU1506448A1 |

| Устройство для контроля знаний обучаемых | 1990 |

|

SU1758658A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1762280A2 |

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

Изобретение относится к автоматике и вычислительной технике и используется для поиска неисправностей в логических блоках. Целью изобретения является повышение достоверности контроля. В устройстве по каждому входу введены два одновибратора, две схемы сравнения, три элемента И, триггер, элемент ИЛИ, элемент задержки, что позволяет исключить ложное инвертирование сигналов при наличии импульсных помех. 2 ил.

п

п

Регистрация

24 Считывание

1

Фие.1

18

20

26

22

,1

| Устройство для контроля дискретных сигналов | 1987 |

|

SU1499347A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-10-07—Публикация

1988-10-25—Подача