Изобретение относится к вычислительной технике и может быть использовано в системсЭх технической диагностики .

Цель изобретения - упрогцение устройства .

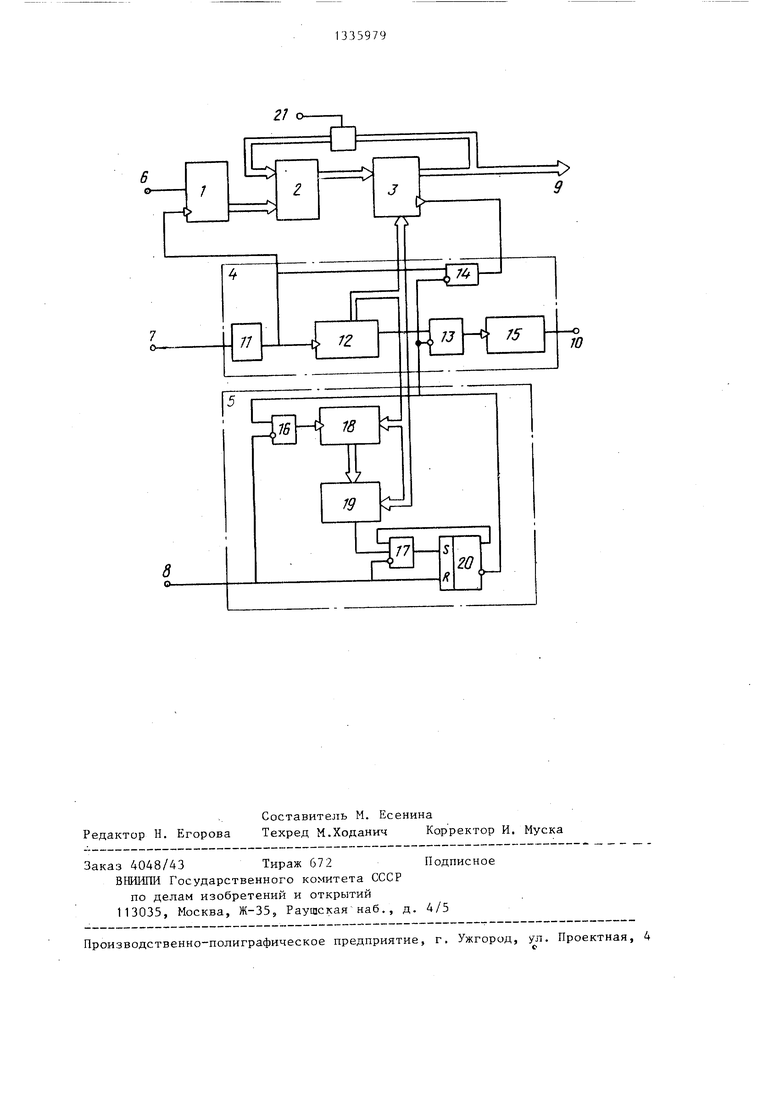

На чертеже представлена фу} кцио-. нальная схема арифметического устройства.

Арифметическое устройство содержит блок 1 сопряжения, сумматор 2, блок 3 памяти, блок 4 синхронизации и блок 5 управления, информационньш вход 6, вход 7 опорного сигнала, вход 8 блокировки, выход 9 результата и выход 10 готовности устройства. Блок 4 синхронизации содержит формирователь 11 импульсов, счетчик 12 адреса, элементы ЗАПРЕТ 13 и 14, счетчик 15 циклов Блок 5 управления содержит элементы ЗАПРЕТ 16 и 17, регистр 18 адреса, компаратор 19 и триггер 20, вход 21 сброса (подается на время считывания информации из блока 3 памяти), элемент ЗАПРЕТ. ,

Устройство работает следующим образом.

Исследуемый сигнал поступает на вход 6 блока 1 сопряжения, который представляет собой аналого-цифровой преобразователь, если идет обработка аналогового сигнала, или запоминающий регистр, если обрабатываемая информация поступает в цифровом виде. На вход 7 подается опорный сигнал. На практике опорный сигнал, например, может представлять сигнал с частотой, кратной частоте сигнала от датчика круговой частоты вращения исследуемого объекта, и формироваться умножителем частоты. При этом исследуемый сигнал представляет собой смесь частотных составляющих, кратных круговой а также помех и шумовых составляющих,

В Соответствии с управляющими сигналами счетчика 12 адреса обеспечивается запись последовательных отсчетов исследуемого сигнала в М ячеек блока 3 памяти, 1-й отсчет поступает в первую ячейку, 2-й отсчет - во вторую ячейку, М-й отсчет - в М-ю ячейку

Предполагается, что первоначально блок памяти обнулен.

М 1-й отсчет, суммируясь в блоке 2 с содержимым 1-й ячейки, вновь записывается в первую ячейку, М + 2-й отсчет, суммируясь в блоке 2 с содер0

5

жимым /-И ячейки, записывается во иторую ячейку и т.д.

Таким образом, обрабатывается К кусков реализации исследуемого сигнала, каждый из которых состоит из М последовательных отсчетов, причем К кратно степени двойки. По переднему фронту сигнала с формирователя 11 происходит выбор ячейки памяти и суммирование в блоке 2, а по заднему фронту - запись результата суммирования в ячейку.

Счетчик 12 адреса обеспечивает счет до М, после чего он обнуляется и обеспечивает запись в счетчик 15 циклов, который обеспечивает счет количества кусков реализаций. После за- счетчик 15 циклов вьщает на сигнал о готовности устрой5

0

5

0

5

0

5

полнения выход 10 ства.

Блок

5 управле}1ия обеспечивает блокирование синхронного накопления с момента поступления сигнала блокировки на вход 8 до момента снятия сигнала 8, но не раньше момента записи в следующую ячейку, считая с ячейки, в которую последней произошла запись к моменту поступления сигнала 8.

При отсутствии сигнала блокировки на входе 8 триггер 20 находится в нулевом состоянии. Элементы ЗАПРЕТ 13 и 14 разрешают прохождение сигналов записи и в регистр 15. Сигналы от компаратора 19 блокируются в элементе 17 .

При поступлении сигнала блокировки, который на практике может означать сигнал перегрузки предусилите- лей. или усилителей, через схему 16 происходит запись адреса последней ячейки блока 3 памяти, в которую была записана достоверная информация.

Триггер 20 устанавливается в единицу. Элементы 13 и 14 запрещают запись в блок 3 памяти и счетчик 15 циклов. Элемент 16 помогает избежать записи нового адреса в регистр 18, если сигнал блокировки будет сброшен, а затем установлен вновь до того, как в регистре 12 появится адрес ячейки, следующей после поступления первоначального сигнала блокировки.

После сброса сигнала блокировки компаратор 19 установит триггер 20 в исходное состояние, когда адрес в счетчике 12 совпадает .с адресом, запомненным в регистре 18. Устройство

будет продолжать накопление К кусков достоверт.пс реализаций.

Для считывания информации Из устройства достаточно подать тактовые сигналы на вход 7, на вход 6 - нулевой сигнал, на вход 21 - сигнал обнуления, по входу 8 - сбросить триггер 20.

Формула изобретения

Арифметическое устройство, содержащее сумматор, блок памяти и блок

управления, содержащий регистр адреса 5 второго элемента ЗАПРЕТ блока синхрои компаратор, первый информационный вход которого соединен с выходом регистра адреса, отличающееся тем, что, с целью упрощекия устройства, оно содержит блок со-20 RS-триггера соединен с инверсными

пряжения, элемент ЗАПРЕТ, блок синхронизации, содержащий формирователь импульсов, счетчик адреса, счетчик циклов, первый и второй элементы

входами первого и второго элементо ЗАПРЕТ блока синхронизации и прямы входом первого элемента ЗАПРЕТ бло управления, выход которого соедине

ЗАПРЕТ, блок управления содержит пер- с тактовым входом регистра адреса.

вый и второй элементы ЗАПРЕТ и КЗ-триггер, причем информационный вход устройства соединен с информационным входом блока сопряжения, синхровход которого соединен с выходом формирователя импульсов, счетным входом счетчика адреса и прямым входом первого элемента ЗАПРЕТ блока синхронизации, выход которого соединен с

входом управления считыванием/записью35 ПРЕТ и входом блокировки устройства, блока памяти, информационный вход вход формирователя импульсов соединен которого соединен с выходом суммато- с входом опорного сигнала устройства.

pa, первый и второй информационные входы которого соединены соответственно с выходом блока сопряжения и выходом элемента ЗАПРЕТ устройства, инверсный вход которого соединен с входом сброса устройства, прямой вход элемента ЗАПРЕТ устройства соединен с выходом результата устройства и выходом блока памяти, адресный вход которого соединен с информационным входом регистра адреса, вторым входом компаратора и выходом результата счетчика адреса, выход переполнения которого соединен с прямым вход ом втонизации, выход которого соединен со счетным входом счетчика циклов, выход которого соединен с выходом готовности устройства, инверсный выход

входами первого и второго элементов ЗАПРЕТ блока синхронизации и прямым входом первого элемента ЗАПРЕТ блока управления, выход которого соединен

с тактовым входом регистра адреса.

первый и второй прямые входы второго элемента ЗАПРЕТ блока управления соединены соответственно с выходом компаратора и прямым выходом RS-тригге- ра, S-вход которого соединен с выходом второго элемента ЗАПРЕТ блока управления, инверсный вход которого соединен с R-входом RS-триггера, инверсным входом первого элемента ЗАРедактор Н. Егорова

Составитель М. Есенина

Техред М.ХоданичКорректор И, Муска

Заказ 4048/43Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-ЗЗ, Раушская наб., д. 4/5

- - - --- -.- -- .-...- .

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Цифровой измеритель несимметричности сигналов | 1990 |

|

SU1725179A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1989 |

|

SU1841074A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Устройство для контроля и идентификации пользователя | 1991 |

|

SU1833902A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - упрощение устройства. Арифметическое устройство содержит блок управления,блок синхронизации, блок сопряжения,сумматор,блок памяти, , элемент ЗАПРЕТ. Изобретение предназначено для проведения синхронного с частотой опорного сигнала накопления информации и обеспечивает блокирование процесса накопления при поступлении сигнала блокировки. Накопленная информация при этом сохраняется, но процесс синхронного накопления возобновляется не сразу после снятия сигнала блокировки, а при попадании процесса в соответствующую фазу опорного сигнала, на которой поступил сигнал блокировки. 1 ил. с (Л оо со ел со -sj со

| Арифметическое устройство | 1973 |

|

SU525950A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-04—Подача