Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля различных дешифраторов.

Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности контроля дешифратора при изменении частоты входных кодов.

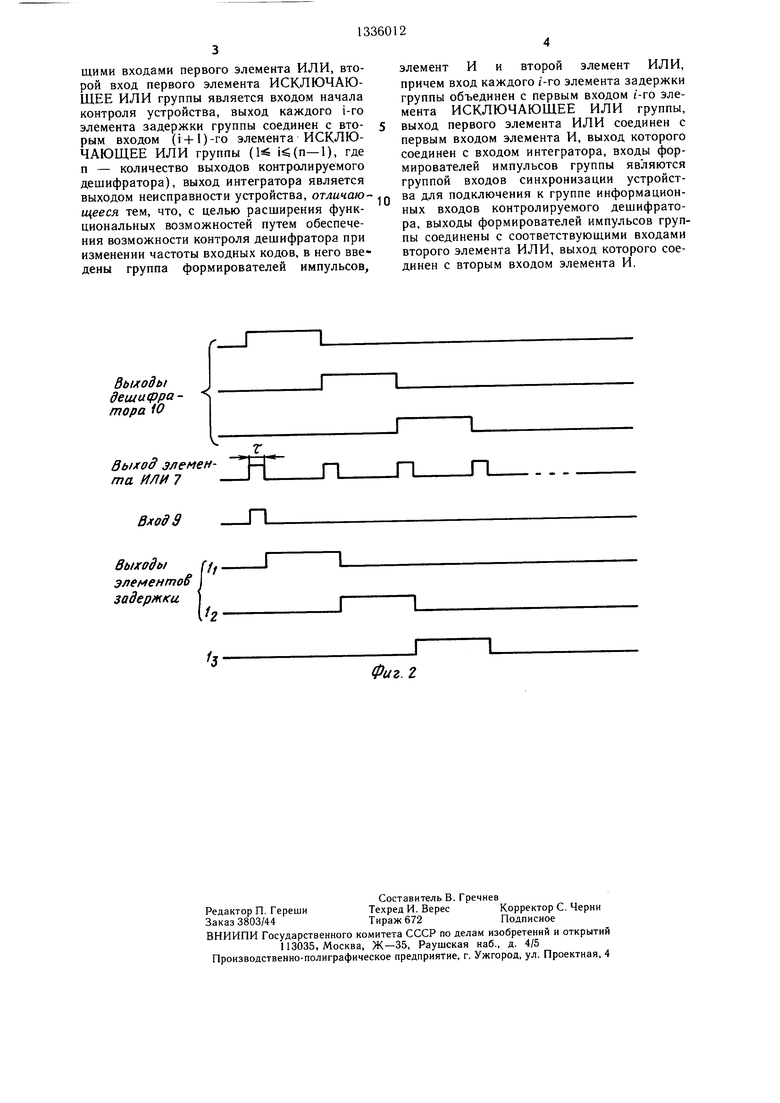

На фиг. 1 приведена функциональная схема устройства для контроля дешифратора; на фиг. 2 - временная диаграмма работы устройства.

Устройство для контроля дешифратора содержит группу 1 элементов задержки, группу 2 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый элемент ИЛИ 3, интегратор 4, выход 5 неисправности устройства, группу 6 формирователей импульсов, второй элемент ИЛИ 7, элемент И 8, вход 9 начала контроля устройства. Кроме того, на фиг. 1 изображен контролируемый дешифратор 10, который не входит в состав устройства.

Формирователи импульсов группы 6 могут быть реализованы, например, в виде дифференцирующих цепочек, предназначенных для формирования импульсов от перепада потенциала на соответствующих входах контролируемого дешифратора 10 при переходе из состояний «1 в «О и из «О в «1.

Устройство работает следующим образом.

Последовательность кодовых комбинаций, поступающих на вход контролируемого дешифратора 10, выбирается так, что на выходах контролируемого дешифратора 10 появляются сигналы в заранее заданной последовательности. При каждом изменении входного кода на соответствующем выходе формирователя импульсов группы 6 появится короткий импульс определенной длительности т. Длительность сигнала на входе 9 устройства должна быть также т. Время задержки каждого элемента группы 1 должна составлять т.

Если одновременно с подачей на входы контролируемого дещифратора 10 первой кодовой комбинации на второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 по входу 9 начала контроля устройства подается импульс, при правильной работе контролируемого дещифратора 10 в течение длительности этого импульса на обоих входах первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 будут присутствовать сигналы логической единицы, а на входах остальных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 будут присутствовать сигналы логического нуля.

На всех выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 будут сигналы логического нуля (во время действия импульса на входе устройства 9), на выходе элемента ИЛИ 3 и элемента И 8 - сигналы логического нуля, а на выходе интегратора 4 - сигнал логической единицы, свидетельствующий об исправности дешифратора на первом шаге проверки. Интегратор 4 обеспечивает фильтрацию кратковременных выбросов на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 и элемента ИЛИ 3 вслед. ствие неидеальности совпадения во времени сигналов на выходах элементов группы 2. Интегратор 4 может быть выполнен в виде инвертора, на входе которого включен шунтирующий конденсатор.

Через время, равное периоду Т смены ко- 0 довых комбинаций, на входы контролируемого дещифратора 10 поступит вторая кодовая комбинация, в результате воздействия которой на втором выходе контролируемого дешифратора 10 появится сигнал и поступит на первый вход второго элемента ИСКЛЮ- ЧАЮЩЕЕ ИЛИ группы 2. В это же время на выходе второго элемента ИЛИ 7 появится следующий импульс длительностью т.

На выходе первого элемента задержки группы 1 логическая единица (сигнал с пер- 0 вого выхода контролируемого дещифратора 10) будет поддерживаться еще время т. При этом во время действия импульсов на выходе элемента ИЛИ 7 на обоих входах второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 присутствуют сигналы логической 5 единицы, а на остальных входах остальных элементов группы 2 - сигналы логического нуля. На выходе 5 неисправности устройства будет сигнал логической единицы.

Если контролируемый дешифратор 10 исправлен, в дальнейшем устройство для контроля дешифратора работает аналогично описанному.

При возникновении различных видов неисправностей в контроируемом дещифраторе 10 импульсы с его выходов и выходов соответствующих элементов задержки группы

1не будут совпадать на соответствующих элементах ИСКЛЮЧАЮЩЕЕ ИЛИ группы

2(во время действия импульса на выходе второго элемента ИЛИ 7). При этом на вы0 ходе интегратора 4 появится сигнал логического нуля, что сигнализирует о сбое в работе дещифратора.

Устройство позволяет правильно контролировать работу дещифратора 10 при периоде Т смены кодовых комбинаций, больщем

5 длительности т импульсов формирователей группы 6.

Формула изобретения

Q Устройство для контроля дещифратора, содержащее группу элементов задержки, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый элемент ИЛИ, интегратор, причем первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы являются группой информа5 ционных входов устройства для подключения к группе выходов контролируемого дещифратора, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с соответствующими входами первого элемента ИЛИ, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы является входом начала контроля устройства, выход каждого i-ro элемента задержки группы соединен с вторым входом (i + l)-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы (1« i(n-1), где п - количество выходов контролируемого дешифратора), выход интегратора является выходом неисправности устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения возможности контроля дешифратора при изменении частоты входных кодов, в него введены группа формирователей импульсов.

Вы/одт дешифра- тора 10

Выход элемен- |-I та ИЛИ 7 1 L

Л

Вход 9

выходы ff.. элементоб задер кки

1/2

0

элемент И и второй элемент ИЛИ, причем вход каждого г -го элемента задержки группы объединен с первым входом j-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выход первого элемента ИЛИ соединен с первым входом элемента И, выход которого соединен с входом интегратора, входы формирователей импульсов группы являются группой входов синхронизации устройства для подключения к группе информационных входов контролируемого дешифратора, выходы формирователей импульсов группы соединены с соответствующими входами второго элемента ИЛИ, выход которого соединен с вторым входом элемента И.

П

Фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дешифратора | 1983 |

|

SU1149267A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1168950A1 |

| Устройство для контроля дешифратора | 1990 |

|

SU1705830A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1141414A1 |

| Устройство для контроля двухступенчатого дешифратора | 1985 |

|

SU1247875A1 |

| Устройство для контроля дешифратора | 1979 |

|

SU811262A1 |

| Устройство для приема и передачи цифровой информации | 1986 |

|

SU1309069A1 |

| Устройство для контроля блоков синхронизации | 1983 |

|

SU1134940A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

| Телеизмерительная система | 1983 |

|

SU1161981A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля различных де1ииф- раторов. Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности контроля дешифратора при изменении частоты входных кодов. Входы формирователей импульсов группы 6 соединены с соответствующими входами контролируемого дешифратора 10. Выходы формирователей импульсов группы 6 объединяются вторым элементом ИЛИ 7, выход которого соединен с .вторым входом элемента И 8. Первый выход контролируемого дешифратора 10 соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 и входом первого элемента задержки группы 1. На второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 поступает сигнал с входа 9 начала контроля устройства. При отсутствии сигнала на первом выходе контролируемого дешифратора 10 сигнал начала контроля проходит через первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 на соответствуюш,ий вход первого элемента ИЛИ 3, на первый вход элемента И 8, сигнал с выхода которого через интегратор 4 поступает на выход 5 неисправности устройства. Коды на вход контролируемого дешифратора 10 подаются в определенной последовательности. Поэтому следуюший единичный сигнал появится на втором выходе дешифратора 10,который соединен с входом второго элемента задержки группы 1 и первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2, на втором входе которого к этому времени присутствует единичный сигнал с выхода первого элемента задержки группы 1. Таким образом, при правильной работе контролируемого дешифратора 10 на выходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 будет нулевой сигнал и на выходе 5 устройства не будет сигнала неисправности. Таким же образом осу- ш.ествляется проверка и остальных выходов контролируемого дешифратора 10. 2 ил. i (Л со со О5

| Устройство для регулирования температуры | 1980 |

|

SU918938A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля дешифратора | 1983 |

|

SU1149267A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-07—Подача