рому входу второго элемента И, а выходы третьего и четвертого элементов И подключены к входам второго элемента ИЛИ, выход которого подключен к R-входу п-разрядного регистра сдвига и R-входу D-триггера, тактовый С-вход которого соединен -с входом Такт устройства , выходом ко прямой выход

торого является D-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи сигналов синхронизации | 1985 |

|

SU1241508A1 |

| Устройство для передачи сигналов начальной синхронизации | 1985 |

|

SU1338100A1 |

| Система передачи и приема информации рекуррентными последовательностями | 1985 |

|

SU1338101A1 |

| Устройство фазового пуска | 1984 |

|

SU1225035A1 |

| Устройство для передачи и приема сигналов начальной синхронизации | 1987 |

|

SU1543559A1 |

| Система передачи дискретной информации | 1985 |

|

SU1325719A1 |

| Устройство для приема сигналов начальной синхронизации | 1986 |

|

SU1427585A1 |

| Система передачи дискретной информации | 1986 |

|

SU1406806A1 |

| Устройство синхронизации с м-последовательностью | 1984 |

|

SU1218484A1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

Игаобретение относится к технике передачи дискретной информации и мож быть использовано в аппаратуре сеансной связи для формирования сигналов Начало сообщения.

Известно устройство для лередачи сигналов начальной синхронизации, содержащее регистр сдвига, выходы которого подключены к входам сумматора по модулю два, выход которого подключен к одному из сигнальных входов выходного переключателя, к другому сигнальному входу которого подключен выход датчикасигналов Точки, а к одному из управляющих входов подключен первый выход датчика меток времени, а также два элемента совпадения, элемент задержки и элемент объединения, при этом второй выход датчика меток времени подключен к одному из входов первого элемента совпадения и к входу элемента задержки, выход которого подключен к одному из входов второго элемента совпадения, выход которого и выход первого элемента совпадения через элемент объединения подключены к другому управляющему входу выходного переключателя, дополнительный выход регистра сдвига подключен к другим входам элемента совпадения, а выход выходного переключателя подключен к входу регистра сдвига Щ.

Однако такое устройство имеет ограниченное применение, так как автокорреляционные функции рекурретных последовательностей не максимальной длины имеют значительные боковые выбросы и по этой причине их применяют в каналах связи с высокими .значениями отношения сигнал/помеха. Кроме того, в таком устройстве невозможно установить точное соот;ношение между интервалами передачи точек и рекуррентной последовательности из-за переключений с передачи точек на передачу рекуррентной последовательности и окончания передачи рекурентной последовательности по сигналам датчика меток времени.

Наиболее близким техническим решением к предлагаемому является устройство для передачи сигналов начальной синхронизации, содержащее п-разрядный регистр сдвига, выходы разрядов которого подключены к входам сумматора по модулю два и дешифратора сигнала окончания рекуррентного цикла, выход которого подключен к R-входу RS-триггера управления передачей, S-вход которого соединен с входом Пуск устройства, при этом выход сумматора по модулю два подключен к D-входу первого разряда п-разрядного регистра сдвига, С-вход которого соединен с входом Такт устройства 2.

Недостатком известного устройства .являются ограниченные функциональные возможности из-за невозможности передачи рекуррентных последовательностей с различными начальными условиями, что не позволяет применить устройство для осуществления адресной начальной синхронизации. Кроме того, в известном устройстве отсутствует возможность передачи сигнала установления пoбиtoвoй синхронизации.

Цель изобретения - расширение функциональных возможностей путем обеспечения передачи сигналов адресной начальной синхронизации.

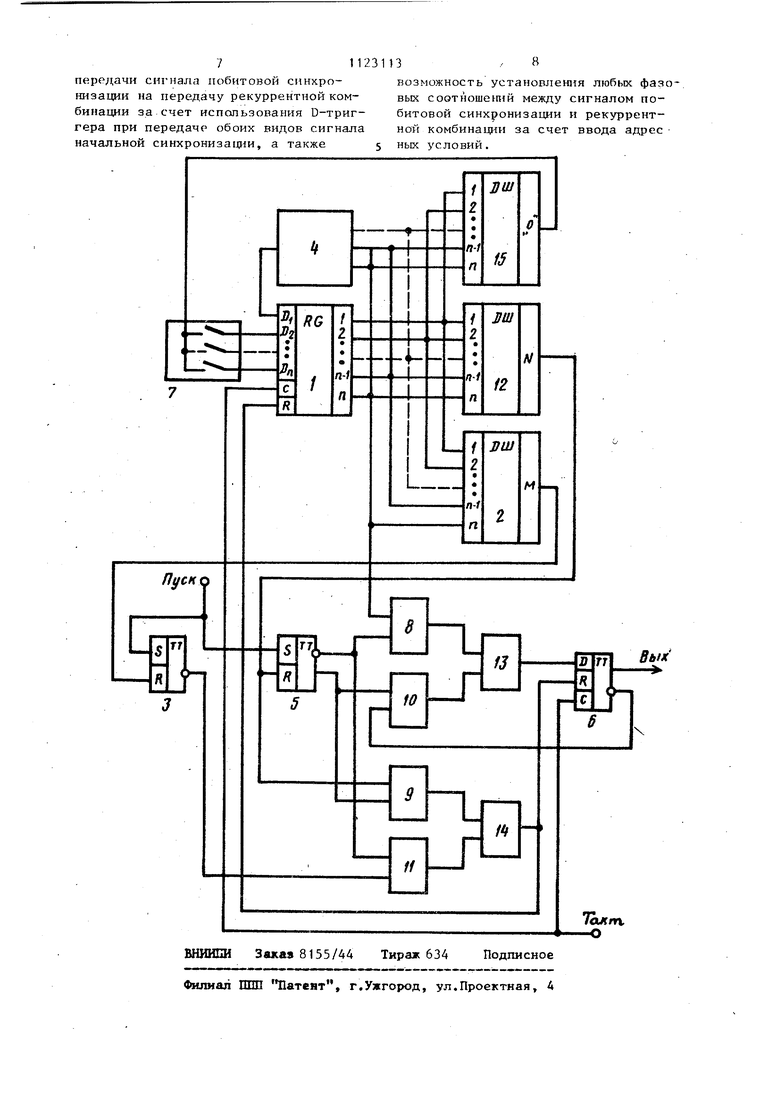

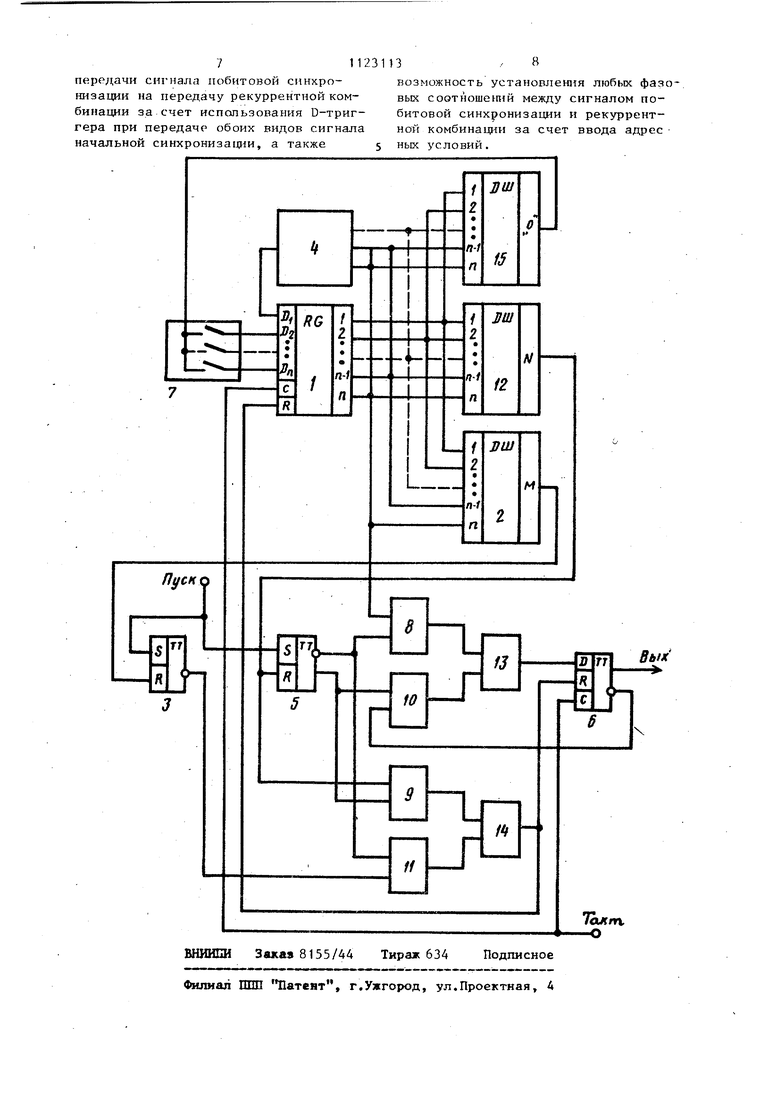

Для достижения поставленной цели в устройство для передачи сигналов начальной синхронизации, содержащее п-разрядный регистр сдвига, выходы разрядов которого подключены к входам сумматора по модулю два и дешифратора сигнала окончания рекуррентного цикла, выход которого подключен к R-входу RS-триггера управления пере-; 31 дачей, S-вход которого соединен с входом Пуск устройства, при этом выход сумматора по модулю два подключен к D-входу первого разряда ,п-разрядного регистра сдвига, С-вход которого соединен с входом Такт устройства, введены RS-триггер переключения сигналов начальной синхрони зации, блок установки адресных условий, четыре элемента И, два элемента ИЛИ, D-триггер, дешифратор сигнала окончания передачи сигнала побитовой синхронизации и дешифратор 1гул вого состояния п-разрядного регистра сдвига, выход которого через блок установки адресных условий подключен к D-входам всех разрядов, кроме первого п-разрядного регистра сдвига, выходы разрядов которого под ключены к входам дешифратора нулевого состояния п-разрядного регистра сдвига и дешифратора сигнала окончания передачи сигнала побитовой синхронизации, при этом выход последнег разряда п-разрядного регистра сдвига подключен к первому входу первого элемента И, к второму входу которого подключен инверсный выход RSтриггера переключения сигналов начальной синхронизации, S-вход которого соединен с входом Пуск устройства, а прямой выход RS-триггера переключения сигналов начальной синхронизации подключен к первым входам второго и третьего элементов И, причем выход дешифратора сигнала окончаНИН передачи сигнала побитовой синхронизации подключен к второму входу третьего элемента И и RS-триггера переключения сигналов начальной синхронизации, инверсный выход которого подключен к первому входу четвертого элемента И, к второ му входу которого подключен инверсный выход RS-триггера управления передачей, при этом выходы первого и второго элементов И подключены к вхо дам первого элемента ИЛИ, выход которого подключен к D-входу D-триггера, инверсньй выход которого подключен к первому входу четвертого элемента И, к второму входу которого подключен инверсный выход RS-триггера управления передачей, при этом выходы первого и второго элементов И подключены к входам первого элемен та ИЛИ, выход которого подключен к D-входу D-триггера, инверсный выход которого подключен к второму входу 134 второго элемента И, авыходы третьего и четвертого элементов И .подключены .к входам второго элемента ИЛИ, выход которого подключен к R-входу п-разрядного регистра сдвига и R-входу D-триггера, тактовый G-вход которого соединен с входом Такт устройства, выходом которого является пря прямой выход D-триггера. На чертеже представлена структур,нал электрическая схема устройства для передачи сигналов начальной синхронизации. Устройство для передачи сигналов начальной синхронизации содержит п-разрядный регистр 1 сдвига, дешифратор 2 сигнала окончания рекуррент ного цикла, RS-триггер 3 управления передачей, сумматор 4 по модулю два, RS-триггер 5 переключения сигналов начальной синхронизации, D-триггер 6, блок 7 установки адресных условий, первый 8, второй 9, третий 10 и четвертый 11 элементы И, дешифратор 12 сигнала окончания передачи сигнала побитовой синхронизации, первый 13 и второй 14 элементы ИЛН. Устройство для передачи сигналов начальной синхронизации работает следующим образом. В исходном состоянии RS-триггер 3 управления передачей и RS-триггер 5переключения сигналов начальной син хронизации находятся в нулевом состоянии, что обеспечивает наличие сигнала на выходе четвертого элемента И 11, который через второй эле- мент ИЛИ 14 удерживает в исходном состоянии п-разрядный регистр 1 сдвига и D-триггер 6 по R-входам. При поступлении сигнала на вход Пуск устройства RS-триггер 3 управ ления передачей и RS-триггер 5 переключения сигналов начальной синхронизации устанавливаются по S-входам в единичное состояние, тем самым разрешая работу п-разрядного регистра 1 сдвига и D-триггера 6, при этом за счет подачи сигнала с прямого выхода RS-триггера 5 переключения сигналов начальной синхронизации на первый вход третьего элемента И 10 обеспечивается связь D-входа D-триггера 6 по своим инверсным выходам через первьй элемент ИЛИ 13, D-триггер 6начинает работать в режиме деления частоты тактовых импульсов на два, тем самым обеспечивая формирова$1ние на выходе устройства сигнала начальной синхронизации в виде точек. По первому тактовому импульсу пос ле сигнала Пуск, в п-разрядный регистр 1 сдвига осуществляется запись адресных условий путем подачи сигнала с выхода дешифратора 15 нулевого состояния п-разрядного регистра 1 сдвига через блок 7 установки адресных условий на соответствукмцие D-BXO ды регистра 1 сдвига и тактового импульса на С-вход.п-разрядного регист ра 1 сдвига. По остальным тактовым импульсам осуществляется формирование рекуррентной комбинации в соответствии с установленными через сумматор 4 по модулю два обратными свя зями выходов разрядов п-разрядного регистра 1 сдвига с D-входом первого разряда п-разрядного регистра 1 сдвига. Дешифратор 12 сигнала окончания передачи сигнала побитовой синхро- низации формирует сигнал при образо вании на выходах разрядов п-разрядкого регистра 1 сдвига рекуррентной комбинации, соответствующей окончанию времени передачи сигнала побитовой синхронизя11 1и в виде вырабатываемых D-триггером 6 точек. Техническая реализация дешифратора 12 сигнала окончания передачи побит вой синхронизаьщи сводится к постро нию логической схемы, формирующей выходной сигнал только при единственном сочетании выходных сигналов Сигнал с выхода дешифратора 12 сигнал окончания передачи сигнала побитово синхронизации (точек) поступает на R-вход RS-триггера 5 переключения сигнала начальной синхронизации и вход второго элемента И 9, при этом происходит установка в исходное сос тояние RS-триггера 5 переключения сигнала начальной синхронизации, п-ра рядного регистра 1 сдвига и D-триг гера 6 за счет образования сигнала на выходе второго элемента И 9 и второго элемента ИЛИ 14. Установка RS-триггера 5 переключения сигнала начальной синхронизации вызывает отключение D-входа D-триггера 6 от собственного инверсного входа за сч снятия сигнала с первого входа третьего элемента И 10, соединенного с прямым выходом RS-триггера 5 переключения сигнала начальной синхро низации, и подключение его к выходу п-го разряда п-разрядного регистра 36 сдвига за счет подачи сигнала с инверсного выхода RS-триггера 5 переключения сигнала начальной синхронизации на второй вход первого эле- , мента И 8. С поступлением очередного тактового импульйа начинается процесс формирования рекуррентной комбинации с начальных условий, которые вводятся описанным способом с блока 7 адресных условий. Сигналы разрядов рекуррентной комбинации поступают на D-вход D-триггера 6 и далее под действием тактовых импульсов, поступаю1цих на С-вход Dтриггера 6,-на выход устройства. Процесс формирования рекуррентной комбинации длится до появления на выходах п-разрядного регистра 1 сдвига конечной комбинации, при которой дешифратор 2 сигнала окончания рекуррентного цикла формирует сигнал, который поступает на R-вход RS-триг-гера 3 управления передачей. Установка RS-триггера 3 управления передачей по К-6ходу приводит к окончанию передачи сигнала начальной синхронизации и установке устройства в исходное состояние. Техническая реализация деишфратора 2 сигнала окончания рекуррентного цикла отличается от описанной реализации дешифратора 12 сигнала окончания передачи сигнала побитовой синхронизации только задаваемой комбинацией на выходах разрядов п-разрядного регистра 1 сдвига. Изменение адресных УСЛОВИЙ производится соответствующими переключателями в блоке 7 адресных условий и изменением конечной комбинации рекуррентного цикла путем перестройки дешифратора 2 сигкала окончания рекуррентного цикла. Таким образом, предлагаемое устройство для передачи сигналов начальной синхронизации обеспечивает более широкие функциональные возможности, так как в нем могут передаваться рекуррентные М-последовательности с адресными условиями и сигналы побитовой синхронизации в виде точек, высокую точность поддержания постоянства отношения времени передачи сигнала Точки к времени передачи рекуррентной комбинации за счет использования регистра сдвига как для генерирования рекуррентной комбинации, так и для отсчета времени передачи сигнала Точки, отсутствие временных искажений при переключениях с

71123113/ В

передачи сигнала побитовой синхро- возможность установления любых фазонизации на передачу рекуррентной комбинации за счет использования D-триггера при передаче обоих видов сигнала начальной синхронизаф1и, а также 5

вых соотношеьшй между сигналом побитовой синхронизации и рекуррентной комбинации за счет ввода адрес ных условий.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для передачи сигналов начальной синхронизации | 1980 |

|

SU896783A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Мартынов Е.М | |||

| Синхронизация в системах передачи дисдсретных сообщений | |||

| М., Связь, 1972, с | |||

| ПЕЧНОЙ ЖЕЛЕЗНЫЙ РУКАВ (ТРУБА) | 1920 |

|

SU199A1 |

Авторы

Даты

1984-11-07—Публикация

1983-07-07—Подача