Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях с высоким быстродействием.

Цель изобретения - повышение точности вычисления при минимальных дополнительных аппаратурных затратах.

Первый и второй регистры обеспечивают хранение кодов старшей и младющее устройство обеспечивает хранение значений oii-координаты на оси абсцисс точки пересечения производных для двух соседних фиксированных

значений sin - X

Схема сравнения обеспечивает сравнение сь с X

и в зависимости от результатов сравнения управляет работой схемы прибавления шей части аргумента (X и Х). Первое fO единицы и через элемент ИС- запоминающее устройство обеспечивает КЛЮЧАЮЩЕЕ ИЛИ работой второ- хранение фиксированных значений го регистра . При этом , вычисsin - Х

и COS - Х

sinx

ление функции произво одной из формул

Второе запоминаsin |(Хс) при ., (1)

sin |(Х,+2 )-1 со8(Х - -2 ).Х„,при Х ei (2)

В результате с выходов второго регистра на второй вход умножителя поступает неинвертированное или инвертированное (отрицательное) значение X . Сумматор единицы за счет связи с адресным входом первого запоминающего устройства обеспечивает выборку из него требуемых значений синуса и косинуса, которые поступают на входы умножителя. Умножитель обеспечивает выдачу результата вычислений JQ схему 4 сравнения, второй регистр 5, по одной из формул.сумматор 6 единицы, умножитель-сумматор 7 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8.

Вычисление cosx производится в соответствии с выражением , для чего на управляющий вход устройства подается сигнал, по которому в буферных регистрах происходит инвертирование аргумента.

Благодаря тому, что устройство реализует вычисление функций sinx, cosx

sin - - cosX

при

-П

(I)

sin 1(X +2 )-1 cos() .X при (2)

X . ed где X - старшая часть разрядов кода аргумента;

младшая часть разрядов кода аргумента;

координата на оси абсцисс точки пересечения производных двух соседних фиксированных значений, хранящихся в первом запоминающем устростве 2.

Устройство работает следующим образом.

Со входа кода аргумента устройства на информа1у онные входы первого 1 и второго 5 регистров поступает ко

о13222722

ющее устройство обеспечивает хранение значений oii-координаты на оси абсцисс точки пересечения производных для двух соседних фиксированных

значений sin - X

Схема сравнения обеспечивает сравнение сь с X

и в висимости от результатов сравнения управляет работой схемы прибавлени единицы и через элемент ИС КЛЮЧАЮЩЕЕ ИЛИ работой второ го регистра . При этом , выч

ление функции производится по одной из формул

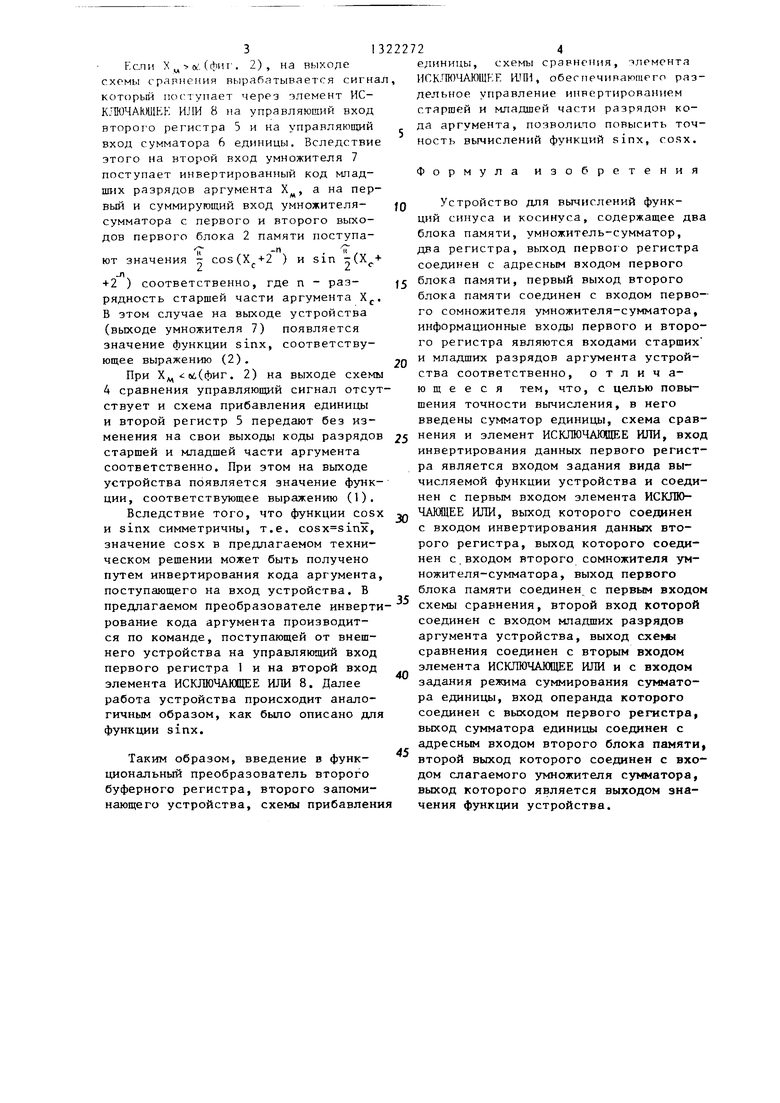

по формулам (1) и (2) (фиг. 2) повышается точность результатов.

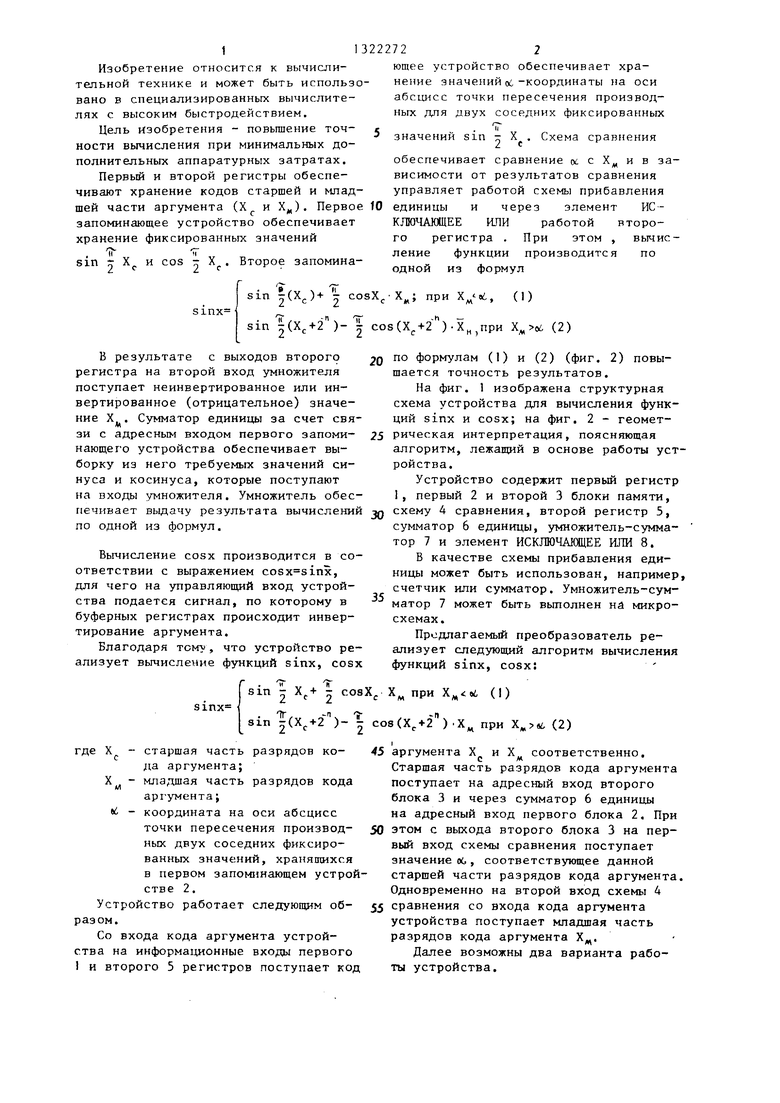

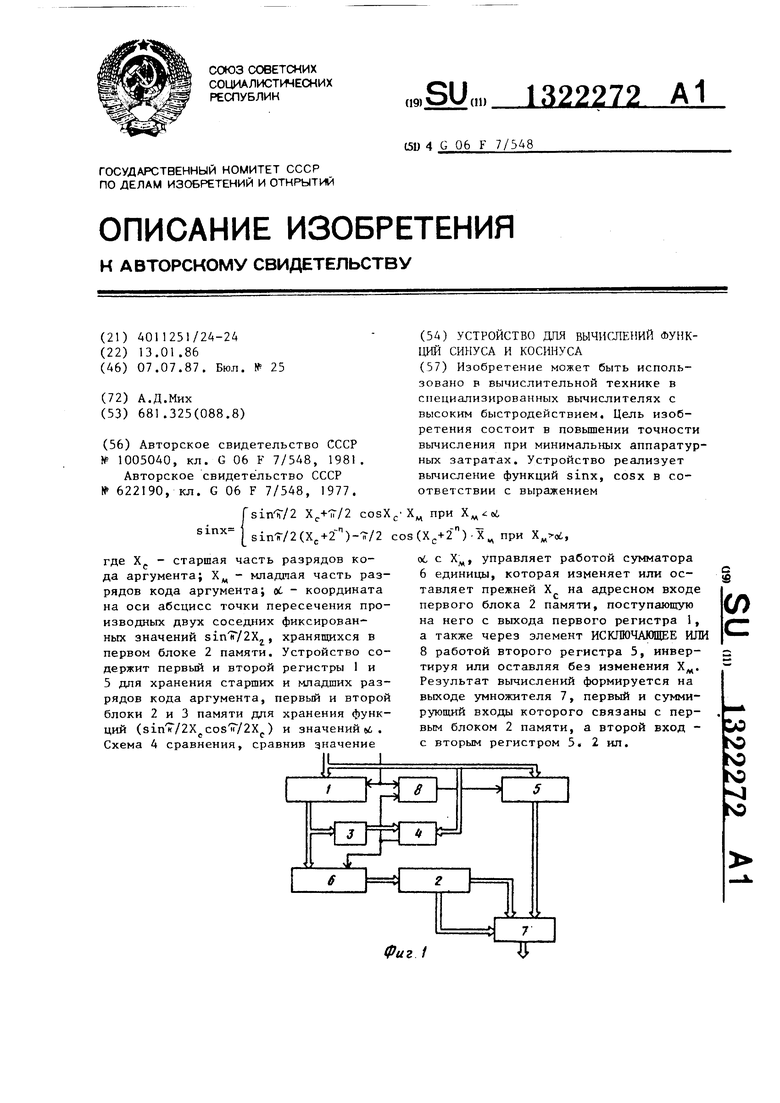

На фиг. 1 изображена структурная схема устройства для вычисления функций sinx и cosx; на фиг, 2 - геомет- рическая интерпретация, поясняющая

алгоритм, лежащий в основе работы устройства.

Устройство содержит первый регистр первый 2 и второй 3 блоки памяти.

35

В качестве схемы прибавления единицы может быть использован, например, счетчик или сумматор. Умножитель-сумматор 7 может быть вьшолнен на микросхемах.

Предлагаемый преобразователь реализует следующий алгоритм вычисления функций sinx, cosx:

при

-П

(I)

+2) .X при Х

45 аргумента X и Х соответственно.

Старшая часть разрядов кода аргумента поступает на адресный вход второго блока 3 и через сумматор 6 единицы на адресный вход первого блока 2. При

50 этом с выхода второго блока 3 на первый вход схемы сравнения поступает значение о(,, соответствующее данной старшей части разрядов кода аргумента Одновременно на второй вход схемы 4

55 сравнения со входа кода аргумента устройства поступает младшая часть разрядов кода аргумента Х.

Далее возможны два варианта работы устройства.

, (фиг . 2), на выходе схемы срариения вырабатывается сигнал который поспупает через элемент ИС- КЛЮЧАЩЕК ИЛИ 8 на управляющий вход второг о регистра 5 и на управляющий вход сумматора 6 единицы. Вследствие этого на второй вход умножителя 7 поступает инвертированный код нпад- Ш1Х разрядов аргумента Х, а на первый и суммирующий вход умножителя- сумматора с первого и второго выходов первого блока 2 памяти поступают значения cos( ) и sin п(+2 ) соответственно, где п - раз-

рядность старшей части аргумента Х. В этом случае на выходе устройства (выходе умножителя 7) появляется значение функции sinx, соответствующее выражению (2).

При Х;.свй(фиг. 2) на выходе схемы 4 сравнения управляющий сигнал отсутствует и схема прибавления едини1да и второй регистр 5 передают без изменения на свои выходы коды разрядов старшей и младшей части аргумента соответственно. При этом на выходе устройства появляется значение функции, соответствующее выражению (1).

Вследствие того, что функции cosx и sinx симметричны, т.е. , значение cosx в предлагаемом техническом решении может быть получено путем инвертирования кода аргумента, поступающего на вход устройства. В предлагаемом преобразователе инверти рование кода аргумента производится по команде, поступающей от внешнего устройства на управляющий вход первого регистра 1 и на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8. Далее работа устройства происходит аналогичным образом, как было описано для функции sinx.

Таким образом, введение в функциональный преобразователь второго буферного регистра, второго запоминающего устройства, схемы прибавления

g

5

о

5

Q

0

5

единицы, схемы срзрнсния, тлемснта ИСК.ПЮЧАЮЩЕЕ Ш1И, обеспечивающего раздельное управление иирертированием старшей и младшей части разрядов кода аргумента, позволнпо повысить точность вычислений функций sinx, cosx.

Формула изобретения

Устройство для вычислений функций синуса и косинуса, содержащее два блока памяти, умножитель-сумматор, два регистра, выход первог о регистра соединен с адресным входом первого блока памяти, первый выход второго блока памяти соединен с входом первого сомножителя умножителя-сумматора, информационные входы первого и второго регистра являются входами старших и младших разрядов аргумента устройства соответственно, отличающееся тем, что, с целью повышения точности вычисления, в него введены сумматор единицы, схема сравнения и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, вход инвертирования данных первого регистра является входом задания вида вычисляемой функции устройства и соединен с первым входом элемента ИСКЛЮ- ЧАЩЕЕ ИЛИ, выход которого соединен с входом инвертирования данных второго регистра, выход которого соединен с,входом второго сомножителя умножителя-сумматора, выход первого блока памяти соединен с первым входом схемы сравнения, второй вход которой соединен с входом младших разрядов аргумента устройства, выход схакси сравнения соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с входом задания режима суммирования сумматора единицы, вход операнда которого соединен с выходом первого регистра, выход сумматора единицы соединен с адресным входом второго блока памяти, второй выход которого соединен с входом слагаемого умножителя сумматора, выход которого является выходом значения функции устройства.

Sin()

Фиг 2

Редактор П.Гереши

Составитель З.Шершнева Техред Л.Олийнык

Заказ 2865/45 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Л.Пилипенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций синуса и косинуса | 1980 |

|

SU907546A1 |

| Устройство для вычисления тригонометрических функций | 1985 |

|

SU1257639A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1388855A1 |

| Устройство для вычисления функций синуса и косинуса | 1986 |

|

SU1478213A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1262486A1 |

| Устройство для вычисления тригонометрических функций | 1987 |

|

SU1427362A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1339555A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1236465A1 |

| Устройство для вычисления функций @ и @ | 1980 |

|

SU978146A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

Изобретение может быть использовано в вычислительной технике в специализированных вычислителях с высоким быстродействием. Цель изобретения состоит в повышении точности вычисления при минимальных аппаратурных затратах. Устройство реализует вычисление функций sinx, cosx в соответствии с выражением при X, ,oi Xg-b2 ) X при , где Xp - старшая часть разрядов кода аргумента; Х, - младиая часть разрядов кода аргумента; oL - координата на оси абсцисс точки пересечения производных двух соседних фиксированных значений sinlT/ZX, хранящихся в первом блоке 2 памяти. Устройство содержит первый и второй регистры 1 и 5 для хранения старших и младших разрядов кода аргумента, первый и второй блоки 2 и 3 памяти для хранения функций () и значений б . Схема 4 сравнения, сравнив значение III об с Х, управляет работой сумматора 6 единицы, которая изменяет или оставляет прежней X на адресном входе первого блока 2 памяти, поступающую на него с выхода первого регистра 1, а также через элемент ИСКЛЮЧАКЛЦЕЕ ИЛИ 8 работой второго регистра 5, инвертируя или оставляя без изменения Х. Результат вычислений формируется на выходе умножителя 7, первый и суммирующий входы которого связаны с первым блоком 2 памяти, а второй вход - с вторым регистром 5. 2 ил. i (Л :) N3 N0 SD SD «г /

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ЗЛОУМЫШЛЕННОЙ РАЗБОРКИ ЖЕЛЕЗНОДОРОЖНОГО ПУТИ | 1927 |

|

SU10050A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| при X, ,oi sinx rsin h-/2 Х +1Г/2 sinir/2(Xj.+2 )-7/2 cos (Xg-b2 ) X при , | |||

Авторы

Даты

1987-07-07—Публикация

1986-01-13—Подача