сигналу устанапливается в О счетчик 7, сумматор и триггер 10, а G 1 -триггер 12. Этот же сигнал, пройдя через элемх нт ИЛИ 18. устанавливает р О триггер 11. Положительный потенциал с единичного выхода триггера 12 разрешает работу элемента И 8 и 9 14 переключает информационный оыхо;;; счетчика 7 ii3 выход коммутатора б. Первы71 тзктойый импульс, пройдя через элемент И G и элемент ИЛИ 17, поступает на вход обра-цен я блока 2 .-.амяти, на адресный вход которого через коммутатор 6 поступает нулесоо значение счетчмка 7, Выход элемзнта И 9, пройдя через элемент 21 задержки и элемент ИЛИ 19, поступает на вход записи блока 2 памяти, На информацио1и ый сход блока 2 памяти поступает нулевой потенциал с единичного пыхода триггера 10. Таким образом, первым тактовым импульсом по нулевому адресу записывается О. Первый тактовь й импульс, пройдя через элемент 22 задержкии элемент И О, прибевляет к значению счетчика 7 единицу. Описанный цикл работы устройства повторяется до переполнения счетчика 7, Импульс переполнения счетчика 7 устанавливает з О триггер 12, нулепэй поте.чциал на единичном выходе которого переключает коммутатор 6 и указывает на окончание режима начальной установки устройства и готовнбсть устройстоа для роботы D режиме контроля. Сигнал переполнения счетчика 7, пройдя через элемент (/ТЛИ 20, переводит триггер 10 в единичное состоян:/;е и обнуляет сумматор 4, В режиме контроля на вход 23 устройстоо подается йдиничный потенциал, на вход 24 подлггср здрес. а из вход 25 - Г1ризна1с обращения. При гюступлеигли сигнала на зходь 24 и 25 устрсйст1ча на выходе 1 поясляетсй значение кода, зап-лсаткого по соотсетствующему адресу, а на выходе блока: 2 памяти появляется нулевой сигнал. Так как триггер 10 находится в единичном состоянии, то на аыходе сумматора 15 по модулю два присутствует единичный потенциал, который разрешает гфохождение через группу элементов И 3 кода с гзыхода блока i памяти. На сумм.аторе 4 происходит содержиг-юго считанной ячейки памяти с предыдущим содержание. сумматора. При этом выход сумматора 15 sio модулю два поступает на тактовый вход . :риггера 11, который устанавливается в 1. По переходу из О в 1 триггера 11 одноf з vopaтop 14 формирует положительный и.мпульс, который прибавляет +1 к счетчику 16 и через элемент 11ЛИ 19 поступает на вход записи блока 2 памяти. В блоке 2 памяти по адресу считывания записывается

единичное значение с триггера 10. Если происходит обращение к ячейке памяти, к которой уже обращались, то содержимое соответствующего адреса блока 2 памяти равно единица. Следовательно, на выходе сумматора 15 присутствует нулевой потенциал и содержимое данного адреса повторно не накапливается в сумматоре А, Кроме того, в счетчике 16 не уч5 тываются многократные обращения к одним и тем ;(е адресам, счетчик 16 считает только первое обращение по каждому из адресов. После того, как было обращение по всем контролируемым адресам, счетчик 16 перег1олняется,

разрешает сравнение накопленной суммы в сумматоре I с эталонной суммой с входа 29, устройства и устанавливает триггер 10 и сумматор в нулевое состояние.

Если содержимое сумматора совпало с

кодом на входе 29, то на выходе 30 имеется нулевой потенциал; если содержимое сумматора не совпало со значением кода на входе 29, то на выходе 30 устройства появляется сигнал, указывающий на неверную

работу блока памяти.

После переключения триггера 10 в нулевое состояние работа устройства происходит точно так . же, как описано, с той разницей, что все ячейки блока 2 памяти

установлены в единицу. По каждому (первому) обращению из блока 2 памяти считывается единичный сигнал, который, складываясь со значением триггера 10, дает на выходе единичный потенциал, который

осуществляет те же действия, которые описаны, с той разницей, что в блок 2 записываатся ноль. Если к ячейке блока 2 памяти производится повторное обращение, то на выходе сумматора 15 имеется нул.евой потенциал, который запрещает суммирование на сумматоре 4, В дальнейшем работа устройства повторяется.

Таким образом, значительно повышается быстродействие устройства, поскольку

нет необходимости в многократной перезаписи блока 2 памяти после каждого цикла контроля.

Формула изобретения Устройство для обнаружения ошибок в блоках памяти программ, содержащее первый .длемемт ИЛИ, первый и второй элементы ys, коммутатор, информационные входы первой группы которого являются информационными входами устройства, выходы коммутатора подключены к адресным входам блока памяти обращений, а информационные аходы второй группы коммутатора соединены с выходами группы счетчика адреса, группу элементов И, первые входы которых являются информационными входами устройства, а выходы подключены к информационным входам накапливающего сумматора, выходы которого подключены к информационным входам первой группы блока сравнения, информационные входы второй группы и выход которого являются соответственно входами значения контрольной суммы и выходом ошибки устройства, первый триггер, информационный вход которого является входом режима контроля устройства, а выход соединен с входом первого одиоЕибратора, выход которого подключен к счетному входу счетчика количества обращений, второй одновибратор, отличающееся тем, что, с целью повышения быстродействия, в него введены второй, третий и четвертый элементы ИЛИ,первый и второй элементы задержки, второй и третий триггеры, сумматор по модулю два, примеру первый вход первого .элемента ИЛИ является входом обращения устройства, выход первого злементй ИЛИ соединен с входом выборки блока памяти обращений, выход которого подключен к первому входу сумматора по модулю два, второй вход которого соединен с информационным входом блока памяти обращений и с выходом второго триггера, R-вход которого подключен к S-входу третьего триггера, входам начальной установки счетчика адреса, сметчика количества обращений и накапливающего сумматора, первому аходу второго элемента ИЛИ и является входом начальной установки устройства, выход

сумматора по модулю два соединен с вторым входом элемента ИЛИ, вторыми входами элементов И группы, синхровходом первого триггера и входом второго одновибратора, выход которого подключен к второму входу второго элемента ИЛИ, выход которого соединен с входом сброса первого триггера, информационные входы счетчика количества обращений являются входами количества обращений устройства, а выход переполнения счетчика количества обращений подключен к управляющему входу блока сравнения и первому входу четвертого элемента ИЛИ, выход которого соединен со счетным входом первого триггера и входом обнуления накапливающего сумматора, вход записи блока памяти обращений подключен к выходу третьего элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого одновибратора и первого элемента задержки, вход которого подключен к третьему входу первого элемента ИЛИ и выходу второго элемента И, первый вход которого является тактовым входом устройства и соединен с входом второго элемента задержки, выход которого подключен к первому входу первого элемента И, второй вход которого соединен с вторым входом второго элемента И, управляющим входом коммутатора и выходом третьего триггера, R-вход которого подключен к второму входу четвертого элемента ИЛИ и выходу счетчика адреса, счетный вход которого соединен с выходом первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1003150A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Логическое устройство для обработки информации | 1984 |

|

SU1339578A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1013955A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2017 |

|

RU2727555C2 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

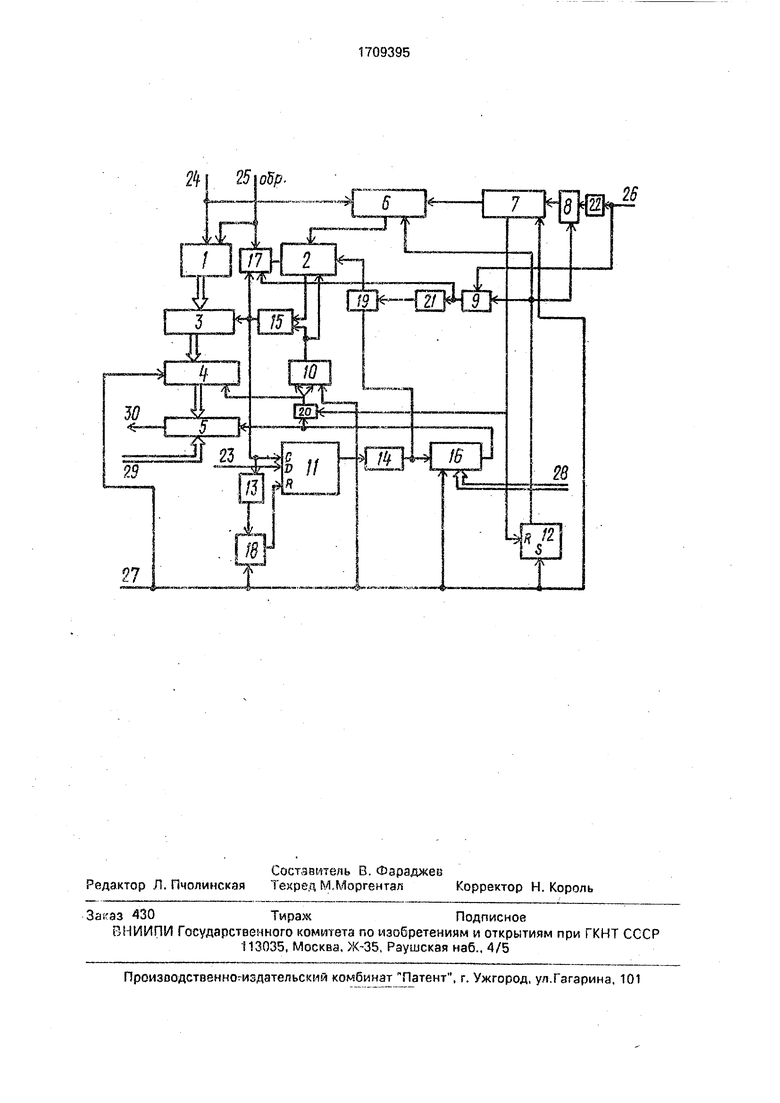

Изобретение относится к вычислительной технике и может быть использовано для контроля достоверности хранения информации в постоянных запоминающих устройствах в процессе их работы. Цельюизобретения является повь?шение быстродействия устройства. Устройство содержит блок памяти обращений, группу элементов И, накапливающий сумматор, блок сравнения, коммутатор, счетчик адреса, первый и второй элементы И, элементы ИЛИ с первого по четвертый, первый и второй элементы задержки, первый и второй одновибраторы, сумматор по модулю два, счетчик количества обращений. Цель изобретения достигается тем, что после каждого цикла подсчета контрольной суммы в устройстве осуществляется инверсия признака фиксации обращений в блоке памяти обращений. В результате исключаются непроизводительные циклы перезаписи блока памяти обращений для его начальной установки. 1 ил.ЁИзобретение относится к вычислительной технике, а именно к устройствам контроля постоянной памяти, и может быть использовано для контроля достоверности хранения информации а запоминающих устройствах в процессе работы.Цель изобретения - повышение быстродействия устройства.На чертеже представлена схема устройства для обнаружения ошибок блока памяти программ.Блок 1 памяти программ, изображенный на чертеже, в состав устройства не входит..'Устройство содержит блок 2 памяти обращений, группу элемантов И 3, накапливающий сумматор 4, блок 5 сравнения контрольной суммы, коммутатор 6. счетчик 1 адреса, элементы И 8 и 9, триггер 10 коли-чества обращений, триггер 11 признака первого обращения. Триггер 12 начальной установки, одновибраторы 13-14, сумматор 15 по модулю два, счетчик 16 количества обращений, элементы ИЛИ 17-20, элементы 21- 22 задержки, вход 23 режима контроля устройства, вход 24 адреса устройства, вход 25 признака обращения устройства, тактовый вход 26, вход 27 начальной установки устройства, вход 28 количества контролируемых адресов устройства, вход 29 значения контрольной суммы устройства и выход 30 ошибки устройства.Устройство работает в двух режимах: в режиме начальной установки и режиме контроля.Режим начальной установки устанавливается при появлении положительного потенциала на входе 27 устройства. По этому•Чо ю00ю ел

| Устройство для контроля долго-ВРЕМЕННОй пАМяТи | 1979 |

|

SU813508A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-01-30—Публикация

1988-07-21—Подача