Изобретение относится к вычисли- тельной технике и может быть использовано для формирования сигнала прерывания при отладке программ.

Цель изобретения - сокращение времени отладки программ.

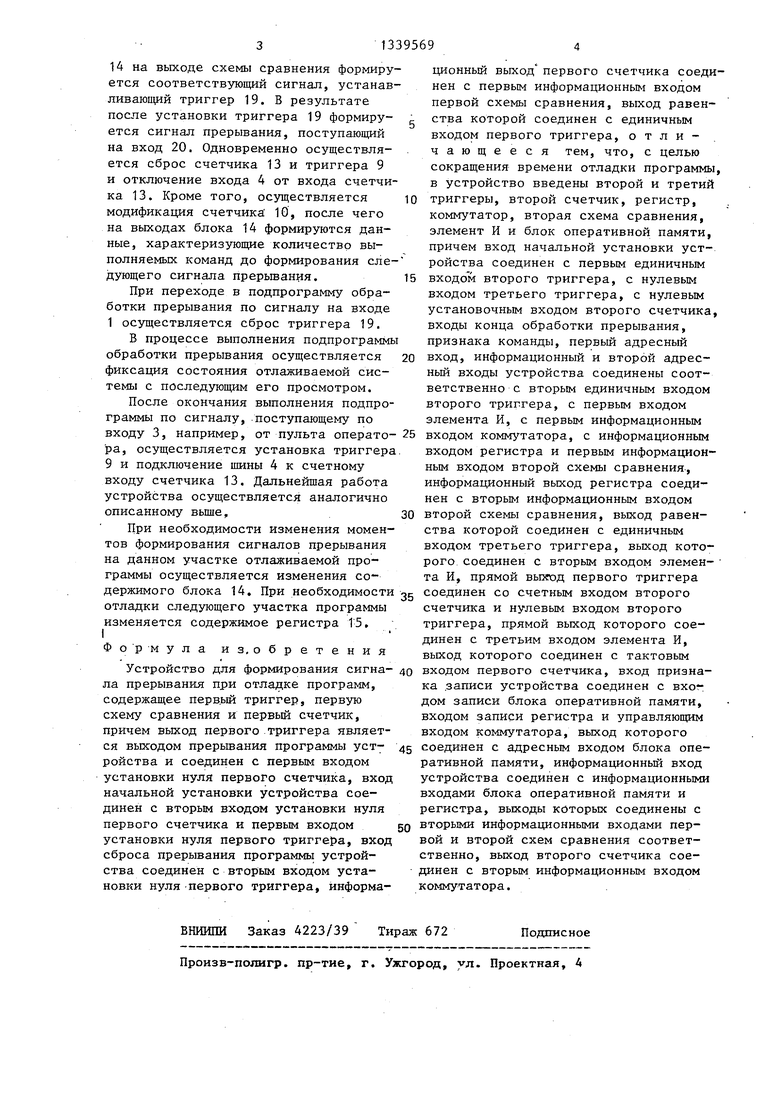

На чертеже представлена структурная схема устройства.

Устройство содержит вход 1 сброса прерывания устройства, вход 2 начальной установки устройства, вход 3 конца обработки прерывания устройства, вход 4 признака команды устройства, первый адресный вход 5 устройства, вход 6 записи устройства, информационный вход 7, второй адресный вход 8 устройства, триггер 9, второй счетчик 10, элемент И 11, коммутатор 12, первый счетчик 13, блок .14 оперативной памяти, регистр 15, схемы 16 и 17 сравнения, триггеры 18 и 19, выход 20 прерывания.

Входы 1-4 служат для передачи сигналов сброса прерывания, начальной установки устройства, сигналов об окончании обработки прерывания и о начале выполнения команды соответственно. Вход 5 служит,.для передачи адресной информации на вход блока 14 при записи .в него данных. При помощи сигналов, поступающих по входу 6, определяются режимы работы блока 14 и регистра 15, а также источник адресов блока 14. По входу 7 поступают данные на входы блока 14 и регистра 15 при записи в них информации. К входу В подключается адресная шина отлаживаемой системы. Триггер 9 фиксирует интервал между окончанием обработки предыдущего и формированием последующего прерываний. Счетчик 10 служит для формирования адресов блока 14 в процессе отладки программ. Коммутатор 12 транслирует на адресные входы бло- ка 14 сигналы с выходов счетчика 10 или входа 5 в зависимости от сигналов на вход 6. При помощи счетч1;(ка 13 фиксируется количество вьшолненных команд с момента окончания обработки последнего прерывания. В блоке 14 хранятся данные, характеризующие количество команд, вьшолняемых в промежутке между формированием двух соседних сигналов прерывания. Регистр 15 служит для хранения начального адреса отлаживаемого участка программы. Схема 16 предназначена для определения момента формирования сигнала прерьшания. При помощи схемы 17 в процессе отладки определяется начало отлаживаемого участка программы с последующей фиксацией его при помощи триггера 18 Триггер 19 предназначен для формирования сигнала прерьшания, поступающего на шину 20.

Устройство работает следующим образом.

П о сигналу, поступающему по входу 6, блок 14 оперативной памяти переводится в режим записи. Одновременно вход 5 подключается к адресным входам блока 14. Данные, поступающие с входа 7 и характеризующие количество команд, выполняемых между двумя соседними прерываниями, записываются в блока 14 по адресам, поступающим с входа 5. Кроме того, осуществляется запись в регистр 15 начального адреса отлаживаемого участка программы. После окончания загрузки сигналом., поступающим с входа 6, блок 14 и регистр 15 переводятся в режим считывания информации. Одновременно счетчик 10 через коммутатор 12 подключается к адресным входам блока 14.

По сигналу, поступающему по входу 2, осуществляется установка триггера 9 в единичное состояние и сброс триггеров 18 и 19 и счетчиков 10 и 13. Устройство приведено в исходное состояние. На выходах блока 14 присутствуют данные, считанные из нулевой ячейки i

В процессе отладки адреса команд отлаживаемой программы поступают по входу 8 на вход схемы 17 сравнения. После совпадения адреса, поступившего по входу 8, с содержимым регистра 15, на выходе схемы сравнения 17 фор- fflpyeтcя соответствующий сигнал. По этому сигналу устанавливается триггер 18 и, тем самым, осуществляется подключение входа 4 к счетному входу счетчика 13. По сигналу, поступающему по входу 4 и свидетельствующему о поступлении команды, осуществляется модификация счетчика 13. Информация с выхода счетчика 13 поступает на один из входов схемы 16 сравнения, на другой .вход которой поступают данные с выходов блока 14, характеризующие количество-выполняемых команд до формирования первого сигнала прерывания. При совпадении содержимого счетчика 13 с данными на выходах блока

14 на выходе схемы сравнения формируется соответствующий сигнал, устанав ливаюпщй триггер 19. В результате

после установки триггера 19 формиру-

ется сигнал прерывания, поступающий

на вход 20. Одновременно осуществляется сброс счетчика 13 и триггера 9 и отключение входа 4 от входа счетчика 13. Кроме того, осуществляется модификация счетчика: 10, после чего на выходах блока 14 формируются данные, характеризующие количество выполняемых команд до формирования еле дующего сигнала прерьюания.

При переходе в подпрограмму обработки прерывания по сигналу на входе 1 осуществляется сброс триггера 19.

В процессе выполнения подпрограммы обработки прерывания осуществляется фиксация состояния отлаживаемой системы с последующим его просмотром.

После окончания выполнения подпрограммы по сигналу,.поступающему по входу 3, например, от пульта операто- ра, осуществляется установка триггера 9 и подключение шины 4 к счетному входу счетчика 13. Дальнейщая работа устройства осуществляется аналогично описанному выше,

Цри необходимости изменения моментов формирования сигналов прерывания на данном участке отлаживаемой программы осуществляется изменения содержимого блока 14. При необходимости отладки следующего участка программы

изменяется содержимое регистра 15,

I

Формула из, обретения

Устройство для формирования сигна- ла прерывания при отладке программ, содержащее первьй триггер, первую схему сравнения и первый счетчик, причем выход первого триггера является выходом прерьшания программы уст- ройства и соединен с первым входом установки нуля первого счетчика, вход начальной установки устройства соединен с вторым входом установки нуля первого счетчика и первым входом установки нуля первого триггера, вход сброса прерывания программь: устройства соединен с входом установки нуля первого триггера, информаВНИИПИ Заказ 4223/39 Тираж 672 Подписное Произв-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

ционный выход первого счетчика соединен с первым информационным входом первой схемы сравнения, выход равенства которой соединен с единичным входом первого триггера, отличающееся тем, что, с целью сокращения времени отладки программы в устройство введены второй и третий триггеры, второй счетчик, регистр, коммутатор, вторая схема сравнения, элемент И и блок оперативной памяти, причем вход начальной установки устройства соединен с первым единичным входом второго триггера, с нулевым входом третьего триггера, с нулевым установочным входом второго счетчика входы конца обработки прерывания, признака команды, первый адресный вход, информационный и второй адресный входы устройства соединены соответственно с вторым единичным входом второго триггера, с первым входом элемента И, с первым информационным входом коммутатора, с информационным входом регистра и первым информационным входом второй схемы сравнения, информационный выход регистра соединен с вторым информационным входом второй схемы сравнения, выход равенства которой соединен с единичным входом третьего триггера, выход которого соединен с вторьм входом элемен- та И, прямой вьпгод первого триггера соединен со счетным входом второго счетчика и нулевым входом второго триггера, прямой выход которого соединен с третьим входом элемента И, выход которого соединен с тактовым входом первого счетчика, вход признака .записи устройства соединен с вхог дом записи блока оперативной памяти, входом записи регистра и управляюпрш входом коммутатора, выход которого соединен с адресным входом блока оперативной памяти, информационньш вход устройства соединен с информационными входами блока оперативной памяти и регистра, выходы которых соединены с вторыми информационными входами первой и второй схем сравнения соответственно, выход второго счетчика соединен с вторым информационным входом коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки программ | 1988 |

|

SU1654827A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1999 |

|

RU2214621C2 |

| Устройство для отладки программ | 1982 |

|

SU1062708A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для отладки программ | 1982 |

|

SU1030805A1 |

Изобретение относится к вычислительной технике и может быть использовано для фор мирования сигнала прерывания при отладке программ. Цель изобретения - сокращение времени отладки программ. Устройство содержит триггер 9, второй счетчик 10, элемент И 11, коммутатор 12, первый счетчик 13, блок оперативной памяти 14, регистр 15, схемы сравнения 16 и 17, триггеры 18 и 19, выход 20 прерывания. Изобретение заключается в обеспечении моментов формирования сигналов прерывания без модификации программы и, кроме того, сокращении количества команд отлаживаемой программы . 1 ил.

| Устройство для контроля времениВыпОлНЕНия пРОгРАММ | 1978 |

|

SU798851A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования сигнала прерывания при отладке программ | 1983 |

|

SU1124315A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-23—Публикация

1985-10-03—Подача