1

(21)4618308/24

(22)23.11.88

(46) 07.06.91.БГОП.

(71)Всесоюзный (- чно-исследоватеяьсжий институт электромеханики

(72)В.Б.Иуанчук, С.Я.Куцаков, М.В.Протопопов. В.Н.Степанов и В.Е.Пызлов (53)681.3(088.8)

(56)Авторское свидетельство СССР № 1030805, кл. G 06 F 11 /22. 1932.

Авторское свидетельство СССР № 1383372,кл. G 06 F 11/28. 1986.

(54) УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ

(57)Изобретение относится к автоматике и вычислительной технике и может использоваться при отладке программ ш кроЭВМ. Цель - расширение функциональных возможностей за счет введения режима останова программы без прерывания работы ЭВМ и перевода ее в режим ожидания. Устройство содержит блок оперативной памяти трассы, два счетчика адреса, два дешифратора команд, счетчик циклов, элемент ИЛИ, элемент ИЛИ-НЕ, блок оперативной памяти точек останова, блок постоянной памяти останова, два регистра адреса, два триггера, элемент И. Устройство обеспечивает выполнение двух режимов работы: записи/чтения трассы исполнения программы и останова отлаживаемой программы по адресу или области адресов без перевода ЭВМ в режим ожидания. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство отладки микропрограммных блоков | 1988 |

|

SU1541617A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

Изобретение относится к автоматике и вычислительной технике и может использоваться при разработке аппаратуры по отладке программ микроЭВМ.

Цель изобретения - расширение функциональных возможностей устройства за счет введения режима останова программы без прерывания работы ЭВМ и перевода ее в режим ожидания.

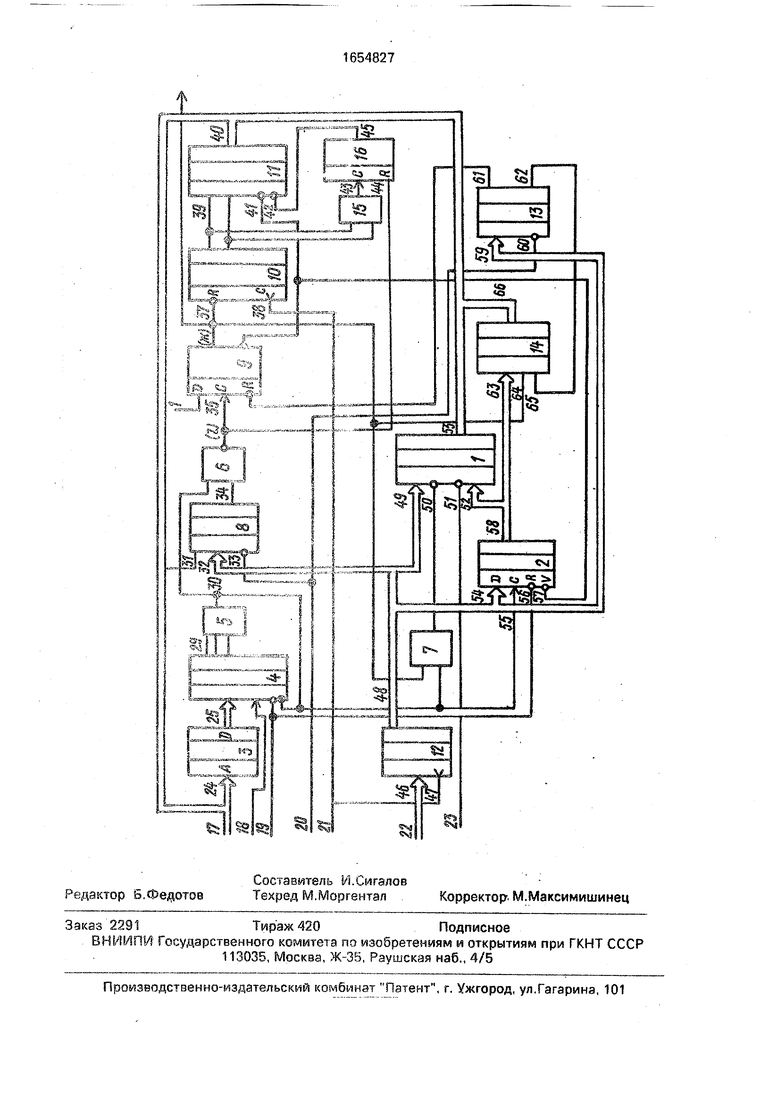

На чертеже изображена функционалы ная схема устройства.

Устройство для отладки программ содержит блок 1 оперативной памяти трасс, первый счетчик 2 адреса, дешифратор 3 команд, счетчик 4 циклов, элемент ИЛИ 5, элемент ИЛИ-НЕ 6, элемент ИЛИ 7, блок 8 оперативной памяти точек останова, первый триггер 9, второй счетчик 10 адреса, блок 11 постоянной памяти останова, первый регистр 12 адреса, дешифратор 13, второй регистр 14 адреса, элемент И 15, второй триггер 16, шину 17 данных, вход признака чтения команды, вход 19 начальной установки устройства, вход 20 сигнала записи устройства, вход 21 сигнала признака адреса, шина 22 адресов устройства, вход 23 сигнала чтения устройства, вход 24 адресный первого дешифратора 3, выход 25 дешифратора 3, счетный вход 26 счетчика 4 циклов команд, вход 27 установки в Исходное состояние счетчика 4, вход 28 загрузки счетчика 4, информационные входы 29 счетчика 4, выход 30 элемента ИЛИ 5, являющийся выходом сигнала, сопровождающего чтение кодов команд, информационный вход 31 блока 8, вход 32 адреса блока 8, вход 33 записи блока 8, информационный вход 34 блока 8, счетный вход 35 триггера 5,

О

Z

00

ю ч

вход 36 установки в исходное состояние триггера 9, вход 37 установки в исходное состояние счетчика 10 адресов, счетный вход 38 счетчика 10, адресные входы 39 блока И, информационные входы 40 блока 11, вход 41 выбора блока 11, вход 42 блога 11 счетный вход 43 триггера 16, вход 44 установки в исходное состояние триггера 16, выход 45 триггера 9, информационный вход 48 регистра 12, вход 47 установки регистра 12, информационные выходы 48 регистра 12, информационные выходы 49 блока 1, вход 50 записи блока 1, вход 51 чтения блока 1, являющийся входом чтения устройства, адресные входы 52 блока 1, информационные выходы 53 блока 1, информационные входы 54 счетчика 2 адреса, счетный вход 55 счетчика 2, вход 56 установки в исходное состояние счетчика 2, вход 57 загрузки счет- - ика 2, информационные выходы 58 счетчика 2, входа 59 дешифратора 13, вход 60 разрешения дешифратора 13, выходы 61, 62 дешифратора 13, информационный вход 63 регистра 14, вход 64 установки регистра 14. вход 65 разрешения выходов регистра 14, информационный выход 66 регистра 14, выход 67 сигнала запрета обращения к блоку с отлаживаемой программой.

Устройство обеспечивает выполнение двух режимов работы: записи/чтения трассы исполнения программы и останова отлаживаемой программы по адресу или области адресов без перевода ЭВМ в режим ожидания.

8 режиме записи трассы на адресные входы дешифратора 3 поступают данные с шины данных ЭВМ (а качестве дешифратора 3 используется ПЗУ с малым временем эыборки, например К556РТ4, и записанным в него числом циклов исполнения команд ЭВМ по адресам, которые являются кодами этих команд).

Доичный код, представляющий число циклов, с выхода дешифратора 3 поступает на информационные входы счетчика 4 циклов 4, которые загружаются при логическом нуле на входе 28. Логический нуль на вход 28 может выставляться по сигналу низкого уровня установки в исходное состояние на входе 19 устройства. Тогда входы 29 счетчика 4 обнуляются, и логический нуль устанавливается на выходе элемента ИЛИ 5, или в конце счета числа циклов по синхросигналу, поступающему на вход 26. Сигнал загрузки счетчика 4 является сопровождающим чтение кода команд ЭВМ, По этому сигналу, поступающему через элемент ИЛИ 7, при логическом нуле на другом входе этого элемента, на вход блока 1 происходит запись информации с адресной шины, соответствующей значению счетчика команд ЭВМ, по адресам, определяемым счетчиком 2 адреса, пересчет которых идет по сигналу с элемента ИЛИ 5. Чтение значения счетчика

команд из блока 1 происходит по сигналу чтения, поступающему на вход 51 при логической единице на входе 50 и логическом нуле на входе 57 загрузки счетчика 2 адреса, которые выставляются после формирова0 ния сигнала останова. Чтение производится по адресам, определяемым состоянием адресной шины 48, адреса выставляются на адресных входах 52 блока 1. Выход 53 блока 1 подсоединен к шине 17 данных. Опреде5 лить адрес последней ячейки блока 1, в которую записывалась информация, возможно при чтении регистра 14, в котором по сигналу останова защелкнулся этот адрес, Обращение к регистру 14 произво0 дится посредством дешифратора 13 сигналов обращения.

Режим останова отлаживаемой программы делится на два подрежима: формирование точек останова и сам останов

5 (см.фиг.2 и 3).

Точки останова формируются в блоке 8 оперативной памяти записью нуля по адресам останова, выставляемым по адресной шине 48 ЭВМ на входе 32. При исполнении

0 отлаживаемой программы и возникновении условий останова, т.е. выставлений на адресной шине 48 адреса останова, на выходе 34 блока 8 памяти устанавливается логический нуль, который через элемент ИЛИ-НЕ

5 б при логическом нуле на другом его входе, характеризующем чтение кода команд ЭВМ, перебрасывает триггер 9, а также поступая на вход 44 сброса триггера 16, устанавливает его в исходное состояние. Сигнал

0 с прямого выхода триггера 9, поступающий на вход 37 счетчика 10 адреса, переводит счетчик из исходного состояния в состояние счета по сигналам признака адреса, поступающим на его счетный вход 38, запрещает

5 запись в блок 1 и защелкивает на регистре 14 значение последней записанной ячейки блока 1. Сигнал с инверсного выхода триггера 9, поступая на вход 41 блока 11 постоянной памяти, разрешает его выбор и,

0 поступая на вход 57 счетчика 2, переводит его в режим загрузки.

Информация, записанная в нулевую ячейку блока 11, не представляющая собой код трехбайтной команды перехода, появ5 ляется на входе 40 блока 11 сразу после выставления ЭВМ адреса, соответствующего точке останова и переходу синхросигнала, по которому ЭВМ читает код команды. Выставление на шине данных информации из следующих двух ячеек памяти происходит по сигналам 20 признака адреса. После считывания ЭВМ всей команды перехода к подпрограмме обработки останова на выходах счетчика 10 выставляются сигналы высокого уровня, которые через элемент И 15, поступая на вход 43 триггера 16, перебрасывают его в единичное состояние, и тем самым запрещается вывод информации блоком 11 на шину данных. Этим обеспечивается возможность работы с шиной данных во время выполнения подпрограммы обработки останова. В конце подпрограммы обработки останова должна присутствовать команда, обеспечивающая с помощью дешифратора 13 выдачу сигнала сброса останова, который сбрасывает в исходное состояние триггер 9, тем самым разрешая дальнейшее обращение к блоку с отлаживаемой программой.

Таким образом, вместо выполняемой команды по адресу точки останова аппарат- но подставляется команда обработки точки останова, что обеспечивает останов отлаживаемой программы без останова ЭВМ.

Формула изобретения Устройство для отладки программ, содержащее блок оперативной памяти трасс, первый счетчик адреса, счетчик циклов пер-. вый элемент ИЛИ и первый триггер, причем информационные выходы первого счетчика адреса соединены с адресными входами блока оперативной памяти трасс, вход чтения устройства соединен с входом чтения блока оперативной памяти трасс, вход признака чтения команды устройства соединен со счетным входом счетчика циклов, информационные выходы которого соединены с входами первого элемента ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей за счет введения режима останова программы без прерывания работы отлаживаемой ЭВМ и перевода ее в режим ожидания, в него введены дешифратор команд, дешифратор адреса, второй элемент ИЛИ, блок оперативной памяти точек останова, элемент ИЛИ -НЕ, второй счетчик адреса, блок постоянной памяти, элемент И, второй триггер, первый и второй регистры адреса, причем информационный вход блока оперативной памяти точек останова, выходы блока оперативной памяти трасс, второго регистра адреса и блока постоянной памяти, входы дешифратора команд подключены к шине данных устройства, выходы

дешифратора команд соединены с информационными входами счетчика циклов, вход начальной установки устройства соединен с нулевыми установочными входами первого 5 счетчика адреса и счетчика циклов, выход первого элемента ИЛИ соединен с первым входом элемента ИЛИ-НЕ, входом загрузки счетчика циклов, первым входом второго элемента ИЛИ и счетным входом первого

0 счетчика адреса, выход первого регистра адреса соединен с адресным входом блока оперативной памяти точек останова, информационными входами блока оперативной памяти трасс и первого счетчика адреса и

5 входом дешифратора адреса,вход записи устройства соединен с тактовым входом дешифратора адреса и входом записи блока оперативной памяти точек останова, выход которого соединен с вторым входом элемен0 та ИЛИ-НЕ, выход которого соединен со счетным входом первого триггера и нулевым входом второго триггера, первый и второй выходы дешифратора адреса соединены соответственно с нулевым вхо5 дом первого триггера и входом разрешения записи второго регистра адреса, информационный вход первого триггера соединен с шиной единичного потенциала устройства, прямой выход первого триггера соединен с

0 нулевым входом второго счетчика адресов, вторым входом второго элемента ИЛИ, вхо- . дом записи второго регистра адреса и является выходом запрета обращения устройства, инверсный выход первого триг5 гера соединен с входом обращения блока постоянной памяти и входом разрешения записи первого счетчика адреса, выход которого соединен с информационным входом второго регистра адреса, вход признака

0 адреса устройства соединен со счетным входом второго счетчика адреса и входом записи первого регистра адреса, адресные входы устройства соединены с информационными входами первого регистра адреса,

5 выход второго элемента ИЛИ соединен с входом записи блока оперативной памяти трасс, выходы второго счетчика адреса соединены с адресными входами блока постоянной памяти и входами элемента И, выход

0 КОТОРОГО соединен с тактовым входом второго триггера, информационный вход, второго триггера соединен с шиной единичного потенциала устройства, прямой выход второго триггере соединен с входом

5 разрешения чтения блока постоянной памяти.

Авторы

Даты

1991-06-07—Публикация

1988-11-23—Подача