Изобретение относится к вычислительной технике и предназначено для отладки микропроцессорных систем, построенных на базе микропроцессоров, однокристальных микроконтроллеров, процессоров цифровой обработки сигналов.

Известен внутрисхемный эмулятор, содержащий блок интерфейса системы проектирования, блок регистров адреса, блок управления записью/чтением, блок памяти и блок интерфейса отлаживаемой системы [1].

Известный эмулятор не обеспечивает полной эмуляции микроконтроллеров семейства MCS51 поскольку в нем используется метод прерывания. Метод прерывания ограничивает использование в отлаживаемой системе следующих ресурсов микроконтроллера: вектора прерывания, некоторой области стека, некоторой области памяти программ. Кроме того, в силу свойства известного эмулятора использовать для организации пошагового режима метода вызова команд основной программы в промежутках между вызовами прерываний, известный эмулятор не может осуществлять указанную функцию при эмуляции микроконтроллеров, в которых такая возможность отсутствует. Использование метода прерываний отлаживаемой программы в известном эмуляторе ограничивает сферу его применения семействами микроконтроллеров с внешними выводами прерываний, в том числе MCS51.

Наиболее близким к заявляемому является внутрисхемный эмулятор, содержащий блок интерфейса системы проектирования, блок регистров адреса, блок регистров управления, блок управления записью/чтением, блок памяти, блок формирования команды холостого цикла работы и блок интерфейса отлаживаемой системы, в которых соответствующие входы и выходы блока интерфейса системы проектирования являются входами и выходами эмулятора для подключения к входам и выходам системы проектирования, информационный вход и вход записи блока регистров адреса соединены с соответствующими выходами блока интерфейса системы проектирования, информационный вход и вход записи блока регистров управления соединены с соответствующими выходами блока интерфейса системы проектирования, вход управления записью/чтением блока памяти соединен с соответствующим выходом блока управления записью/чтением, выход блока формирования команды холостого цикла работы соединен с информационным входом-выходом блока интерфейса отлаживаемой системы, соответствующие входы и выходы которого являются входами и выходами эмулятора для подключения к входам и выходам отлаживаемой системы [2].

В известном эмуляторе применен метод трассировки с ограниченным числом точек останова. Ограничение числа точек останова обусловлено особенностями организации и недостаточным объемом памяти для их хранения. Кроме того, известное устройство не позволяет эмулировать память данных, так как не имеет соответствующих технических средств. Между тем, при решении сложных программно-аппаратных проблем часто возникает необходимость эмуляции памяти данных. При обмене информацией между системой проектирования и интерфейсом отлаживаемой системы необходимо многократная перезапись служебных программ в блок памяти вспомогательных процедур, что ограничивает быстродействие эмулятора. В силу методических ограничений в известном эмуляторе не может быть реализован пошаговый режим отладки. Вышеуказанные причины не позволяют ускорить отладку программно-аппаратных систем, в том числе сложных, имеющих множественные ошибки, допущенные при разработке, и являются причинами ограничения функциональных возможностей известного эмулятора. Блок формирования команды холостого цикла работы тесно связан с системой команд микроконтроллеров семейства MCS51 (8051), что лишает возможности модифицировать эмулятор для работы с микроконтроллерами других семейств.

Согласно изобретению предлагается внутрисхемный эмулятор для отладки микропроцессоров, микроконтроллеров и процессоров цифровой обработки сигналов различных типов.

Технический результат, достигаемый изобретением, заключается в получении такого универсального набора функциональных свойств, который делает возможной эмуляцию более широкого спектра семейств микроконтроллеров и микропроцессоров.

Достижение технического результата обеспечивается тем, что во внутрисхемном эмуляторе, содержащем блок интерфейса системы проектирования, блок регистров адреса, блок регистров управления, блок управления записью/чтением, блок памяти, блок формирования команды холостого цикла работы и блок интерфейса отлаживаемой системы, в которых соответствующие входы и выходы блока интерфейса системы проектирования являются входами и выходами эмулятора для подключения к входам и выходам системы проектирования, информационный вход и вход записи блока регистров адреса соединены с соответствующими выходами блока интерфейса системы проектирования, информационный вход и вход записи блока регистров управления соединены с соответствующими выходами блока интерфейса системы проектирования, вход управления записью/чтением блока памяти соединен с соответствующим выходом блока управления записью/чтением, выход блока формирования команды холостого цикла работы соединен с информационным входом-выходом блока интерфейса отлаживаемой системы, соответствующие входы и выходы которого являются входами и выходами эмулятора для подключения к входам и выходам отлаживаемой системы, дополнительно введены коммутатор шин, анализатор кода, блок останова, блок переадресации, блок захвата адреса и блок сравнения адреса, в которых первый и второй адресные входы коммутатора шин соединены соответственно с выходом блока регистров адреса и первым выходом блока переадресации, первый и второй информационные входы - выходы коммутатора шин соединены с соответствующими входами - выходами блока интерфейса системы проектирования и блока интерфейса отлаживаемой системы, третий информационный вход-выход коммутатора шин соединен с информационным входом-выходом блока памяти, управляющий вход коммутатора шин соединен с соответствующим выходом блока управления записью/чтением, адресный выход коммутатора шин соединен с адресным входом блока памяти, информационные входы - выходы анализатора кода, блока останова, блока переадресации, блока захвата адреса, блока сравнения адреса и блока формирования команды холостого цикла работы соединены с информационным входом-выходом блока интерфейса системы проектирования, адресные входы анализатора кода, блока останова, блока переадресации, блока захвата адреса, блока сравнения адреса и блока формирования команды холостого цикла работы соединены с выходом блока регистров адреса, первые управляющие входы блока управления записью/чтением, анализатора кода, блока останова, блока переадресации, блока захвата адреса, блока формирования команды холостого цикла работы и управляющий вход блока сравнения адреса соединены с соответствующим выходом блока интерфейса системы проектирования, первый и второй информационные входы анализатора кода соединены соответственно с информационным входом-выходом блока интерфейса отлаживаемой системы и вторым выходом блока переадресации, выход анализатора кода соединен с третьим управляющим входом блока останова, информационные входы блока переадресации, блока захвата адреса и блока сравнения адреса соединены с адресным выходом блока интерфейса отлаживаемой системы, вторые управляющие входы блока останова и блока переадресации и управляющий вход блока интерфейса отлаживаемой системы соединены с выходом блока регистров управления, первый, второй и третий выходы блока останова соединены соответственно со вторым управляющим входом блока захвата адреса, с третьим управляющим входом блока переадресации и со вторым управляющим входом блока формирования команды холостого цикла работы, четвертый управляющий вход блока останова соединен с выходом блока сравнения адреса, первый выход блока переадресации соединен с информационным входом блока останова, второй выход блока переадресации соединен со вторыми управляющими входами блока управления записью/чтением и блока формирования команды холостого цикла работы, четвертый управляющий вход блока переадресации соединен с управляющим выходом блока интерфейса отлаживаемой системы.

Технический результат достигается за счет применения во внутрисхемном эмуляторе метода останова выполнения отлаживаемой программы для контроля за процессом ее выполнения и диагностики промежуточных результатов. Для этого управление временно передается служебной программе - монитору. Эмулятор снабжен памятью точек останова, достаточной для установки точек останова на любых доступных пользователю адресах памяти программ. Это значительно ускоряет процесс отладки сложных программ, поскольку становится возможным контролировать выполнение отдельных мелких участков программы без многократных ее прогонов с переустановкой точек останова. По достижению отлаживаемой программой точки останова процессор переходит к выполнению холостого цикла работы. Во время холостого цикла работы происходит переключение памяти с отлаживаемой программой на память с монитором. Переключение происходит прозрачно для процессора, при этом не задействуются какие-либо ресурсы эмулируемой системы. В случае необходимости, монитор может быть расположен и в адресном пространстве отлаживаемой системы. Монитор реализован в виде набора подпрограмм, постоянно находящихся в памяти эмулятора. Монитор позволяет производить чтение внутренних регистров микроконтроллера (в том числе указателя стека и счетчика команд), а также внешних ресурсов (памяти, устройств ввода-вывода). В случае необходимости изменить состояние некоторых ресурсов эмулятора монитор соответствующим образом модифицируется. Для организации режима выполнения отлаживаемой программы с точками останова и пошагового режима используется анализатор кода. Весьма полезным для отладки является пошаговый режим, который позволяет выполнять отлаживаемую программу по отдельным командам и после каждой команды контролировать состояние системы. Блок переадресации позволяет гибко конфигурировать распределение памяти между эмулятором и отлаживаемой системой, а также эмулировать различные участки памяти в случаях, когда адресное пространство отлаживаемой системы превышает объем внутренней памяти эмулятора. В целях обеспечения возможности настройки эмулятора на различные микропроцессоры блоки эмулятора обладают свойством программируемости. Для обеспечения возможности эмуляции различных типов микроконтроллеров блок интерфейса отлаживаемой системы выполнен в виде сменного модуля.

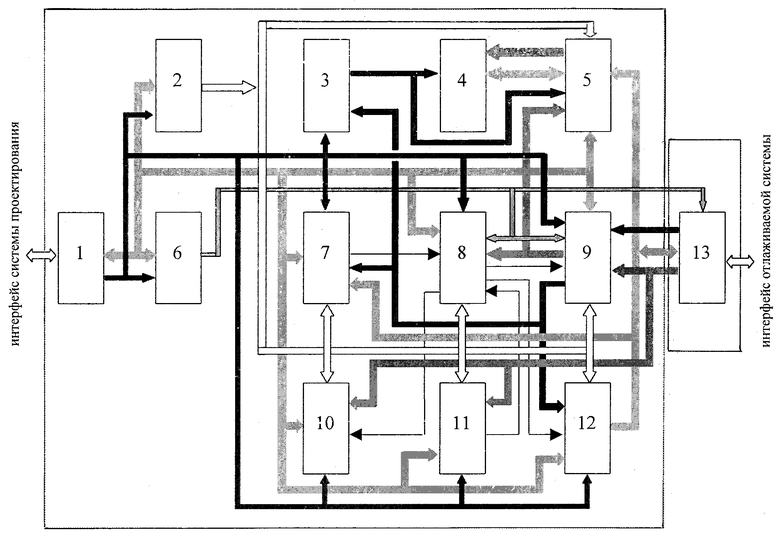

На чертеже приведена структурная схема внутрисхемного эмулятора.

Внутрисхемный эмулятор содержит блок 1 интерфейса системы проектирования, блок 2 регистров адреса, блок 3 управления записью/чтением, блок 4 памяти, коммутатор шин 5, блок 6 регистров управления, анализатор кода 7, блок 8 останова, блок 9 переадресации, блок 10 захвата адреса, блок 11 сравнения адреса, блок 12 формирования команды холостого цикла работы, блок 13 интерфейса отлаживаемой системы, причем соответствующие входы и выходы блока 1 интерфейса системы проектирования являются входами и выходами эмулятора для подключения к входам и выходам системы проектирования, информационный вход и вход записи блока 2 регистров адреса соединены с соответствующими выходами блока интерфейса 1 системы проектирования, информационный вход и вход записи блока 6 регистров управления соединены с соответствующими выходами блока 1 интерфейса системы проектирования, вход управления записью/чтением блока 4 памяти соединен с соответствующим выходом блока 3 управления записью/чтением, выход блока 12 формирования команды холостого цикла работы соединен с информационным входом-выходом блока 13 интерфейса отлаживаемой системы, соответствующие входы и выходы которого являются входами и выходами эмулятора для подключения к входам и выходам отлаживаемой системы, первый и второй адресные входы коммутатора шин 5 соединены соответственно с выходом блока 2 регистров адреса и первым выходом блока 9 переадресации, первый и второй информационные входы - выходы коммутатора шин 5 соединены с соответствующими входами - выходами блока 1 интерфейса системы проектирования и блока 13 интерфейса отлаживаемой системы, третий информационный вход-выход коммутатора шин 5 соединен с информационным входом-выходом блока 4 памяти, управляющий вход коммутатора шин 5 соединен с соответствующим выходом блока 3 управления записью/чтением, адресный выход коммутатора шин 5 соединен с адресным входом блока 4 памяти, информационные входы - выходы анализатора кода 7, блока 8 останова, блока 9 переадресации, блока 10 захвата адреса, блока 11 сравнения адреса и блока 12 формирования команды холостого цикла работы соединены с информационным входом-выходом блока 1 интерфейса системы проектирования, адресные входы анализатора кода 7, блока 8 останова, блока 9 переадресации, блока 10 захвата адреса, блока 11 сравнения адреса и блока 12 формирования команды холостого цикла работы соединены с выходом блока 2 регистров адреса, первые управляющие входы блока 3 управления записью/чтением, анализатора кода 7, блока 8 останова, блока 9 переадресации, блока 10 захвата адреса, блока 12 формирования команды холостого цикла работы и управляющий вход блока 11 сравнения адреса соединены с соответствующим выходом блока 1 интерфейса системы проектирования, первый и второй информационные входы анализатора кода 7 соединены соответственно с информационным входом-выходом блока 13 интерфейса отлаживаемой системы и вторым выходом блока 9 переадресации, выход анализатора кода 7 соединен с третьим управляющим входом блока 8 останова, информационные входы блока 9 переадресации, блока 10 захвата адреса и блока 11 сравнения адреса соединены с адресным выходом блока 13 интерфейса отлаживаемой системы, вторые управляющие входы блока 8 останова и блока 9 переадресации и управляющий вход блока 13 интерфейса отлаживаемой системы соединены с выходом блока 6 регистров управления, первый, второй и третий выходы блока 8 останова соединены соответственно со вторым управляющим входом блока 10 захвата адреса, с третьим управляющим входом блока 9 переадресации и со вторым управляющим входом блока 12 формирования команды холостого цикла работы, четвертый управляющий вход блока 8 останова соединен с выходом блока 11 сравнения адреса, первый выход блока 9 переадресации соединен с информационным входом блока 8 останова, второй выход блока 9 переадресации соединен со вторыми управляющими входами блока 3 управления записью/чтением и блока 12 формирования команды холостого цикла работы, четвертый управляющий вход блока 9 переадресации соединен с управляющим выходом блока 13 интерфейса отлаживаемой системы.

К блоку 1 интерфейса системы проектирования подключается инструментальная ЭВМ. Блок 2 регистров адреса используется для адресации блоков эмулятора при доступе к ним со стороны системы проектирования. Блок 3 управления записью/чтением вырабатывает управляющие сигналы, необходимые для доступа к блоку 4 памяти как из системы проектирования, так и из отлаживаемой системы. Блок 4 памяти предназначен для хранения программ и данных отлаживаемой системы, а также системной программы - монитора. Коммутатор шин 5 служит для переключения шин адресов и данных при обращении к блоку 4 памяти со стороны системы проектирования и отлаживаемой системы. Необходимость в коммутации шин вызвана тем, что блок 4 памяти не допускает одновременного доступа по двум парам шин. На выходах блока 6 регистров управления формируются управляющие сигналы, необходимые для управления процессом эмуляции. Анализатор кода 7 выполняет функцию определения первых байтов команд в отлаживаемых программах. Для достижения технического результата анализатор кода 7 имеет возможность настройки на целевой процессор отлаживаемой системы. Блок 8 останова содержит информацию об установленных точках останова и вырабатывает сигналы для останова отлаживаемой программы и переключения на выполнение монитора по достижению отлаживаемой программой одной из точек останова. Блок 9 переадресации служит для распределения адресов памяти между эмулятором и отлаживаемой системой, а также позволяет эмулировать различные области памяти в адресном пространстве отлаживаемой системы. Блок 10 захвата адреса предназначен для фиксации состояние шины адреса в момент достижения отлаживаемой программой точки останова. Блок 11 сравнения адреса отслеживает состояние адресной шины отлаживаемой системы и вырабатывает сигнал в случае равенства текущего состояния и наперед заданного значения. Блок 12 формирования команды холостого цикла работы предназначен для перевода процессора отлаживаемой системы в холостой цикл работы и установки программного счетчика на начало монитора. При этом процессор отлаживаемой системы выполняет коды, хранящиеся в блоке 12 формирования команды холостого цикла работы, и не обращается к блоку 4 памяти, что делает возможным обращение к блоку 4 памяти со стороны системы проектирования. Для достижения технического результата блок 12 формирования команды холостого цикла работы имеет возможность настройки на целевой процессор отлаживаемой системы. Блок 13 интерфейса отлаживаемой системы служит для выполнения программ и обеспечения интерфейса отлаживаемой системы. Для достижения технического результата блок 13 интерфейса отлаживаемой системы выполнен в виде сменного модуля, включает в себя целевой микроконтроллер или микропроцессор, соответствующий ему интерфейс отлаживаемой системы и средство для подключения к основному модулю эмулятора (разъем). При необходимости в некоторых частных случаях частичной эмуляции того или иного микроконтроллера или микропроцессора блок интерфейса отлаживаемой системы выполняется в виде соединительных шин и разъемов.

Внутрисхемный эмулятор работает следующим образом.

В начале сеанса работы происходит инициализация блоков эмулятора. Затем коды программ и данных пользователя, а также монитора, записываются в блок 4 памяти, а в блок 8 останова заносится информация об установленных точках останова. Для адресации блоков эмулятора и ячеек памяти внутри блоков, адреса, выставляемые системой проектирования, поступают в блок 2 регистров адреса, а с его выхода - на внутреннюю адресную шину эмулятора. Внутренние шина данных и шина управления эмулятора формируются на выходах блока 1 интерфейса системы проектирования. Для управления процессом загрузки блока 4 памяти используются соответствующие выходы блока 3 управления записью/чтением. При отладке микропроцессорных устройств часто возникает потребность совмещать память эмулятора и память, расположенную в отлаживаемой системе, в едином адресном пространстве. Для распределения адресов памяти эмулятора и памяти отлаживаемой системы соответствующим образом настраивается блок 9 переадресации. В соответствии с выбранным типом целевого процессора настраиваются анализатор кода 7 и блок 12 формирования команды холостого цикла работы. В блок 11 сравнения адреса заносится значение состояния шины адреса отлаживаемой системы, соответствующее адресу начала монитора. Далее управление передается блоку 13 интерфейса отлаживаемой системы, содержащему целевой микропроцессор. Для этого на выходе блока 6 регистров управления формируется сигнал запуска процессора. С этого момента процессор блока 13 начинает выполнение программы, записанной в блоке 4 памяти.

Выполнение происходит в одном из режимов - реального времени, пошаговом, с точками останова. Выполнение программы в режиме реального времени полностью аналогично выполнению программы в отлаживаемой системе без эмулятора, однако есть возможность остановить программу по желанию пользователя.

Выполнение программы с точками останова происходит следующим образом. Программа запускается на выполнение и до достижения точки останова работает аналогично режиму реального времени. Во время работы программы анализатор кода 7 и блок 8 останова производят анализ текущего состояния шин адреса и данных, и если адрес, выставленный процессором, соответствует одной из установленных точек останова, а на шине данных должен появится код первого байта соответствующей команды, то на выходе блока 8 останова формируется сигнал, который поступает на блок 10 захвата адреса. По этому сигналу блок 10 захвата адреса запоминает текущее состояние адресной шины отлаживаемой системы. С другого выхода блока 8 останова на управляющий вход блока 12 формирования команды холостого цикла работы поступает сигнал, разрешающий выдачу команды установки программного счетчика, записанной во внутренних регистрах блока 12, на шину данных отлаживаемой системы. Таким образом, процессор блока 13 выполняет команду установки программного счетчика на начало программы монитора. Как только на адресной шине отлаживаемой системы появляется адрес начала монитора, блок 11 сравнения адреса вырабатывает соответствующий сигнал, который поступает на вход блока 8 останова. Блок 8 останова отключает блок 12 формирования команды холостого цикла работы от шины данных отлаживаемой системы и разрешает доступ к монитору путем воздействия на блок 9 переадресации. Монитор может находится как в адресном пространстве отлаживаемой системы, так и вне его. В последнем случае все адресное пространство доступно для размещения программ и данных пользователя. При выполнении монитора данные о состояниях внутренних ресурсов отлаживаемой системы поступают в блок 4 памяти. При необходимости модификации состояния некоторых ресурсов система проектирования при помощи блока 6 регистров управления подает сигнал, разрешающий холостой режим работы процессора. В этом случае отлаживаемая система освобождает блок 4 памяти и система проектирования соответствующим образом модифицирует монитор. Если необходимо продолжить выполнение отлаживаемой программы, система проектирования считывает адрес возврата, сохраненный в блоке 10 захвата адреса, записывает в блок 4 памяти команду установки программного счетчика в соответствующее состояние по адресу начала монитора и заносит адрес возврата в основную программу в блок 11 сравнения адреса. Далее, при помощи блока 6 регистров управления, сигнал формирования холостого цикла работы снимается и процессор отлаживаемой системы возвращается к выполнению монитора. Если по адресу начала монитора находится команда установки программного счетчика в соответствии с адресом возврата в отлаживаемую программу, адрес возврата появляется на адресной шине отлаживаемой системы и блок 11 сравнения адреса формирует управляющий сигнал, поступающий на вход блока 8 останова. По этому сигналу блок 8 останова формирует управляющее воздействие для блока 9 переадресации. С этого момента на выходах блока 9 переадресации появляются адреса, соответствующие отлаживаемой программе.

Пошаговый режим осуществляется аналогично режиму с точкам останова, с той разницей, что переключение к выполнению монитора происходит по достижению первого байта каждой команды отлаживаемой программы, о чем свидетельствует сигнал на выходе анализатора кода 7.

При использовании предлагаемого устройства в качестве эмулятоpa различных однокристальных микропроцессоров и микроконтроллеров изменяется только сменный модуль, состав и принципы работы остальных блоков эмулятора остаются неизменными.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Development Systems Handbook. - N.Y. Intel. Corp., 1984, order number 280017-001, pp.5-1-5-7, fig.1.

2. Авторское свидетельство СССР 1589274, МПК G 06 F 9/44, оп. 30.08.90 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1996 |

|

RU2110833C1 |

| Внутрисхемный эмулятор | 1988 |

|

SU1589274A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство отладки микропрограммных блоков | 1988 |

|

SU1541617A1 |

Изобретение относится к вычислительной технике и предназначено для отладки микропроцессорных систем, построенных на базе микропроцессоров, микроконтроллеров, процессоров цифровой обработки сигналов. Техническим результатом является обеспечение возможности выполнения внутрисхемным эмулятором эмуляции широкого спектра семейств микроконтроллеров и микропроцессоров. Для этого заявленный эмулятор содержит блоки интерфейсов системы проектирования и отлаживаемой системы, блоки регистров адреса и управления, блок управления записью/чтением, блок памяти, блок формирования команды холостого цикла работы, коммутатор шин, анализатор кода, блок переадресации, блок захвата адреса и блок сравнения адреса. 1 ил.

Внутрисхемный эмулятор, содержащий блок интерфейса системы проектирования, блок регистров адреса, блок регистров управления, блок управления записью/чтением, блок памяти, блок формирования команды холостого цикла работы и блок интерфейса отлаживаемой системы, в которых соответствующие входы и выходы блока интерфейса системы проектирования являются входами и выходами эмулятора для подключения к входам и выходам системы проектирования, информационный вход и вход записи блока регистров адреса соединены с соответствующими выходами блока интерфейса системы проектирования, информационный вход и вход записи блока регистров управления соединены с соответствующими выходами блока интерфейса системы проектирования, вход управления записью/чтением блока памяти соединен с соответствующим выходом блока управления записью/чтением, выход блока формирования команды холостого цикла работы соединен с информационным входом - выходом блока интерфейса отлаживаемой системы, соответствующие входы и выходы которого являются входами и выходами эмулятора для подключения к входам и выходам отлаживаемой системы, отличающийся тем, что дополнительно содержит коммутатор шин, анализатор кода, блок останова, блок переадресации, блок захвата адреса и блок сравнения адреса, в которых первый и второй адресные входы коммутатора шин соединены соответственно с выходом блока регистров адреса и первым выходом блока переадресации, первый и второй информационные входы - выходы коммутатора шин соединены с соответствующими входами - выходами блока интерфейса системы проектирования и блока интерфейса отлаживаемой системы, третий информационный вход - выход коммутатора шин соединен с информационным входом - выходом блока памяти, управляющий вход коммутатора шин соединен с соответствующим выходом блока управления записью/чтением, адресный выход коммутатора шин соединен с адресным входом блока памяти, информационные входы - выходы анализатора кода, блока останова, блока переадресации, блока захвата адреса, блока сравнения адреса и блока формирования команды холостого цикла работы соединены с информационным входом - выходом блока интерфейса системы проектирования, адресные входы анализатора кода, блока останова, блока переадресации, блока захвата адреса, блока сравнения адреса и блока формирования команды холостого цикла работы соединены с выходом блока регистров адреса, первые управляющие входы блока управления записью/чтением, анализатора кода, блока останова, блока переадресации, блока захвата адреса, блока формирования команды холостого цикла работы и управляющий вход блока сравнения адреса соединены с соответствующим выходом блока интерфейса системы проектирования, первый и второй информационные входы анализатора кода соединены соответственно с информационным входом - выходом блока интерфейса отлаживаемой системы и вторым выходом блока переадресации, выход анализатора кода соединен с третьим управляющим входом блока останова, информационные входы блока переадресации, блока захвата адреса и блока сравнения адреса соединены с адресным выходом блока интерфейса отлаживаемой системы, вторые управляющие входы блока останова и блока переадресации и управляющий вход блока интерфейса отлаживаемой системы соединены с выходом блока регистров управления, первый, второй и третий выходы блока останова соединены соответственно со вторым управляющим входом блока захвата адреса, с третьим управляющим входом блока переадресации и со вторым управляющим входом блока формирования команды холостого цикла работы, четвертый управляющий вход блока останова соединен с выходом блока сравнения адреса, первый выход блока переадресации соединен с информационным входом блока останова, второй выход блока переадресации соединен со вторыми управляющими входами блока управления записью/чтением и блока формирования команды холостого цикла работы, четвертый управляющий вход блока переадресации соединен с управляющим выходом блока интерфейса отлаживаемой системы.

| Внутрисхемный эмулятор | 1988 |

|

SU1589274A1 |

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1996 |

|

RU2110833C1 |

| Внутрисхемный эмулятор | 1988 |

|

SU1615715A1 |

| US 5630102 А, 13.05.1997 | |||

| US 4954942 А, 04.09.1990. | |||

Авторы

Даты

2003-10-20—Публикация

1999-12-07—Подача