1134

Изобретение относится к автоматике и вычислительной технике, является усовершенствованием изобретения по авт.св. № 1257849 и может быть использовано в системах передачи информации.

Цель изобретения - расширение области применения путем преобразования двуполярного вхбдного сигнала в им- пульсно-кодомодулированный (ИКМ) сигнал.

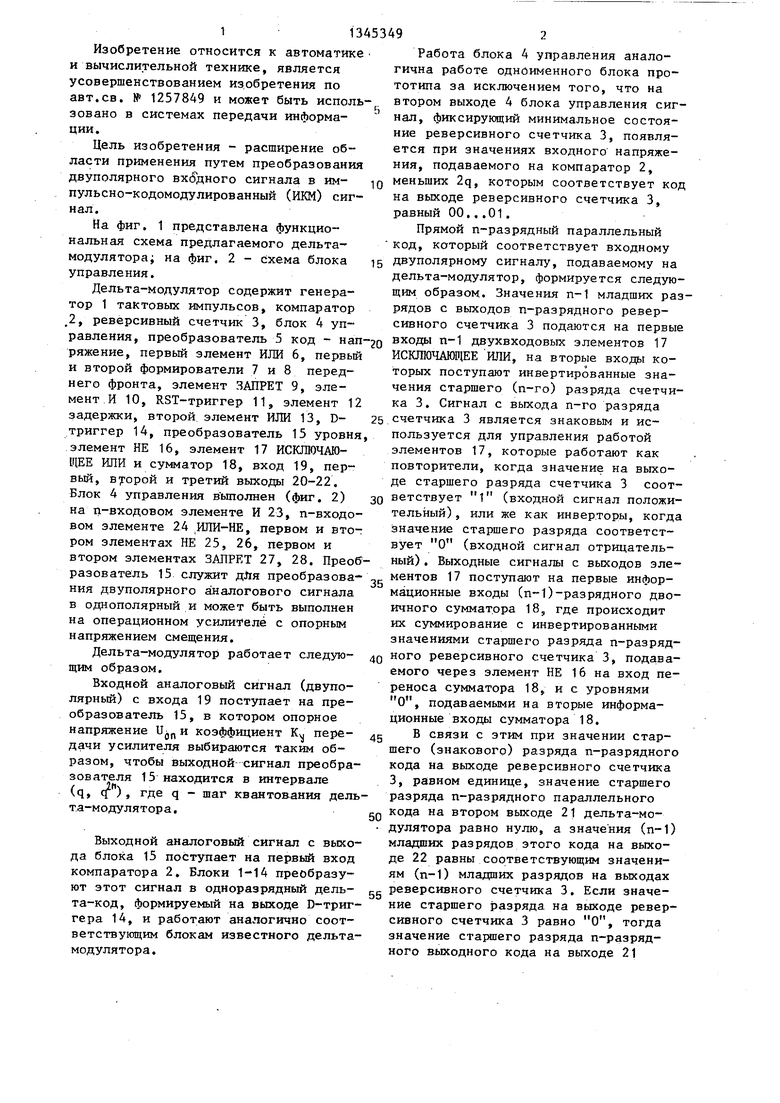

На фиг. 1 представлена функциональная схема предлагаемого дельта- модуля тор а на фиг, 2 - Схема блока управления.

Дельта-модулятор содержит генератор 1 тактовых импульсов, компаратор ,2, реверсивный счетчик 3, блок 4 управления, преобразователь 5 код - нап ряжение, первый элемент ИЛИ 6, первый и второй формирователи 7 и 8 переднего фронта, элемент ЗАПРЕТ 9, элемент И 10, RST-триггер 11, элемент 12 задержки, второй элемент ИЛИ 13, D- триггер 14, преобразователь 15 уровня элемент НЕ 16, элемент 17 ИСКЛЮЧАЮЩЕЕ ИЛИ и сумматор 18, вход 19, первый, второй и третий выходы 20-22. Блок 4 управления в ыполнен (фиг. 2) на п-входовом элементе И 23, п-входо- вом элементе 24 ,ИЛИ-НЕ, первом и втот ром элементах НЕ 25, 26, первом и втором элементах ЗАПРЕТ 27, 28. Преобразователь 15 служит для преобразования двуполярного аналогового сигнала в однополярный и может быть выполнен на операционном усилителе с опорным напряжением смещения.

Дельта-модулятор работает следующим образом.

Входной аналоговый сигнал (двупо- лярный) с входа 19 поступает на преобразователь 15, в котором опорное напряжение Uj и коэффициент Ку, пере

дачи усилителя выбираются таким образом, чтобы выходной сигнал преобразователя 15 находится в интервале q Т ) где q - шаг квантования дельта-модулятора.

Выходной аналоговый сигнал с выхода блока 15 поступает на первый вход компаратора 2. Блоки 1-14 преобразуют этот сигнал в одноразрядный дельта-код, формируемый на выходе D-триг гера 14, и работают аналогично соответствующим блокам известного дельта модулятора.

0

о Работа блока 4 управления аналогична работе одноименного блока прототипа за исключением того, что на втором выходе 4 блока управления сигнал, фиксирующий минимальное состояние реверсивного счетчика 3, появляется при значениях входного напряжения, подаваемого на компаратор 2, меньших 2q, которым соответствует код на выходе реверсивного счетчика 3, равный 00... 01.

Прямой п-разрядный параллельный код, который соответствует входному 5 двуполярному сигналу, подаваемому на дельта-модулятор, формируется следующим образом. Значения п-1 младших разрядов с выходов п-разрядного реверсивного счетчика 3 подаются на первые входы п-1 двухвходовых элементов 17 ИСКЛЮЧАЮЩЕЕ ИЛИ, на вторые входы которых поступают инвертированные значения старшего (п-го) разряда счетчика 3. Сигнал с выхода п-го разряда счетчика 3 является знаковым и используется для управления работой элементов 17, которые работают как повторители, когда значение на выходе старшего разряда счетчика 3 соответствует 1 (входной сигнал положительный) , или же как инверторы, когда значение старшего разряда соответствует О (входной сигнал отрицатель25

30

ный). Выходные сигналы с выходов элементов 17 поступают на первые информационные входы ()-разрядного двоичного сумматора 18, где происходит их суммирование с инвертированными значениями старшего разряда п-разряд- ного реверсивного счетчика 3, подаваемого через элемент НЕ 16 на вход переноса сумматора 18, и с уровнями О, подаваемыми на вторые информационные входы сумматора 18.

В связи с этим при значении старшего (знакового) разряда п-разрядного кода на выходе реверсивного счетчика 3, равном единице, значение старшего разряда п-разрядного параллельного кода на втором выходе 21 дельта-модулятора равно нулю, а значения (п-1) младших разрядов этого кода на выходе 22 равны соответствующим значениям (п-1) младших разрядов на выходах реверсивного счетчика 3. Если значение старшего разряда на выходе реверсивного счетчика 3 равно О, тогда значение старшего разряда п-разрядного выходного кода на выходе 21

дельта-модулятора равно единице, а значение (п-1) младших разрядов счетчика 3 инвертируется и к ним добавляется единица младшего разряда, что обеспечивает формирование прямого кода на третьих выходах 22 дельта-модулятора.

Таким образом, при подаче на вход дельта-модулятора двуполярного сиг- нала на первом выхода 20 дельта-модулятора формируется дельта-модулиро- ванный сигнал, а на выходах 21, 22 - п-разрядный параллельный ИКМ сигнал.

Формула изобретения

1. Дельта-модулятор по авт.св. № 1257849, отличающийся тем, что, с целью расширения области применения за счет преобразования двуполярного входного сигнала в им- пульсно-кодомодулированный сигнал, в дельта-модулятор введены сумматор, элементы ИСКЛЮЧАКЩЕЕ ИЛИ, элемент НЕ, источник логического нуля и преобразователь уровня между первым входом компаратора и входом дельта-модулятора, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и вход элемента НЕ подклю- чены к соответствуклцйм выходам реверсивного счетчика, начиная с младшего разряда, выход элемента НЕ подключен к входу переноса сумматора, вторым входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и является вторым выходом дельта-модулятора, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с первыми информацион

3494

ными входами сумматора, вторые информационные входы которого подключены к источнику логического нуля, выходы сумматора являются третьими выходами дельта-модулятора.

2. Лельта-модулятор по п. 1, отличающийся тем, что блок управления вьшолнен на элементах НЕ, п-разрядном элементе ИЛИ-НЕ, где п число разрядов входного кода, п-вхо

довом элементе И и элементах ЗАПРЕТ, выход первого элемента НЕ соединен с первым прямым входом первого элемен- та ЗАПРЕТ, первый прямой вход второго элемента ЗАПРЕТ объединен с входом первого элемента НЕ и является управляющим входом блока, вторые прямые входы элементов ЗАПРЕТ объединены и являются тактовым входом блока, выход п-входового элемента И подключен к инверсному входу первого элемента ЗАПРЕТ и является первым выходом блока, выход п-входового элемента ИЛИ- НЕ подключен к инверсному входу Второго элемента ЗАПРЕТ и является вторым выходом блока, выходы элементов ЗАПРЕТ являются соответственно третьим и четвертым выходами блока, 1-П-1 входы- п-входового элемента ИЛИ- НЕ и п-входового элемента И объединены и являются одноименными информационными входами блока, п-й вход п- входового элемента И непосредственно, а п-й вход п-входового элемента ИЛИ- НЕ через второй элемент НЕ подключены к п-му информационному входу блока.

Редактор С.Лисина

Составитель О.Ревинский

Техред и.Попович Корректор С,Черни

Заказ 4932/55Тираж 899 Подписное

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушскаянаб., д. 4/5 -----. „« -„« „ -«--

Производственно-полиграфическое предприятие, г. Ужгород, ул,Проектная, 4

фи5.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1990 |

|

SU1718383A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Дельта-модулятор | 1986 |

|

SU1388992A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Устройство аналого-цифрового преобразования для измерения параметров моноимпульсных сигналов | 1980 |

|

SU924849A1 |

| Дельта-модулятор | 1987 |

|

SU1448411A1 |

| Устройство для кодирования аналоговой информации | 1986 |

|

SU1338074A1 |

| Дельта-модулятор | 1989 |

|

SU1649666A1 |

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Коррелятор | 1986 |

|

SU1339584A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи информации. Цель изобретения - расширение области применения за счет преобразования двуполярного входного сигнала в импульсно-кодомодулирован- ный сигнал смещенного формата. Дельта-модулятор содержит генератор 1 тактовых импульсов, компаратор 2, реверсивный счетчик 3, блок 4 управления, преобразователь 5 код - напряжение, элементы ИЛИ 6, 13, формирова-. тели 7, 8 переднего фронта, элемент ЗАПРЕТ 9, элемент И 10, RST-триггер 11, D-триггер 14, элемент 12 задержки, преобразователь 15 уровня, элемент НЕ 16, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 17 и сумматор 18. 1 з. п. ф-лы, 2 ил. с (Л со 4 СЛ со N гг N) р/ Фиг.

| Дельта-модулятор | 1985 |

|

SU1257849A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-15—Публикация

1986-02-27—Подача