Изобретение относится к вычислительной технике и может быть использовано в системах обработки иэображе-; НИИ для решения задач распределения элементов изображения по диапазонам яркости.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения подсчета количества чисел массива по произвольному числу диапазонов произвольной длины.

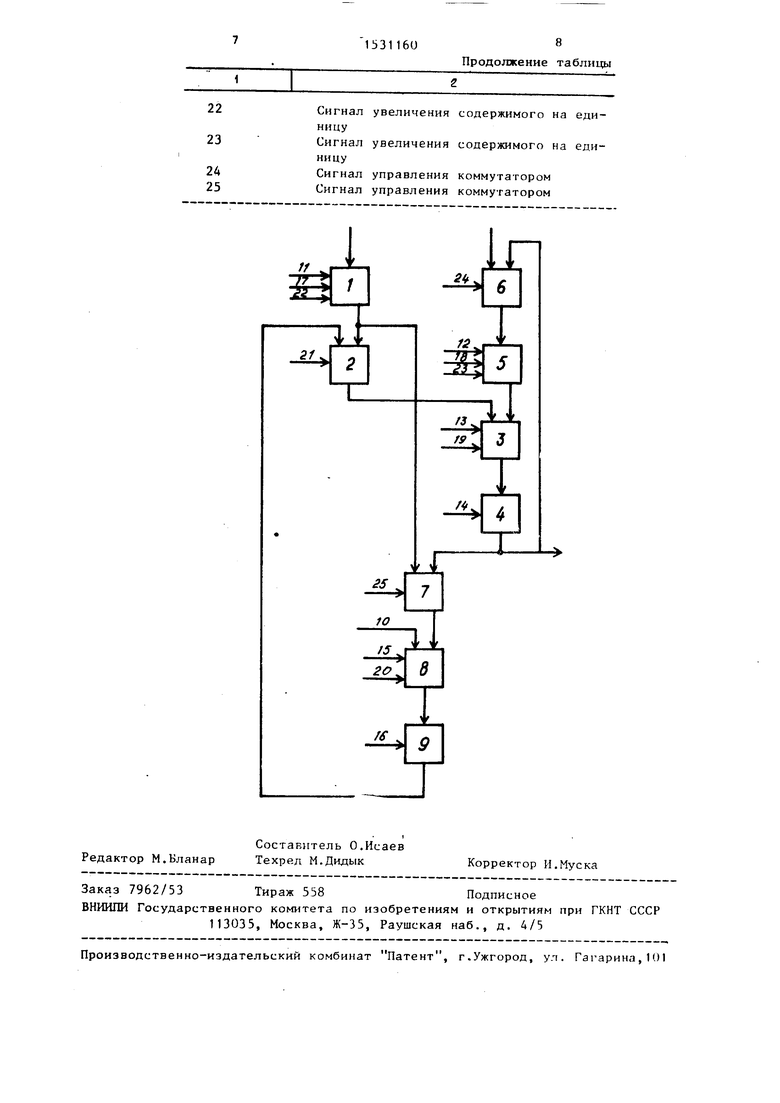

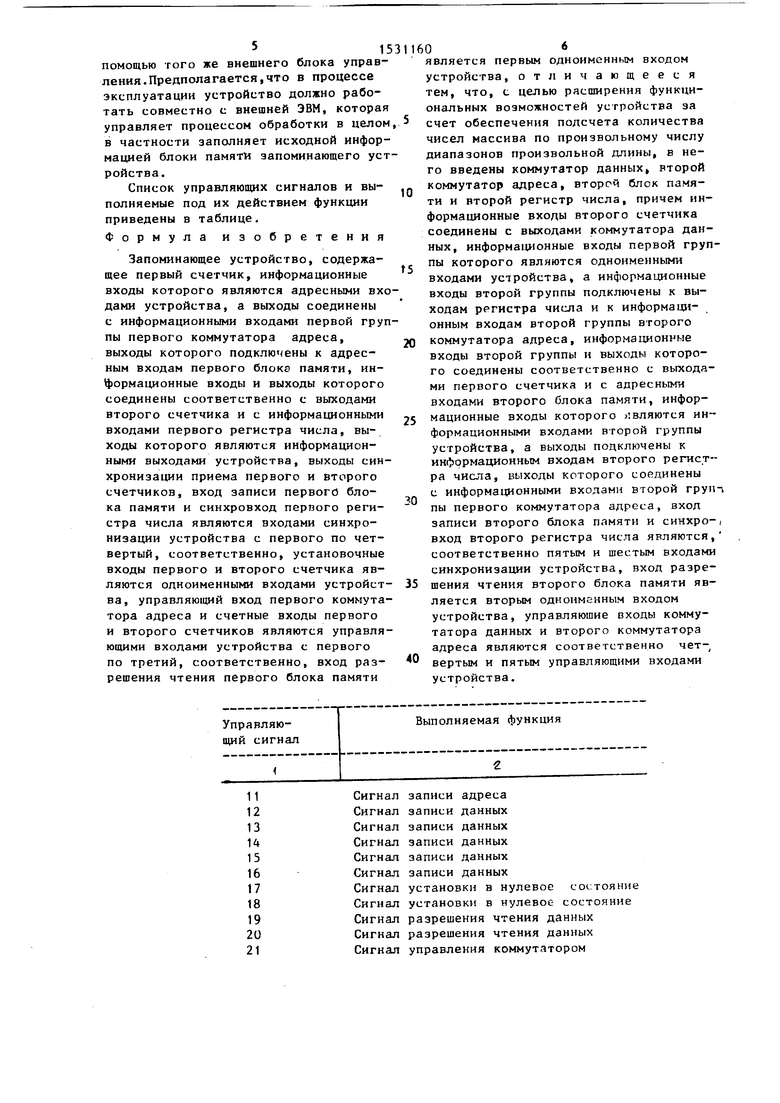

На чертеже приведена схема запоминающего устройства.

Устройство содержит первый счетчик 1, первый коммутатор 2 адреса, первый блок 3 памяти, первый регистр 4 числа, второй счетчик 5, коммутатор 6 данных, второй коммутатор 7 адреса, (Второй блок 8 памяти и второй регистр

9 числа.

На схеме также обозначены входы 11-16 синхронизации, установочные входы 17 и 18, входы 19 и 20 разрешения чтения и управляющие входы 21-25 устройства.

Работа устройства в режиме полсчета чисел основана на функциональчоЛ

О)

зависимости между величиной числа и номером ячейки, соответствующей данно му диапазону значений числа. Функциональная зависимость задается предвари тельной загрузкой второго блока 8 памяти. В первом блоке 3 памяти хранится обрабатываемый массив чисел, максимальное из которых может иметь значение 2-1, где ,2,...,n (разряд- ность блока 3), При этом обработка может вестись по m диапазонам, где m

К

1,2,3,...,2 . Максимально возможное значение числа- из всего множества чисел обрабатываемого массива опреде ляет емкость второго блока 8 памяти, а разрядность блока 8 определяется как

Р log2ra

где j ... - операция округления до це лого числа в большую сторону.

В ячейки блока 3 памяти с нулевой 1ПО (т-1 )-ю включительно,вьщеленные для подсчета чисел, распределяемых по диапазонам, должны быть записаны нули Обрабатываемый массив чисел должен храниться в последующих ячейках блока 3 памяти, начальный адрес записываетс в счетчик 1.

В ячейки блока 3 памяти с адресами, равными значениям чисел исходного массива, входящими в заданный диапазон, записывается константа, равная номеру ячейки блока 3 памяти, которая соответствует данному диапазону значений числа. На этом подготовка устройства к работе заканчивается, после чего оно готово к обработке массива чисел, хранящихся в первом блоке 3 па- мяти.

Коммутатор 2 адреса настраивается на передачу адреса с выхода счетчика 1 на адресный вход блока 3 памяти и производится считывание числа, храня- щегося в ячейке блока 3 памяти с данным адресом.

Считанное число через регистр 4 числа и коммутатор 7 адреса, настроенный на передачу информации с выхода регистра числа 4, поступает на адресный вход блока У памяти и по данному адресу производится считывание кода, который записывается в регистр 9 числа. Этот код является ад ресом ячейки соответствующего диапазона в блоке 3 памяти и через коммутатор 2 адреса поступает на его ад--сtO-15 ,

-ро 25 . я 30

..,

- 45 35

50

55

ресный вход. Производится считывание в регистр 4 числа кода, представляющего собой текущее значение количества анализируемых чисел, попадающих в данный диапазон. Код с выхода регистра 4 числа через коммутатор 6 данных записывается в счетчик 5, где производится увеличение его на единицу. Увеличенный на единицу код из счетчика 5 записывается обратно в блок 3 памяти по тому же адресу. Содержимое счетчика 1 увеличивается на единицу, и производится обработка следующего числа из исходного массива, хранящегося в блоке 3 памяти. Эта последовательность действий повторяется для каждого исходного числа и, таким образом, производится подсчет количества чисел исходного массива по диапазонам их значений.

Устройство может работать и в режиме обычного ЗУ. Лля этого коммутаторы 2 и 7 адреса переключаются в режим передачи информации с выхода счетчика 1 на адресные входы блоков 3 и 8 памяти соответственно. При этом устройство представляет собой два отдельных ЗУ с общим счетчиком адреса, информация из которых считывается в регистры 4 и 9 чиста.

Кроме того, устройство может работать и п р .яшо ЗУ с таблицей коснен- ной адресации на выходе. При этом первый блок J представляет собой основную память для хранения информации, которая при считывании через регистр 4 числа и коммутатор 7 адреса поступает на адресный вход второго блока 8 памяти, представляющего собой вспомогательную память, выполняющую функции хранения таблицы косвенной адресации, и является адресом, по которому из блока 8 памяти в регистр 9 числа считывается результат. Таким образом, устройство осуществляет хранение и табличное преобразование информации.

Упра.вление предлагаемым устройством в описанном порядке может осуществлять как автомат с жесткой логикой, так и универсальная ЭВМ по заданной программе.

Сигналы управления поступают от внещнего блока управления ко всем блокам запоминающего устройства. Результат или выходные данные могут быть считаны, согласно алгоритма обработки, из первого блока 3 памяти с

помощью того же внешнего блока управления. Предполагается, что в процессе эксплуатации устройство должно работать совместно с внешней ЭВМ, которая управляет процессом обработки в целом в частности заполняет исходной информацией блоки памяти запоминающего устройства.

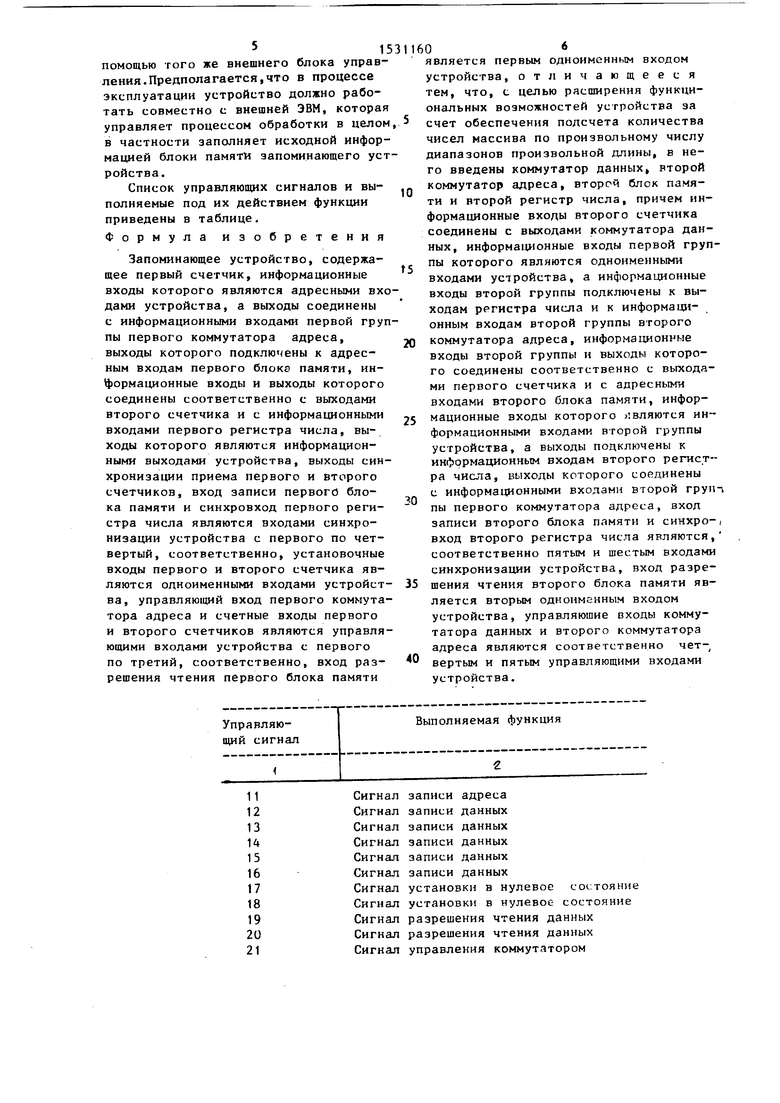

Список управляющих сигналов и выполняемые под их действием функции приведены в таблице.

Формула изобретения

Запоминающее устройство, содержащее первый счетчик, информационные входы которого являются адресными входами устройства, а выходы соединены с информационными входами первой группы первого коммутатора адреса, выходы которого подключены к адресным входам первого блоке памяти, информационные входы и выходы которого соединены соответственно с выходами второго счетчика и с информационными входами первого регистра числа, выходы которого являются информационными выходами устройства, выходы синхронизации приема первого и второго счетчиков, вход записи первого блока памяти и синхровход первого регистра числа являются входами синхронизации устройства с первого по четвертый, соответственно, установочные входы первого и второго счетчика являются одноименными входами устройства, управляющий вход первого коммутатора адреса и счетные входы первого и второго счетчиков являются управляющими входами устройства с первого по третий, соответственно, вход разрешения чтения первого блока памяти

является первь1м одноименным входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения подсчета количества чисел массива по произвольному числу диапазонов произвольной длины, в него введены коммутатор данных, второй коммутатор адреса, второй блок памяти и второй регистр числа, причем информационные входы второго счетчика соединены с выходами коммутатора данных, информационные входы первой группы которого являются одноименными входами устройства, а информационные входы второй группы подключены к выходам регистра чи(::ла и к информационным входам второй группы второго коммутатора адреса, информационные входы второй группы и выходы которого соединены соответственно с выходами первого счетчика и с адресными входами второго блока памяти, информационные входы которого являются ИН формационными входами второй группы устройства, а выходы подключены к информационным входам второго регистра числа, выходы которого соединены с информационными входами второй грут пы первого коммутатора адреса, вход записи второго блока памяти и синхро-, вход второго регистра числа являются, соответственно пятым и шестым входами синхронизации устройства, вход разрешения чтения второго блока памяти является вторым одноименным входом устройства, управляющие входы коммутатора данных и второго коммутатора адреса являются соответственно чет- вертым и пятым управляющими входами устройства.

Сигнал увеличения содержимого на единицу

Сигнал увеличения содержимого на единицу

Сигнал управления коммутатором Сигнал управления коммутатором

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1339653A1 |

| Запоминающее устройство | 1981 |

|

SU970463A1 |

| Запоминающее устройство с коррекцией программы | 1986 |

|

SU1347097A1 |

| Устройство подсчета кодов | 1987 |

|

SU1534457A1 |

| Запоминающее устройство | 1980 |

|

SU942141A2 |

| Буферное запоминающее устройство | 1987 |

|

SU1479954A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Устройство для сортировки чисел | 1985 |

|

SU1304015A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обработки изображений для решения задач распределения элементов изображения по диапазонам яркости. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения подсчета количества чисел массива по произвольному числу диапазонов произвольной длины. Устройство содержит первый и второй блоки памяти, первый и второй коммутаторы адреса, коммутатор данных, первый и второй счетчики, первый и второй регистры числа. Цель изобретения достигается разделением первого блока памяти на две части для хранения обрабатываемого массива чисел и текущих кодов количества чисел по каждому диапазону, а также предварительным распределением всех возможных длин чисел массива по требуемым диапазонам путем кодировки второго блока памяти таким образом, что по коду каждого числа массива в первом блоке памяти выбирается ячейка во втором блоке памяти, содержащая код диапазона для этого числа. 1 ил., 1 табл.

//

2/

1л

21

IS,

/j,

/9

Li

15

ттвтя ялл

2О.

I

| Запоминающее устройство | 1977 |

|

SU691925A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство | 1981 |

|

SU970463A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-12-23—Публикация

1987-06-08—Подача