(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287238A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

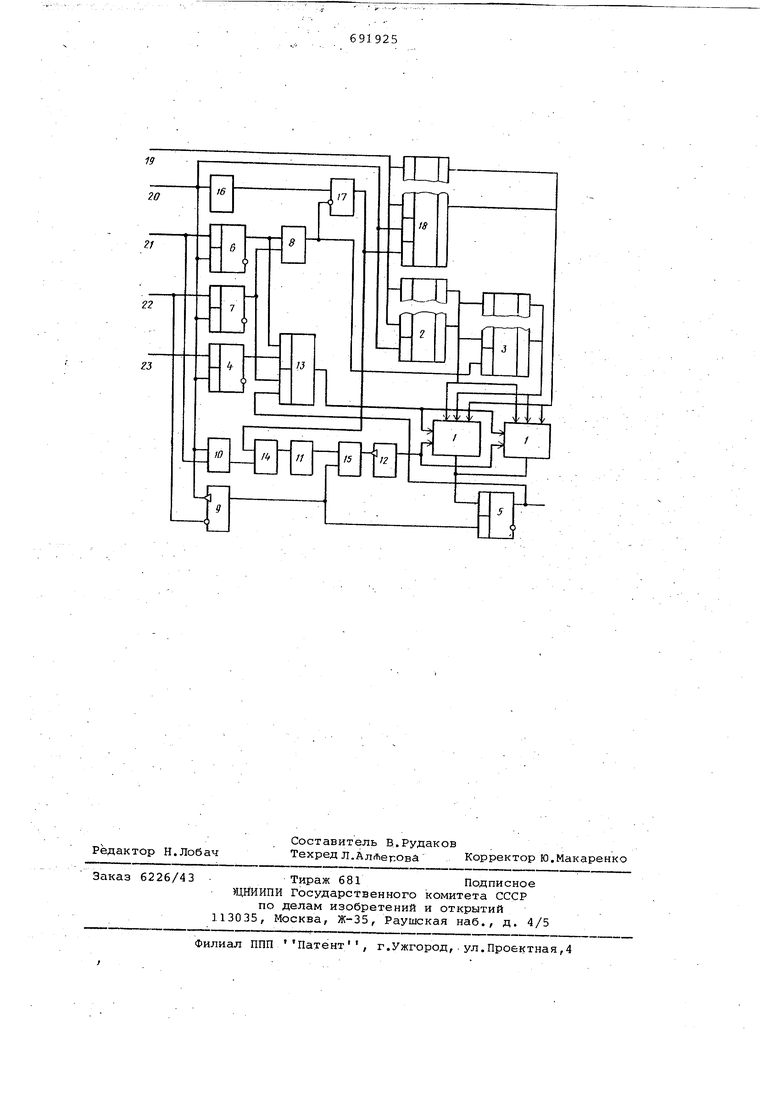

Изобретение относится к области aanoNMHaioiuHx устройств и может быть использовано в аппаратуре передачи данных устройствах автоматики и вычислительной техники с синхронной пр извольно-последовательной выборкой, где количество обращений в одной серии последовательных выборок или рас стояние межлу началами двух серий больше 32 или 64 (ограничение накладывается числом циклов регенерации, необходимых для восстановления инфор мации в полупроводниковых динамических запоминающих узлах). Одно из известных запоминающих устройств содержит полупроводниковые динамические запоминанациё узлы, регистр адреса, дешифраторы, регистры числа, триггер записи-считывания, формирователь строба считывания, формирователь задержки сигнала записи, формирователь сигнала записи, счетчик адресов регистрации, мультиплексор адресных сигналов, кольцевой генератор импульсов, формирователи сигналов обращения и регенерации {1 . Это запоминающее устройство предназначено для асинхронных систем, в которых обращение к памяти прекращается при проведении в ней регенерации-информации. Применение его в синхронных системах, в.которых длительность обращения жестко задана и само обращение происходит в фиксированные моменты времени, требует увеличения вдвое длительности цикла обращения, что в большинстве случаев является неприемлемым. Из -известных запоминающих устройств наиболее близким техническим решением к данному изобретению является запоминающее устройство, содержащее полупроводниковые динамические блоки памяти, входы разрешения выборки и адресные входы которых подключены к выходам регистра адреса, входи которого соединены с одними из входных шин адреса, входной регистр числа, выходной регистр числа, входы которого подключены к выходам блоков памяти, первый элемент ИЛИ, входы которого соединены с выходами триггеров записи и считывания, а выход - с управляюищм входом дешифратора, формирова:тель сигнала считывания, входы которого подключены к входной шине считывания и шине тактового сигнала соответственно, а выход - к управляющему входу выходного регистра числа, первый элемент И,один из входов которого соединен с входной шиной записи, другой вход - с шиной тактового сигнала, формирователь задержки сигнала записи, формг-фователь сигнала записи, выход которого соеди нен с входом записи блоков памяти. Кроме того это устройство содержит формирователь команды регенерации, мультиплексор адресов, счетчик регенерации, инвертор младшего разряда адреса.2. Это запоминающее устройство, не требуя дополнительного времени на регенерацию при произвольно-последовательной выборке, содержит большое количество оборудования в схемах управления, Целью настоящего изобретения является упрощение устройства без снижения быстродействия. Указанная цель достигается тем, что запоминающее устройство содержит элемент .2И-ИЛИ, второй элемент И, второй и третий элементы ИЛИ, формирователь задержки тактового сигнала и счетчик, причем входы элемента 2И-ИЛИ подключены соответственно к выходам входного и выходного рёгистров числа и триггеров записи и считывания, а выход - к информационным входам блоков памяти, прямой вход второго элемента И соединен с выходом формирователя задержки тактового сигнала, инверсный вход - с выходом первого элемента ИЛИ, а выход - с суммирующим входом счетчика и одним из, входов второго элемента ИЛИ, дру гой вход которого соединен с выходо первого элемента И, а выход второго элемента ИЛИ соединен со входом формирователя задержки сигнала, выход которого подключен к одномуиз вхо дов третьего элемента ИЛИ, другой . вход третьего элемента ИЛИ соединен с выходом формирователя сигнала счи тывания, а выход - с входом формирователя записи, выходы-счетчика сОед нены с входами адресов регенераций - обращения блоков, памяти, информацио ные входы счетчика подключены к дру гим входным шинам адреса, а управля щий вход - к шине TaktbBoro сигнала На че зтеже изображена схема запо минающего устройства, использующего в качестве запоминающих блоков дина мические микросхемы памяти 1024x1 би Запоминающее устройство сЬдёржит полупроводниковые динамические блок памяти 1, регистр 2 адреса, дешифра тор 3, входной регистр 4 числа, вых ной регистр 5 числа, триггер записи 6, триггер считывания 7, первый эле мент ИЛИ 8, формирователь 9 сигнала считывания, первый элемент И 10, .формирователь 11 задержки сигнала аписи, формирователь 12 сигнала заиси, элемент 2И-ИЛИ 13, второй элеент ИЛИ 14, третий элемент ИЛИ 15, ормирователь 16 задержки тактового игнала, второй.элемент И 17, счетчик 18, входные шины 19 адреса, шину 20 актового сигнала, шины 21 записи и 22 считывания, входные шины 23 данных . Входы элемента 2И-ИЛИ 13 подключены соответственно к выходам регистров 4 и 5, и триггеров 6 и 7, а выход - к информационным входам блоков памяти 1. ., . Прямой вход элемента И 17 соединен с выходом формирователя 16, инверсный вход - с выходом элемента ИЛИ 8, а выход - с суммирующим входом счетчика 18 и одним из входов элемента ИЛИ 14, другой вход которого соединен с выходом элемента И 10. Выход элемента ИЛИ 14 соединен со . входом формирователя 11, выход которого подключен к одному из входов элемента ИЛИ 15, другой вход элемента ИЛИ 15 соединен с выходом формирователя 9, а выход - с входом формирователя .12. Входы регистра 2 соединены с одними из входных шин 19 адреса, другие шины 19 подключены . к информационным входам счетчика 18. Выходы сче.тчика 18 соединены с входами адресов регенерации-обращения блоков.памяти 1, а управляющий вход - к шине 20 тактового сигнала.- - . . Запоминакядее устройство работает следующим образом. ; . .: , ... . . . В цикле записи по шинам 23 постуг пает код з.аписываемого числа, по; шинам 19 - код адреса записываемого числа, по шине 21 - команда записи положительной полярности. Тактовый сигнал положительной полЖрности записывает код Числа в регистр 4, младшие разряды адреса - в счетчик 18, старшие разряды адреса.- в регистр 2адреса, команду запись - ,в триггер 6. Триггер б разрешает прохождение кода записываемого числа с регистра 4 через элемент. 2И-ИЛИ 13 на памяти 1. Триггер 7 запрещает про- . ховдение информации с регистра 5 через элемент 2И-ЙЛИ 13. Элемент ИЛИ 8 разрешает выбор блока 1 дешифратором 3и запрещает прохождение тактового сигнала через элемент И 17 на счетчик 18. Сигнал записи на шине 21 разрешает прохождениетактового сигналачерез элемент И 10 на формирователь 11. Задержанный формирователем 11 . сигнал запускает формирователь 12, который формирует записи требуемой амплитуды, длительности иполярности и подает его в блоки 1. В цикле записи происходит генерация информации в блоках 1 по адресу, определяемому кодом младших разрядов адреса. / . В цикле считывания по шинам 19 подается адрес считываемого числа, по шине 22 - команда считывания положительной полярности. Тактовый сиг нал записывает код адреса в счетчик 18 и регистр 2 адреса, команду считы вания - в триггер 7. Триггер 7 разре шает прохождение кода числа из регис ра 5 через элемент 2И-ИЛИ 13. Тригге 6 запрещает прохождение содержимого регистра 4 через элемент 2И-ИЛИ 13. Элемент ИЛИ 8 разрешает выбор дешифратором 3 блока 1 и запрещает прохож дение тактового сигнала через элемен И 17 на счетчик 18. Сигнал считывани на шине 22 разрешает формирование сй нала считывания формирователем 9. Сигнал считывания с выхода форми)Ова теля 9 поступает на управт1яю1йий вход регистра 5, записывая в него информа цию с выхода блоков 1. Этот же сигнал через элемент ИЛИ 15 запускает задним фронтом формирователь 12. Считанное число/ находящееся в регистре 5, через элемент 2И-ИЛИ 13 записывается в блоки 1, пр этом происходит регистрацияинформации в них.. - :-,. . При отсутствии записи и считывани на Соответствующих входных шинах 21 и 22 элемент ИЛИ 8 запрещает набор дешифратором 3 блока 1 и разрешает прохождение тактового сигнала через элемент И 17 на счетчик 18. Тактовый сигнал на выходе элемента И 17 прибавляет 1 к содержимому счетчика 18 и, пройдя через элемент ИЛИ 14, запускает формирователи 11 и 12. Про .изводится регенерация информации в блоках 1. При этом не требуется дополнительного времени на рёгенераи;ию по адресу, находящемуся в счетчике 18 При произвольно-последовательной выборке, т.е. когда серия обращений начинается с произвольного адреса, а адреса обращений в серии последовательно увеличиваются на , вОзможны следующие случаи: при числе обращений в серии не Менее 32 происходит обращение ко всем адресам, регенерации блоков 1 с регенерацией информации ,в них; при расстоянии Между началами двух серий не МёНеё: 32 обращений и. количестве обратдений в серии, менее 32 формирователь. 1б, элементы ИЛИ 8, И 17, счетчик 18 и форми рователи 11 и 12 производят регенерацию информации в неопрошенных при обращении адресах блоков памяти 1; при отсутствии обращений регенерация информации производится блоками 16,8, 17,18,14,11,15 и 12. в предлсокенном изобретении пример но в два раза сокращается количество оборудования в схемах управления по сравнению с прототипом. При этом не требуется дополнительного времени на регенерацию..

691925 Формула изобретения Запоминающее устройство, содержащее полупроводниковые динамические блоки памяти, входы разрешениявыборки и адресные входы которых подключены к выходам регистра адреса,;входы которого соединены с одними из входных шин адреса, входной регистр числа, выходной регистр числа.- входы которого подключены к выходам блоков памяти, первый элемент ИЛИ, входы которого соединены с выходами триггеipa записи и считывания, а выход - с управляющим входом дешифратора, формирователь сигнала считывания, входы которого подключены к входной шине считывания и шине тактового сигнала соответственно, а выход - к управляющему входу Ъых6дноГо регистра числа, первый элемент И, один из входов которого соединен с входной шиной записи, другой вход - с шиной тактового сигнала, формирователь задержки сигнала записи, формирователь сигнала записи, вайод которого соединен с входом записи блоков памяти, о -т личающееся тем, что, с целью упрощения устройства, оно содержит элемент 2И-ИЛЙ, второй элемент И, второй и третий элементы ИЛИ, формирователь задержки тактового сигнала и счетчик, причем входы элемента 2И-ИЛИ Подключены соответственно к выходам входного и выходногорегистров числа и триггеров записи и считывания, а выход - к информационным входам блоков памят.и, прямой вход второго элемента И соединен с выход.ом формирователя задержки тактового сигнала, инверсный вход - .с. ВЕагходом первого элемента ИЛИ, а выход - с суммирующим входом с 1етчика.; и одним из входов второго элемента.ИлИ, другойвход которо.го соединен с выходом первого элемента И, авыхОд второго элемента ИЛИ соединен со входом формирователя задержки сигнала, выход которого подключен к одному из входов третьего элемента ИЛИ, другой вход, третьего элемента ИЛИ соединен с выходом формирователя Сигнала сч1 тывания, а выход - с входом формирователя записи, выходы счетчика соединены с входами адресов регенерации-ббращения блоков амяти, информационные входы счетчика одключены к другим входным шинам дреса, а управляющийвхОд - к шине актового сигнала. Источники информации, принятые во внимание при экспертизе 1. Патент США W 3790961, п. 340-173, 1974. 2. Патент США, 3846765, л.340-173, 1974.

Авторы

Даты

1979-10-15—Публикация

1977-06-15—Подача