13

Изобретение относи7 ся к вычислительной технике и может быть использовано при построении запоминающих устройств большой емкости.

Цель изобретения - повышение быстродействия при отсутствии статического потребления от высоковольтного источника напряжения, и повьшение надежности формирователя.

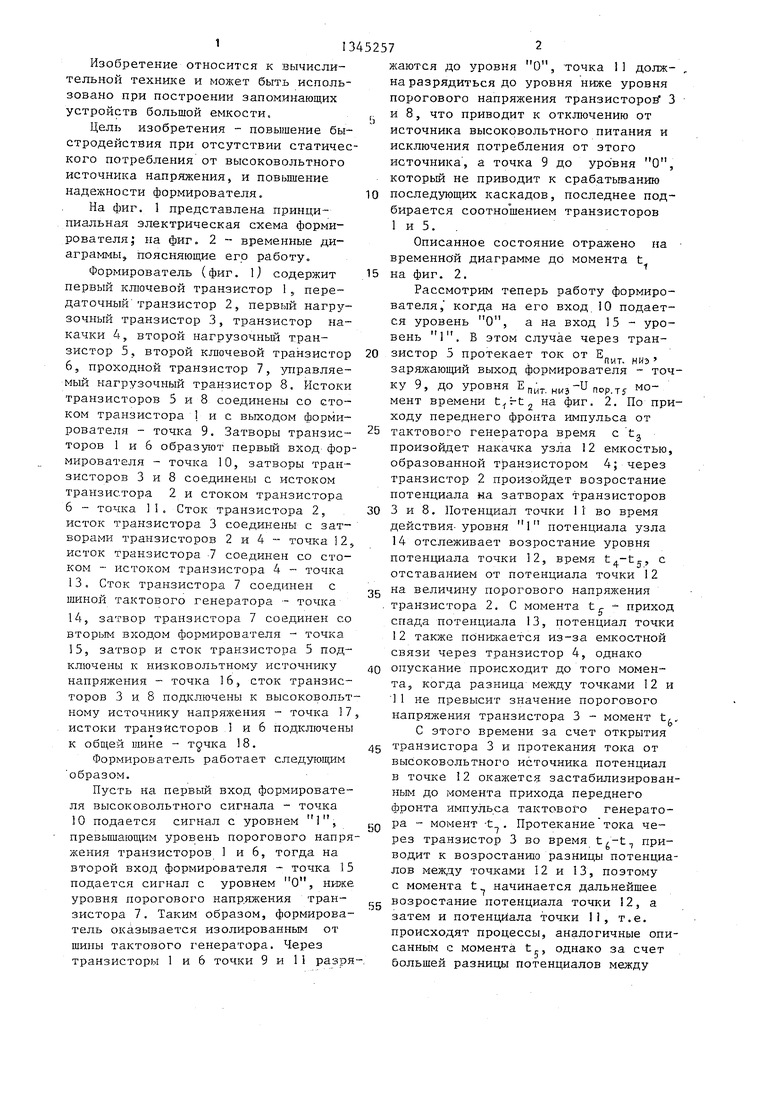

На фиг, 1 представлена принципиальная электрическая схема формирователя j на фиг 2 - временные диаграммы, поясняющие его работу

Формирователь (фиг. ) содержит первый ключевой транзистор 1 ., передаточный транзистор 2, первый нагрузочный транзистор 3, транзистор накачки 4, второй нагрузочный транзистор 5, второй ключевой транзистор 6, проходной транзистор 7, управляемый нагрузочный транзистор 8. Истоки транзисторов 5 и 8 соединены со стоком транзистора 1 и с выходом формирователя - точка 9. Затворы транзисторов 1 и 6 образуют первый вход формирователя - точка 10, затворы транзисторов 3 и 8 соединены с истоком транзистора 2 и стоком транзистора 6 - точка 11. Сток транзистора 2, исток транзистора 3 соединены с затворами транзисторов 2 и 4 - точка 12, исток транзистора 7 соединен со стоком - истоком транзистора 4 - точка

13,Сток транзистора 7 соединен с шиной тактового генератора - точка

14,затвор транзистора 7 соединен со вторым входом формирователя - точка

15,затвор и сток транзистора 5 подключены к низковольтному источнику напряжения - точка 16, сток транзисторов 3 и 8 подключены к высоковольтному источнику напряжения - точка 17 истоки транзисторов 1 и 6 подключены к общей шине - 18.

Формирователь работает следующим образом.

Пусть на первый вход формирователя высоковольтного сигнала - точка 10 подается сигнал с уровнем 1 , превышаюЕЩМ уровень порогового напряжения транзисторов 1 и 6, тогда на второй вход формирователя - точка 15 подается сигнал с уровнем О, ниже уровня порогового напряжения транзистора 7. Таким образом, формирователь оказывается изолированным от шины тактового генератора. Через транзисторы 1 и 6 точки 9 и 11 разря

0

5

0

25

257

.

30

35

40

1

45

50

55

2

жаются до уровня О, точка 11 долж- , на разрядиться до уровня ниже уровня порогового напряжения транзисторов 3 и 8, что приводит к отключению от источника высоковольтного питания и исключения потребления от этого источника, а точка 9 до уровня О, который не приводит к срабатьгоанию последующих каскадов, последнее подбирается соотношением транзисторов 1 и 5. .

Описанное состояние отражено на временной диаграмме до момента t, на фиг. 2.

Рассмотрим теперь работу формирователя, когда на его вход.10 подается уровень О, а на вход 15 - уровень 1. В этом случае через транзистор 5 протекает ток от Е , заряжающий выход формирователя - точку 9, до уровня nm..Tf момент времени на фиг. 2. По приходу переднего фронта импульса от тактового генератора время с tg произойдет накачка узла 12 емкостью, образованной транзистором 4; через транзистор 2 произойдет возростание потенциала на затворах транзисторов 3 и 8. Потенциал точки 11 во время действия-уровня 1 потенциала узла 14 отслеживает возростание уровня потенциала точки 12, время , с отставанием от потенциала точки 12 на величину порогового напряжения транзистора 2. С момента tg. - приход спада потенциала 13, потенциал точки 12 также понизкается из-за емкостной связи через транзистор 4, однако опускание происходит до того момента, когда разница между точками 12 и 1 1 не превысит значение порогового напряжения транзистора 3 - момент t.

С этого времени за счет открытия транзистора 3 и протекания тока от высоковольтного источника потенциал в точке 12 окажется застабилизирован- ным до момента прихода переднего фронта импульса тактового генератора - момент -t . Протекание тока через транзистор 3 во время приводит к возростанию разницы потенциалов меж,а,у точками 12 и 13, поэтому с момента t начинается дальнейшее возростание потенциала точки 2, а затем и потенциала точки 11, т.е. происходят процессы, аналогичные описанным с момента tj, однако за счет большей разницы потенциалов между

точками 12 и 13 процессы будут происходить каждый раз при более в гсоком уровне исходных потенциалов точек I2 и 11, а следовательно, и будут приводить к возростанию потенциалов этих точек.

Пусть в момент t произойдет переключение уровней сигналов 10 и 15. Теперь транзистор 7 закрыт, а тран- зисторы 6 и 1 открыты. Закрытие транзистора 7 приведет к прекращению емкостной накачки транзистором 4, а открытие транзисторов 1 и 6 к обнулению точек 9 и 11, потенциал точки 12 будет превышать потенциал точки 11 на величину порогового напряжения транзистора 2. При достаточно длительном сохранении на входах 10 и 15 состояния с момента tg (милисекунды и более) произойдет за счет токов утечки р-п переходов полный разряд (до нулевого уровня) точки 12,

Установим некторые простейшие

зависимости. Пусть в исходном положе- 25 нам размеров, которые не вносят оп- нии до начала переднего фронта импульса точки 13 потенциал в точке 12 был равен V, пусть амплитуда импульределяющий вклад в снижение процента выхода годных.

Происходит возростание надежности работы формирователя и расширение 30 сфер его применения поскольку обнуле ние выхода точки 9 теперь не приво- дит к изменению состояния потенциалов остальных точек, то формирователь работоспособен при любых операциях с точкой 9, не служит источником отрицательных выбросов и позволяет подключить к точке 9 как выходы, так и входы других устройств

са точки 13 составляет V, пороговое напряжение всех транзисторов Vnop , тогда во время действия уровня 1 импульса точки 13 в точке 11 устанавливается потенциал равный ,

который.стабилизирует потенциал точ-- ки 12 на уровне , Откуда gg следует, что возростание потенциалов (как и в известном устройстве) будет происходить до тех пор, пока -2V 70; необходимо /читьшать, что в процессе возростания потенциалов точек 11 и 12 происходит также возростание порогового напряжения транзисторов через коэффициент влияния подложки. В целом для-МОП технологии и 5-ти вольтовых импульсов шин тактового генератора удается обеспечить возростание потенциалов на выходе . до уровня 21-23 В, чт-о соответствует требованиям к уровню программирующего напряжения ячеек памяти FLOTOX и МНОЙ.

Рассмотрим отличительные особенности, связанные с разделением выхода формирователя - точка 9 от внутренних цепей накачки.

Подключение выхода к точке 9 позволяет рассчитывать работу формирователя - частоту тактового генератора, размеры транзисторов 7, 4,3,2,6 без

30

45

40

50

55

точного учета величины емкостной нагрузки, подключенной к точке 9.

Поскольку емкостная нагрузка теперь подключена непосредственно,а через транзистор 8, быстродействие

CL

возростает, примерно, в

г -Tg

где

Чвеличина емкостной нагрузки в точ- С

j-g - емкость затвора транзис- Переключение емкостной наке 9; тора {

грузки позволяет также-повысить тактовую частоту генератора, что приводит к росту быстродействия.

Поскольку произошло существенное уменьшение величины емкостной нагрузки, подклт)ченной к точке 1 1 , а также теперь необходимо обеспечивать полный предразряд только точек 12 и 11, но не обязательно точки 9, во время действия уровня 1 импульса точки 13, то это дает возможность уменьшить размеры транзисторов 4, 3,2, что позволяет перейти к тем величинам размеров, которые не вносят оп-

ределяющий вклад в снижение процента выхода годных.

Происходит возростание надежности работы формирователя и расширение сфер его применения поскольку обнуление выхода точки 9 теперь не приво- , дит к изменению состояния потенциалов остальных точек, то формирователь работоспособен при любых операциях с точкой 9, не служит источником отрицательных выбросов и позволяет подключить к точке 9 как выходы, так и входы других устройств.

gg

40 Формула изо.бретения

Формирователь сигналов записи, содержащий ключевой транзистор, передаточный транзистор, нагрузочный транзистор и транзистор накачки, причем затвор ключевого транзистора подключен к затвору нагрузочного транзистора, сток и затвор передаточного транзистора подключены к затвору транзистора накачки и к истоку нагрузочного транзистора, сток нагрузочного транзистора подключен к высоковольтному источнику, исток и сток транзистора накачки соединены, отличающийся тем, что, с целью повышения быстродействия и надежности формирователя, в него введены второй нагрузочный транзистор, второй ключевой транзистор.

проходной транзистор, управляемый нагрузочный транзистор, причем сток и затвор второго нагрузочного транзистора подключены к шине низковольт-- ного источника питания формирователя, исток второго нагрузочного транзистора подключен к стоку ключевого транзистора, истоку управляемого нагрузочного транзистора и является выходом формирователя, затвор второго ключевого транзистора является прямьЕ«1 информационным входом, форми- рователя, исток этого транзистора подключен к общей шине формирователя, сток второго ключевого транзистора

подключен к затвору управляемого нагрузочного транзистора и к точке соединения затвора нагрузочного транзистора и истока передаточного транзистора, сток проходного транзистора подключен к тактовой шине формирователя,, исток проходного транзистора подключен к истоку-стоку транзистора накачки, затвор проходного транзистора является инверсным информационным входом формирователя, сток управляемого нагрузочного транзистора подключен к шине высоковольтного источника питания формирователя.

ti tz iy

фие.г

te tg

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Ячейка памяти на МДП транзисторах | 1981 |

|

SU968854A1 |

| Формирователь импульсов на мдп-транзисторах | 1974 |

|

SU503353A1 |

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Формирователь импульсов записи | 1985 |

|

SU1297114A1 |

| Симметричный мультивибратор на моп-транзисторах | 1974 |

|

SU500577A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств большой емкости. Целью изобретения является повышение быс-т- родействия при отсутствии статического потребления от высоковольтного источника напряжения и повьшение надежности формирователя. Формирователь содержит ключевые транзисторы 1,6, передаточный транзистор 2, нагрузочные транзисторы 3,5, транзистор 4 накачки, проходной транзистор 7, управляемый нагрузочный транзистор 8. 2 ил. со NU ел to р фие.1

Составитель В, Гордонова Редактор И, Сегляник Техред А.Кравчук Корректор И.Муска

Заказ 4926/50 Тираж 587Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035,, Москва, Ж-35, Раушская наб. , д. 4/5

.Производственно-полиграфическое предприятие, г., Ужгород, ул. Проектная 4

| Способ автоматической сварки под слоем флюса | 1946 |

|

SU68892A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| IEEE Journal of Solid-state circuits, vol | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| ЯКОРЬ ДЛЯ МАШИНЫ ВЫСОКОЙ ЧАСТОТЫ | 1922 |

|

SU535A1 |

Авторы

Даты

1987-10-15—Публикация

1986-03-07—Подача