Изобретение относится к импульсно технике и может быть использовано в вычислительной технике, системах автоматического управления -и системах передачи информации.

Целью изобретения является расширение функциональных возможностей за счет обеспечения регулирования периода формируемой псевдослучайной последовательности.

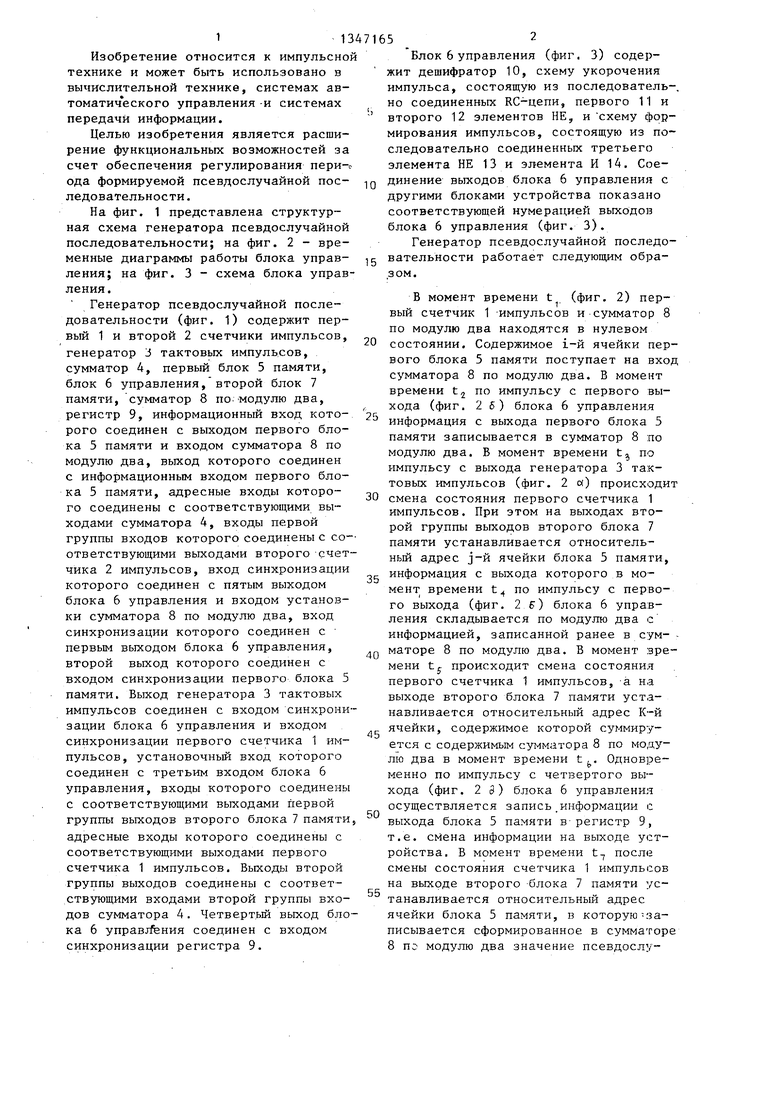

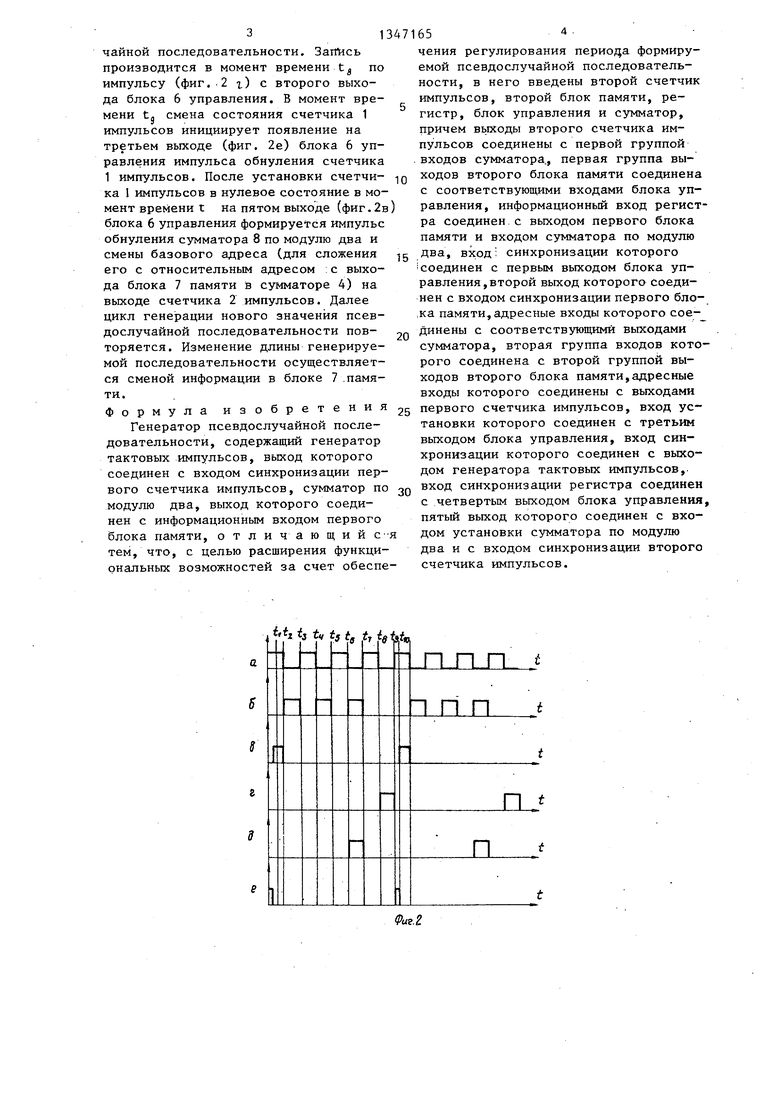

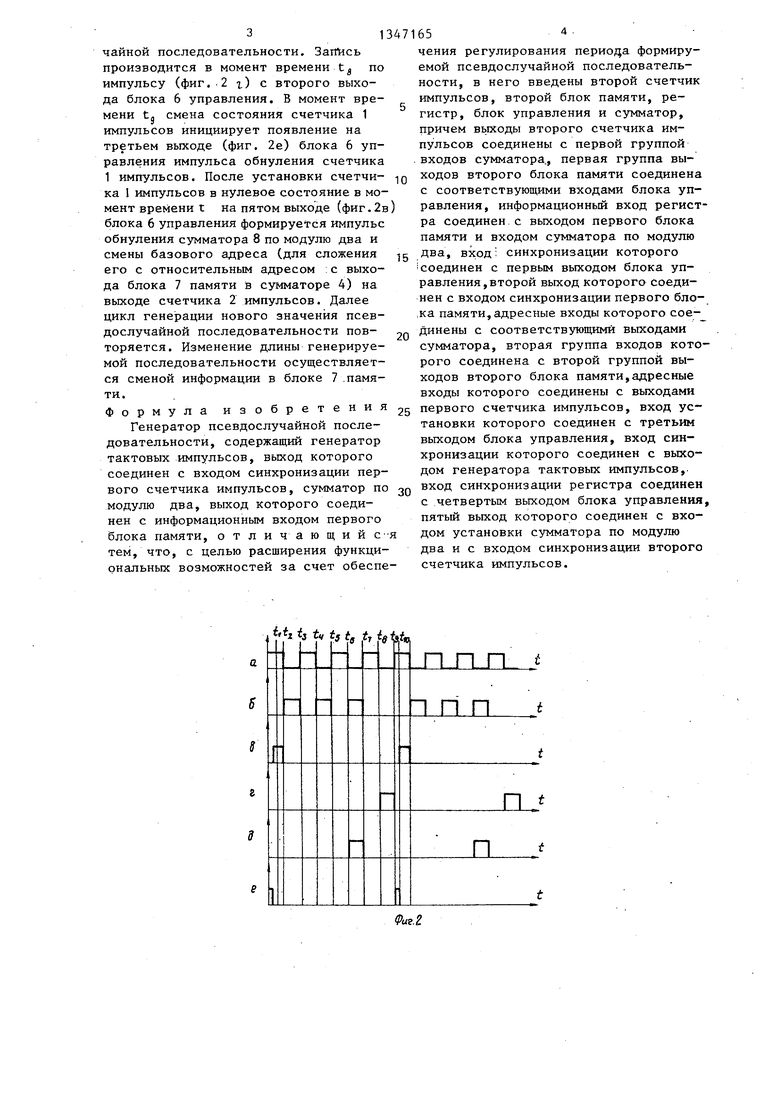

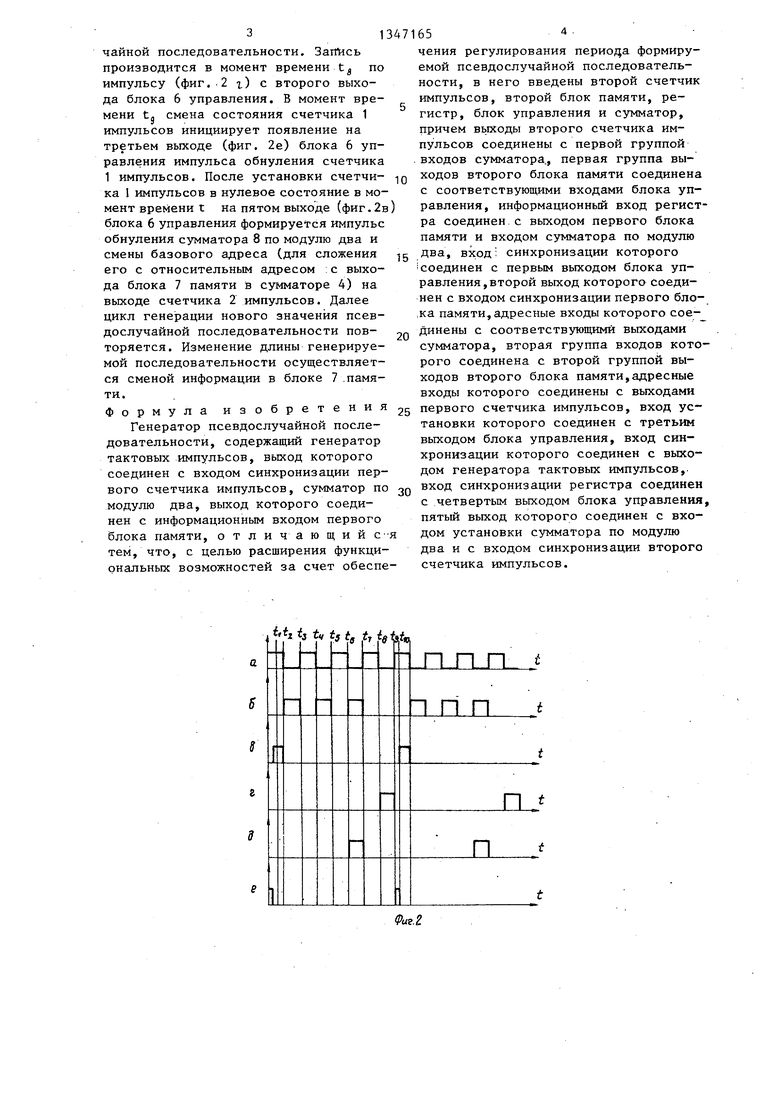

На фиг. 1 представлена структурная схема генератора псевдослучайной последовательности; на фиг. 2 - временные диаграммы работы блока управления; на фиг. 3 - схема блока управления.

Генератор псевдослучайной последовательности (фиг. 1) содержит первый 1 и второй 2 счетчики импульсов, генератор :5 тактовых импульсов, сумматор 4, первый блок 5 памяти, блок 6 управления, второй блок 7 памяти, сумматор 8 подмодулю два, регистр 9, информационный вход которого соединен с выходом первого блока 5 памяти и входом сумматора 8 по модулю два, выход которого соединен с информационным входом первого блока 5 памяти, адресные входы которого соединены с соответствующими выходами сумматора 4, входы первой группы входов которого соединены с соответствующими выходами второго счетчика 2 импульсов, вход синхронизации которого соединен с пятым выходом блока 6 управления и входом установки сумматора 8 по модулю два, вход синхронизации которого соединен с первым выходом блока 6 управления, второй выход которого соединен с входом синхронизации первого блока 5 памяти. Выход генератора 3 тактовых импульсов соединен с входом синхронизации блока 6 управления и входом синхронизации первого счетчика 1 импульсов, установочньй вход которого соединен с третьим входом блока 6 управления, входы которого соединены с соответствующими выходами первой группы выходов второго блока 7 памяти адресные входы которого соединены с соответствующими выходами первого счетчика 1 импульсов. Выходы второй группы выходов соединены с соответствующими входами второй группы входов сумматора 4. Четвертый выход блока 6 управления соединен с входом синхронизации регистра 9.

5

0

5

0

5

0

5

0

5

Блок 6 управления (фиг. 3) содержит дешифратор 10, схему укорочения импульса, состоящую из последователь-, но соединенных RC-цепи, первого 11 и второго 12 элементов НЕ, и схему формирования импульсов, состоящую из последовательно соединенных третьего элемента НЕ 13 и элемента И 14. Соединение выходов блока 6 управления с другими блоками устройства показано соответствующей нумерацией выходов блока 6 управления (фиг. 3).

Генератор псевдослучайной последовательности работает следующим образом.

В момент времени t (фиг. 2) первый счетчик 1 -импульсов и сумматор 8 по модулю два находятся в нулевом состоянии. Содержимое i-й ячейки первого блока 5 памяти поступает на вход сумматора 8 по модулю два. В момент времени t2 по импульсу с первого выхода (фиг. 26) блока 6 управления информация с выхода первого блока 5 памяти записывается в сумматор 8 по модулю два. В момент времени t по импульсу с выхода генератора 3 тактовых импульсов (фиг. 2 и) происходит смена состояния первого счетчика 1 импульсов. При этом на выходах второй группы выходов второго блока 7 памяти устанавливается относительный адрес j-й ячейки блока 5 памяти, информация с выхода которого в момент времени t по импульсу с первого выхода (фиг. 2) блока 6 управления складывается по модулю два с информацией, записанной ранее в сум- - маторе 8 по модулю два. Б момент времени tj происходит смена состояния первого счетчика 1 импульсов, -а на выходе второго блока 7 памяти устанавливается относительный адрес К-й ячейки, содержимое которой суммируется с содержимым су1 1матора 8 по модулю два в момент времени t . Одновременно по импульсу с четвертого выхода (фиг. 29) блока 6 управления осуществляется запись информации с выхода блока 5 памяти в-регистр 9, т.е. смена информации на выходе устройства. В момент времени t-, после смены состояния счетчика 1 импульсов на выходе второго блока 7 памяти устанавливается относительный адрес ячейки блока 5 памяти, в которую Записывается сформированное в сумматоре 8 по модулю два значение псевдослу31

чайной последовательности. Запись производится в момент времени t по импульсу (фиг..2 г) с второго выхода блока 6 управления. В момент времени tg смена состояния счетчика 1 импульсов инициирует появление на третьем выходе (фиг. 2е) блока 6 управления импульса обнуления счетчика 1 импульсов. После установки счетчи- ка 1 импульсов в нулевое состояние в момент времени t на пятом выходе (фиг.2в блока 6 управления формируется импульс обнуления сумматора 8 по модулю два и смены базового адреса (для сложения его с относительным адресом :с выхода блока 7 памяти в сумматоре 4) на выходе счетчика 2 импульсов. Далее цикл генерации нового значения псевдослучайной последовательности пов- торяется. Изменение длины генерируемой последовательности осуществляется сменой информации в блоке 7 .памяти. Формула изобретения

Генератор псевдослучайной последовательности, содержащий генератор тактовых импульсов, выход которого соединен с входом синхронизации первого счетчика импульсов, сумматор по модулю два, выход которого соединен с информационным входом первого блока памяти, отличающий с тем, что, с целью расширения функциональных возможностей за счет обеспе65

чения регулирования периода формируемой псевдослучайной последовательности, в него введены второй счетчик импульсов, второй блок памяти, регистр, блок управления и сумматор, причем вьгходы второго счетчика импульсов соединены с первой группой входов сумматора., первая группа выходов второго блока памяти соединена с соответствующими входами блока управления, информационный вход регистра соединен.с выходом первого блока памяти и входом сумматора по модулю два, вход; синхронизации которого Соединен с первым выходом блока управления, второй выход которого соединен с входом синхронизации первого бло- ,ка памяти, адресные входы которого сое- динены с соответствующими выходами сумматора, вторая группа входов которого соединена с второй группой выходов второго блока памяти,адресные входы которого соединены с выходами первого счетчика импульсов, вход установки которого соединен с третьим выходом блока управления, вход синхронизации которого соединен с выходом генератора тактовых импульсов,- вход синхронизации регистра соединен с четвертым выходом блока управления пятый выход которого соединен с входом установки сумматора по модулю два и с входом синхронизации второго счетчика импульсов.

:|:

/ f

Zbe.J

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 2009 |

|

RU2416157C1 |

| Устройство для формирования тестов | 1984 |

|

SU1226472A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1317486A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Генератор псевдослучайных последовательностей | 1986 |

|

SU1406739A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU968816A1 |

| Генератор псевдослучайных сигналов | 1986 |

|

SU1347166A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

Изобретение относится к импульсной технике и может быть использовано в вычислительной технике, системах автоматического управления и системах передачи информации. Цель изобретения - расширение функциональных возможностей - достигается за счет обеспечения регулирования периода, формируемой псевдослучайной последовательности. Для этого в генератор псевдослучайной последовательности введены второй счетчик 2 импульсов, второй блок 7 памяти, сумматор 8 по модулю два и регистр 9. Кроме того, устройство содержит первый счетчик 1, генератор 3 тактовых импульсов, сумматор 4,первый блок 5 памяти и блок & управления. Изменение длительности, генерируемой последовательности осуществляется сменой информации в блоке 7 памяти. Функциональная схема и поэлементный состав блока 6 управления, а также временные диаграммы, поясняющие работу устройства,приводятся в описании изобретения. 3 ил. (Л 0н W 4 1 о: Cfl до/х

Редактор И. Шулла

Составитель Ю. Бурмистров

Техред и.ПоповичКорректор А. Тяско

Заказ 5127/51Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Варакин Л.Е | |||

| Теория сложных сигналов | |||

| - М.: Советское радио, 1970, с | |||

| Питательное приспособление к трепальным машинам для лубовых растений | 1922 |

|

SU201A1 |

| Генератор псевдослучайной последовательности | 1981 |

|

SU959076A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-23—Публикация

1985-10-08—Подача