Изобретение относится к устройствам управления сложными объектами и может найти применение в автоматизированных системах идентификации электрофизических объектов.

Целью изобретения являет ся расширение функциональных возможностей путем возможности задержки серии импульсов и упрощение устройства.

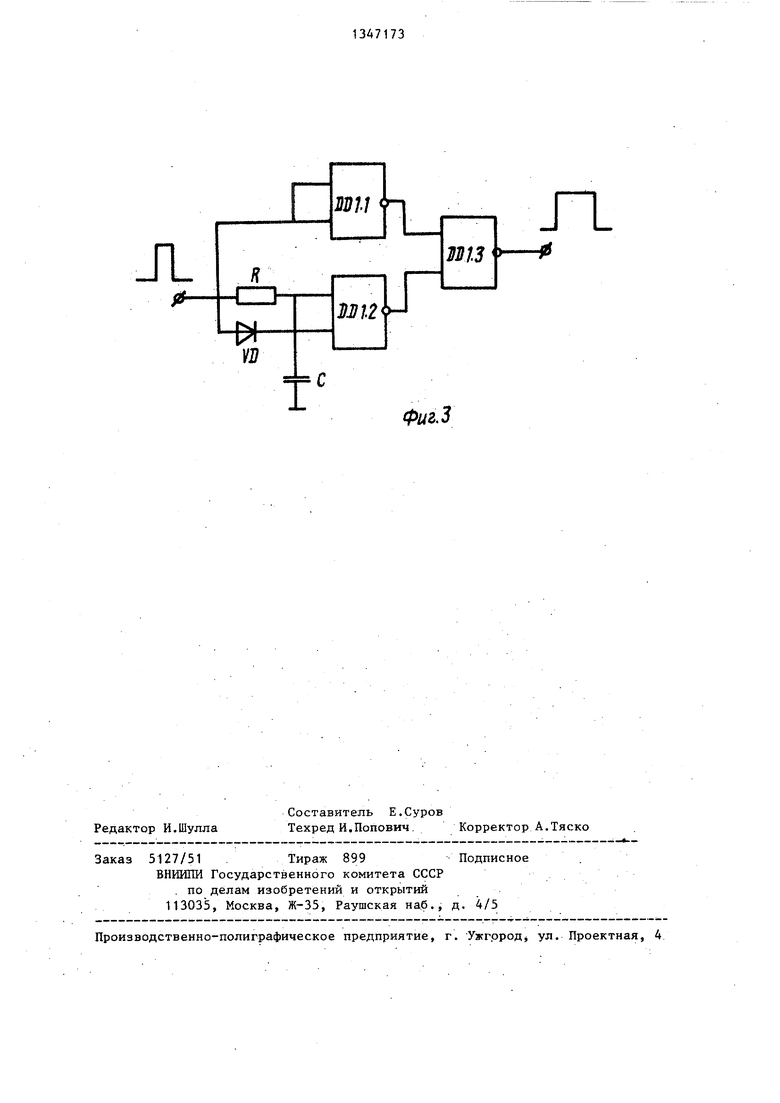

На фиг. 1 представлена структурная схема предлагаемого генератора; на фиг. 2 - диаграммы,поясняющие его работу;на фиг. 3 - формирователь выходных импульсов.

Многоканальный генератор задержанных импульсов состоит из генератора 1 эталонной частоты, счетчика 2, фиксатора 3 нулевого уровня,мультиплексора 4, оперативного запоминающего устройства (ОЗУ) 5, сумматора 6, демультиплексора 7 и формирователей 8.1-8.П выходных импульсов, где п 2 - 1 - число каналов задержки.

Генератор 1 эталонной частоты своим выходом соединяется в входом суммирующего счетчика 2 и входом разрешения выборки ОЗУ 5. Выходная шина младших-т разрядов счетчика 2 подключена к входу фиксатора 3 нулевого уровня,а также к шинам управления мультиплексора 4 и демультиплексора 7. Шина старших-1 разрядов счетчика 2 соединяется с одной из входных шин сумматора 6, к другой входной шине которого подключена выходная инверсная шина мультиплексора 4. Выходная шина сумматора 6 соединяется с адресной шиной ОЗУ 5. Выход последнего подключается к информационному входу демультиплексора 7 , к каждому из выходов которого подключается формирователь 8 выходных импульсов. Задерживаемые импульсы подаются, на информационный вход 9 ОЗУ 5. Источники кодов задержки каждого из каналов подключаются к соответствующей информационной шине мультиплексора 4.

Многоканальный генератор -задержан .ных ммпульсов работает следующим образом.

Счетчик 2 своими младшими т-раз- рядами формирует цикл поочередного опроса кодов задержки, а старшими 1-разрядами - базовый адрес ОЗУ 5. Цикл начинается обнулением младших разрядов и увеличением числа, записанного в старших, т.е. изменение базового адреса на единицу,при этом мультиплексор.4, проинвертировав код на входной шине D, подает на одну из входных шин сумматора 6 код О, т.е. логический О во всех разрядах,в результате на адресный вход ОЗУ 5 проходит без изменения

0 базовый адрес данного цикла Ар. Если в это время на информационный вход D ОЗУ 5 приходит задерживаемый импульс, в ячейку по этому адресу записывается логическая 1,если

5 импульса нет, то в нее записывается О, поскольку на вход разрешения записи подается низкий логический уровень с выхода схемы фиксации нулевого уровня. В течение следующих

0 ;тактов цикла ОЗУ 5 переключаются в режим считывания, а на шину сумматора .6 поочередно поступают инвертированные коды задержки каналов и на его выходе формируются числа Т или

5 относительный адрес (относительно базового), равный Т|, k 1,..., 2 - 1. Смысл такого построения схемы в том (фиг. 2а), чтобы базовый адрес, перемещаясь в поле ячеек

0 ОЗУ 5, производил активизацию одного из них в момент прихода задерживаемого импульса, а считывается информация из нее через то время, на которое импульс в данном канале

j. задерживается. Задержанный импульс с выхода ОЗУ 5 проходит на выход демультиплексора 7, соответствующий номеру канала, определяемого в данном такте, поскольку на адресный

0 вход демультиплексора 7 поступает тот же код, что и на адресный вход мультиплексора 4. В результате временного разделения импульсы на выходе могут быть очень короткими,поэто5 У о поступают после распределения на входы формирователей 8 выходных импульсов.

Во избежание нарушения работы ге- ннератора из-за конечного числа

Q ячеек ОЗУ 5 необходимо выбрать соответствующую разрядность счетчика 2 и ОЗУ 5 таким образом, чтобы обновление информации в данной ячейке могло произойти только после считываg ния предьщущей информации, т.е. необходимо, чтобы выполнялось условие 7 е fTvo-x г, , к )

В этом случае ситуация, возникшая

в результате суммирования по модулю

два (т.е. без переноса из старшего разряда сумматора (фиг. 26), не приводит к сбою, поскольку ячейка с базовым адресом А с вновь опрашивается через данное время, так как после ячейки 2 - 1 выбирается ячейка 0. Число Т| зависит от длительности задержки t в канале и точности ее

установки Е и определяется отно/J /1

шением Т log ,-g операция взятия ближайшего большего целого числа. Разрядность сумматора б и ОЗУ 5 1 max ClogjT, если задано число каналов п, то разрядность выбирается из условия m Clogjn, тогда разрядность счетчика 2 составляет 1+т. Частота генератора 1 эталонной частоты определяется из условия

Г Е.

Формула изобретения

Многоканальный генератор задержанных импульсов, содержащий генератор эталонной частоты, счетчик, к выходной шине младших разрядов которогр подключен фиксатор нулевого уровня,: запоминающее устройство и

7;«7-Л7-/

-г -г т к

формирователи выходных импульсов по числу каналов задержки, отличающийся тем,что, с целью расширения функциональных возможностей путем возможности задержки серии импульсов и упрощения устройства, в него введены сумматор, мультиплексор и демультиштексор, причем запоминающее

0 устройство выполнено в виде оперативного запоминающего устройства, вход разрешения выборки которого подключен к генератору эталонной частоты, а к адресному входу подключен выход

5 мультиплексора через сумматор, к второму входу которого подключен выход старших разрядов счетчика, а выход младших разрядов счетчика соединен с входом управления мультиплек0 сора и демультиплексора,выход фиксатора нулевого уровня соединен с входом разрешения записи оперативного запоминающего устройства,информационный вход которого подключен к

5 шине входных импульсов, а выход соединен с информационным входом демультиплексора, к выходам которого подключены формирователи выходных импульсов, при этом соответствующая

0 информационная-шина мультиплексора подключена к шине кода задержки каждого из каналоё.

(риг. 2

JL

w

1IM2

Редактор Й.Шулла

Составитель Е.Суров

Техред И.Попович, Корректор А,Тяско

Заказ 5127/51 . Тираж 899 Подписное ВНИИПИ Государственного комитета СССР

. по делам изобретений и открытий 113035, Москва, Ж-35, Раушская на.б., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород ул. Проектная, 4

тз

)-

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Цифровое устройство для управления ведомым сетью преобразователем | 1986 |

|

SU1381668A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Формирователь сложной функции | 1985 |

|

SU1287135A1 |

| Устройство цифроаналогового преобразования | 1985 |

|

SU1361716A1 |

Изобретение относится к устройствам управления сложными объектами и может найти применение в автоматизированных системах идентификации электрофизических объектов. Целью изобретения является расширение функциональных возможностей путем задержки серии импульсов и упрощение устройства. Для достижения этой цели в устройство дополнительно введены мультиплексор 4, сумматор 6 и де- мультиплексор 7, а запоминающее устройство выполнено в виде оперативного запоминающего устройства -(ОЗУ) 5. Кроме того, устройство содержит генератор 1 эталонной частоты,счетчик 2, фиксатор 3 нулевого уровня, формирователи выходных импульсов 8.1-8.П, где п - число каналов задержки определяемое из формулы п 2 - 1, где m - число младших разрядов, выбираемой из условия m logj,n. Для исключения возможности нарушения работы генератора из-за конечного числа ячеек ОЗУ 5 необходимо выбрать соответствующую разрядность счетчика 2 и ОЗУ 5 с таким расчетом, чтобы обновление информации в данной ячейке производилось только после считывания пре- дыдущ.ей информации. 3 ил. i (Л С со со J со

| Важенина З.Н | |||

| и др | |||

| Методы и схемы временной задержки импульсных сигналов | |||

| - М.: Советское радио,1971 | |||

| Многоканальный генератор задержанных импульсов | 1976 |

|

SU564715A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-23—Публикация

1985-11-26—Подача