Изобретение относится к цифропой вычислительной технике, к ycTpoiicTFja для генерирования с-инхрониэирующих

сигналои.

Целью изобретения является расширение функциональных возможностей за счет оперативного изменения выходных импульсов.

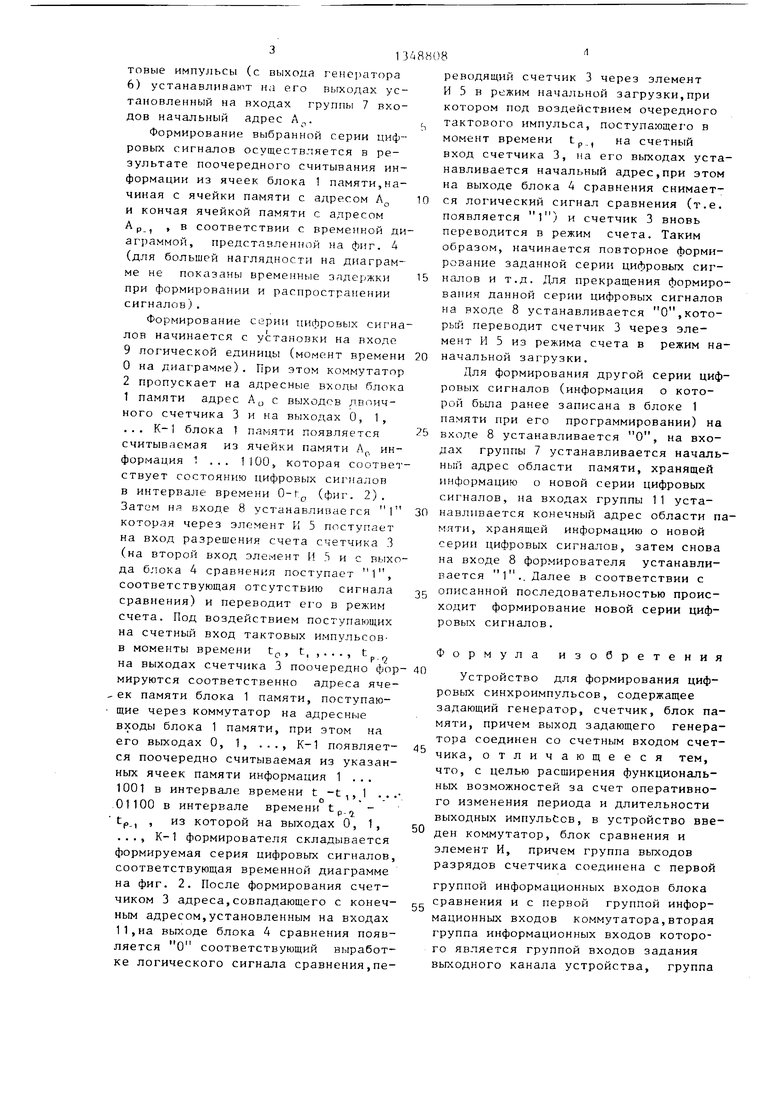

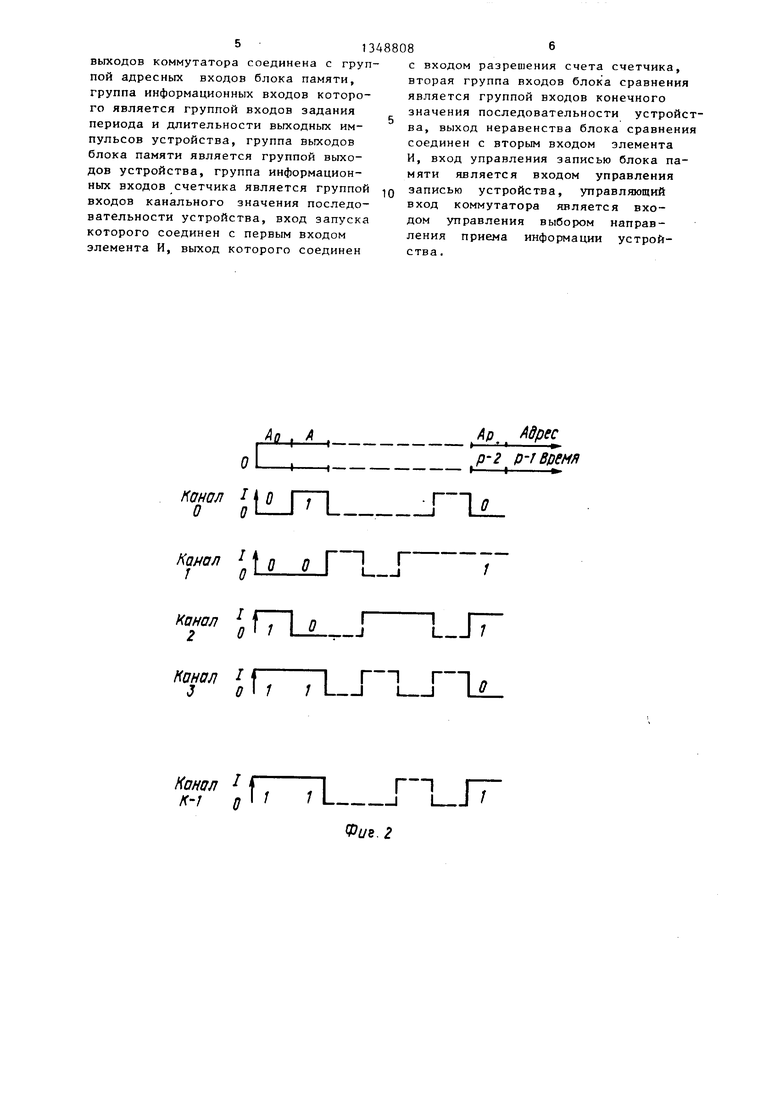

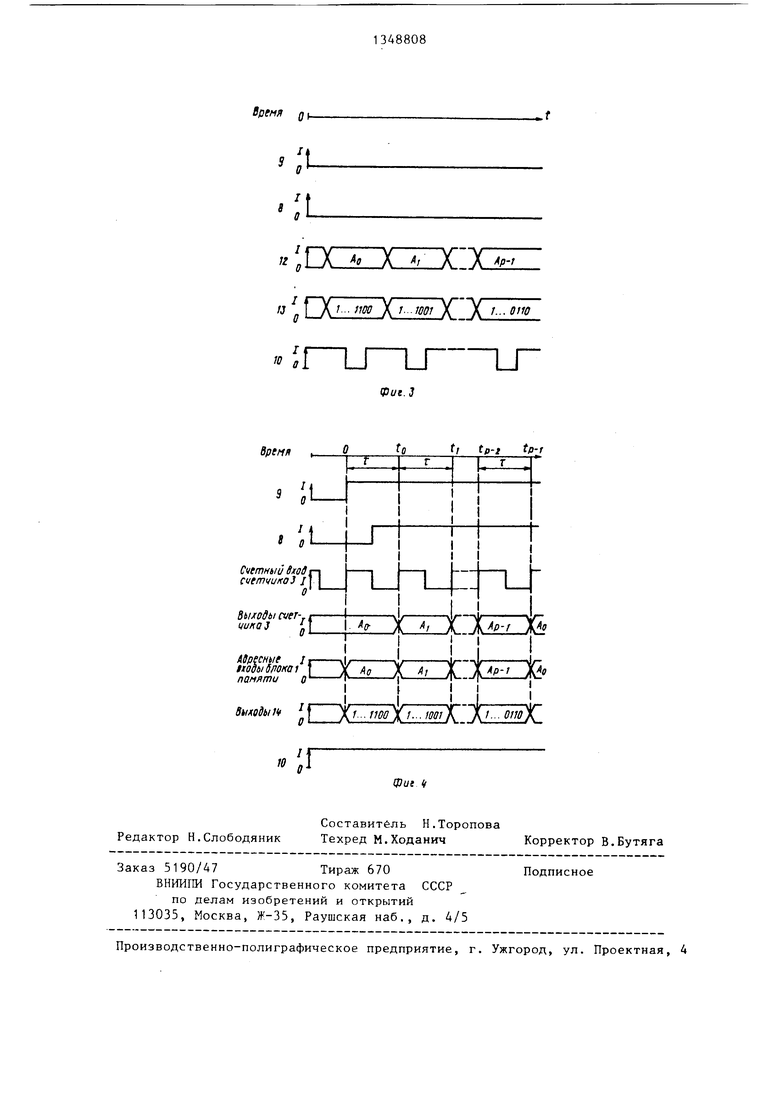

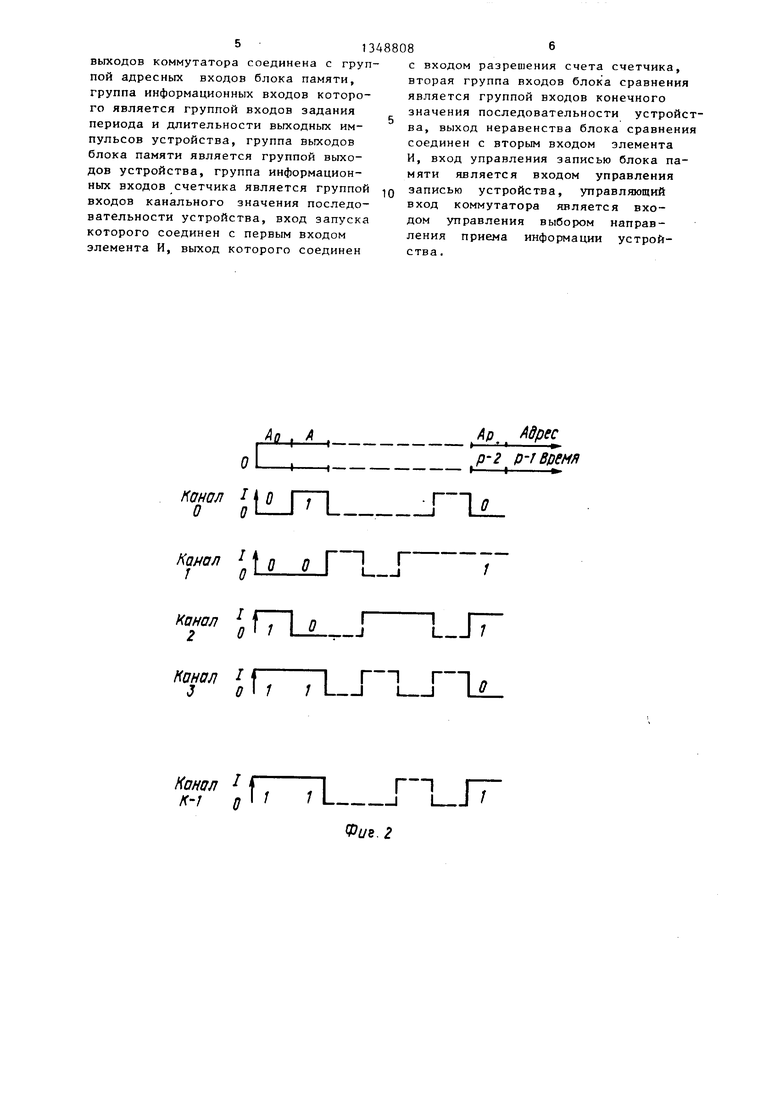

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - временная диаграмма примера формирования импульсов для К каналов;на фиг. 3 - временная диаграмма управления записью информации п блок памяти; на фиг. 4 - временная диаграмма считывания информации из блока памяти.

Устройство содержит блок 1 памяти коммутатор 2, счетчик 3, блок А сравнения, элемент И 5, задающий генера- тор 6, группу 7 входов начального значения, вход 8 запуска, вход 9 управления выбором направления приема информации, вход 10 управления записью, группу ВХО/10Н I 1 конечного зна- чения, группу входов 12 задания выходного канала, группу входов 13 задания периода и /иштельности выходны импульсов, группу выходов 14.

Устройство работает следующим г - разом.

Работа начинается с ег о прог-рамми рования для формирования необходимых серий цифровых сигналов. Программирование осуществляется путем записи в -лок 1 памяти информации о формируемых сериях цифровых (сигналов.

Рассмотрим пример записи в блок 1 памяти информации об одно11 из серий цифровых сигналов, отражающей изменение во времени каждого из формируемых по соотнетсткующему каналу формирователя цифровых сигналов, и последующего формирования из нее серии цифровых сиг налов, по К каналам в соответствии с временной диаграммо приведенной на фиг. 2. Изменения во времени (фпг. 2) пифровых сигнало равны периоду тактовр 1х импульсов, генерируемых за/ акицим генератором 6. Состояние цифроных сигналов по каналам О, 1 , . . . , К - I и течение любого указанног о шлг.ю интервала времени выражается двоичным числом, в котором его ну.чеиому разряду соответст- вует состоян 1е пифровог о сигнала по каналу О, периому разряду - состояние цифрового сип .чл а по каналу 1, .. , К-1. При :iroM число 1 ... 1100,

соответствующее состоянию цифровых сигналов в течение интернала времени 0-t , записывается в ячейку блока 1 памяти с адресом А, число 1 ... 1001, соответствующее состоянию циф- ров1,(х си1 налов в течение интервала времени ,, - в ячей.ку памяти с адресом А, наконец, число 1 ..,0110, соответствующее состоянию цифровых сигналов в течение интервала времени -р 9 tp 1 в ячейку памяти с адресом Ар .

Рассмотрим процесс записи информации в блок 1 памяти.

Перед записью на входах устройства установлены: на входе 8 запуска - О, на входе 9 - О, на входе 10 - 1. При этом коммутатор 2 пропускает на адресные входы блока 1 памяти адрес,установленный на входах 12 устройства. При записи информации в указанные выше ячейки памяти блока 1 необходимо в соответствии с временной диаграммой,представленной на фиг. 3, установить на входах группы 12 a/ipec ячейки памяти, на входах группы 13 - соответствующие значения разрядов двсл1чного числа, отражающего состояние цифровых сигналов, и за 1ем устанотзить на входе 10 устройства О.Таким образом, в области памяти блока 1, начиная с адреса А

0 5 0

5

и кончая адресом А,, , , записывается и хранится информация о серии цифроных сигналов, изображенных на фиг. 2. Аналогично в другие области памяти блока 1 может быть записана информация о Д1)угих сериях цифровых сигналов.

После окончания программирования ycTpcTi icTBo подготавливается к формированию одной из записанных в его блок 1 памяти серий цифровых сигналов. При этом на входе 10 устанавливается 1, на входах группы 7 устанавливается начальный адрес области памяти, хранящей информацию о выбранной для формирования серии цифровых сигна:1ов (в нашем примере это А„) , а на входах группь; 1 1 устанавливается конечный адрес этой области памяти (в наием примере это А, ). Установ- ленн1 |й ранее на входе 8 логический нуль поступает через элемент И 5 на вход разрешения счета счетчика 3, при этом счетчик 3 находится в режиме начальной загрузки,при котором П1 ступающие на его счетный вход так3П

товые импульсь (с выхода генератора 6) устанавливают на его выходах установленный на входах группы 7 входов начальный адрес А,,.

Формирование выбранной серии цифровых сигналов осуществляется в результате поочередного считывания информации из ячеек блока 1 памяти,начиная с ячейки памяти с адресом Л и кончая ячейкой памяти с адресом Ар , в соответствии с временной диаграммой, представленной на фиг, 4 (для большей наглядности на диаграмме не показаны временные злдержкн при формировании и распространении сигналов),

Формирование серии цифровых сигналов начинается с установки на входе 9 логической единицы (момент времени

0на диаграмме). При этом коммутатор 2 пропускает на адресные входы блока

1памяти адрес Ац с выходов двоичного счетчика 3 и на выходах О, 1, ... К-1 блока 1 памяти появляется считываемая из ячейки памяти А,, информация 1 ... 1100 которая соответствует состоянию цифровых сигналов

в интервале времени O-t (фиг. 2). Затем ня входе 8 устанавливаегея I которая через элемент И 5 поступает на вход разрешения счета счетчика 3 (на второй вход элемент И З и с выхода блока 4 сравнения поступает 1, соответствующая отсутствию сигнала сравнения) и переводит ег о в режим счета. Под воздействием поступающих на счетный вход тактовых импульсов- в моменты времени t , t, , . . . , t на выходах счетчика 3 поочередно формируются соответственно адреса ячеек памяти блока 1 памяти, поступающие через коммутатор на адресные входы блока 1 памяти, при этом на его выходах О, 1, ..., К-1 появляется поочередно считываемая из указанных ячеек памяти информация 1 ... 1001 в интервале времени t -t ,, 1 . . .

о

01100 в интервале времени tp -р-

ИЗ которой на выходах О, 1,

..., К-1 формирователя складывается формируемая серия цифровых сигналов, соответствующая временной диаграмме на фиг. 2. После формирования счетчиком 3 адреса,совпадающего с конечным адресом,установленным на входах 11,на выходе блока 4 сравнения появляется О соответствующий выработке логического сигнала сравнения,пе8

реводящий счетчик 3 через элемент И 5 в режим начальной загрузки,при котором под воздействием очередного

тактового импульса, поступающег о в момент времени tp , на счетный вход счетчика 3, на его выходах устанавливается начальный адрес,при этом на выходе блока А сравнения снимается логический сигнал сравнения (т.е. появляется l) и счетчик 3 вновь переводится в режим счета. Таким образом, начинается повторное формирование заданной серии цифровых сигналов и т.д. Для прекращения формирования данной серии цифровых сигналов на входе 8 устанавливается О,который переводит счетчик 3 через элемент И 5 из режима счета в режим наначальной загрузки.

Для формирования другой серии цифровых сигналов (информация о которой была ранее записана в блоке 1 памяти при его программировании) на

входе 8 устанавливается О, на входах группы 7 устанавливается начальный адрес области памяти, хранящей информацию о новой серии цифровых сигналов, на входах группы 11 устанавливается конечный адрес области памяти, хранящей информацию о новой серии цифровых сигналов, затем снова на входе 8 формирователя устанавливается 1.. Далее в соответствии с

описанной последовательностью происходит формирование новой серии цифровых сигналов.

Формула изобретения

Устройство для формирования цифровых синхроимпульсов, содержащее задающий генератор, счетчик, блок памяти, причем выход задающего генератора соединен со счетным входом счетчика, отличающееся тем, что, с целью расширения функциональных возможностей за счет оперативного изменения периода и длительности выходных импульсов, в устройство вве- ден коммутатор, блок сравнения и элемент И, причем группа выходов разрядов счетчика соединена с первой

группой информационных входов блока сравнения и с первой группой информационных входов коммутатора,вторая группа информационных входов которого является группой входов задания выходного канала устройства, группа

выходов коммутатора соединена с группой адресных входов блока памяти, группа информационных входов которого является группой входов задания периода и длительности выходных импульсов устройства, группа выходов блока памяти является группой выходов устройства, группа информационных входов счетчика является группой входов канального значения последовательности устройства, вход запуска которого соединен с первым входом элемента И, выход которого соединен

0 f .-

11 Q Г

/7/7 I1 I1

J о о J

Конол г П I I /г-; {j 1 1 1 L

Фиъ.г

с входом разрешения счета счетчика, вторая группа входов блока сравнения является группой входов конечного значения последовательности устройства, выход неравенства блока сравнения соединен с вторым входом элемента И, вход управления записью блока памяти является входом управления записью устройства, управляющий вход коммутатора является входом управления выборюм направления приема информации устройства ,

Ар Адрес

р-2 р-гврем/}

8р(мя QI

0 X t X X p-

13 w X g )Г X

Заказ 5190/47Тираж 670

ВНИИГ1И Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

w

ffl

0 tg-ffjO r

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестовых последовательностей | 1989 |

|

SU1675890A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

| Устройство регистрации электрического импульса | 1988 |

|

SU1596256A1 |

| Система управления многопозиционной индукционной нагревательной установкой | 1983 |

|

SU1121789A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| Устройство для обработки видеоинформации | 1986 |

|

SU1322320A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

Изобретение относится к цифровой вычислительной технике, к устройствам для генерирования синхронизирующих сигналов. Отличительной особенностью устройства является возможность оперативного изменения выходных сигналов. Целью изобретения является расширение функциональных возможностей за счет оперативного изменения выходных сигналов. Поставленная цель достигается за счет введения коммутатора 2 и блока 4 сравнения. 4 ил. J2 13 С в f}« со 4 00 00 о 00 Фиг. /

| Приборы и техника эксперимента, № 2, 1984 | |||

| М.:Наука, с | |||

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

| Патент США № 4404644, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-30—Публикация

1985-08-01—Подача