Фиг.2 ,

Изобретение относится к вычислительной технике, к устройствам для формирования тестов, преимущественно к созданию аппаратуры тестирования цифровых устройств.

Целью изобретения является расширение технических возможностей за счет многократного увеличения одновременно формируемых различных независимых друг от друга последовательностей цифровых сигналов.

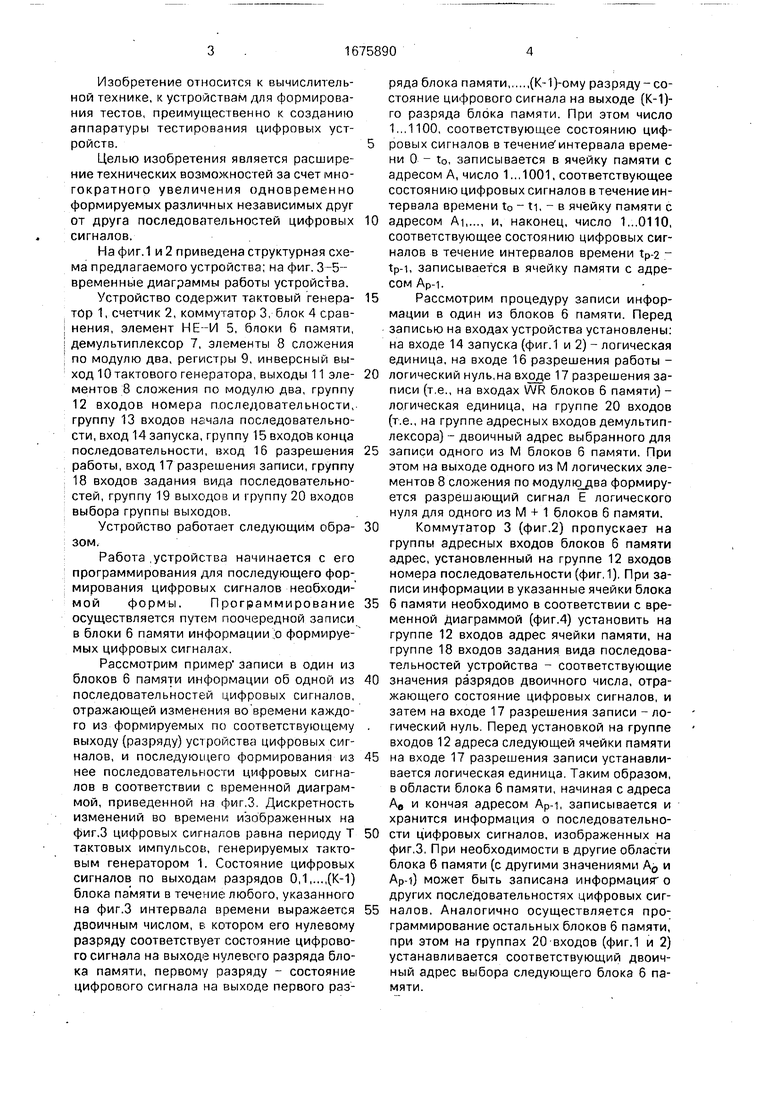

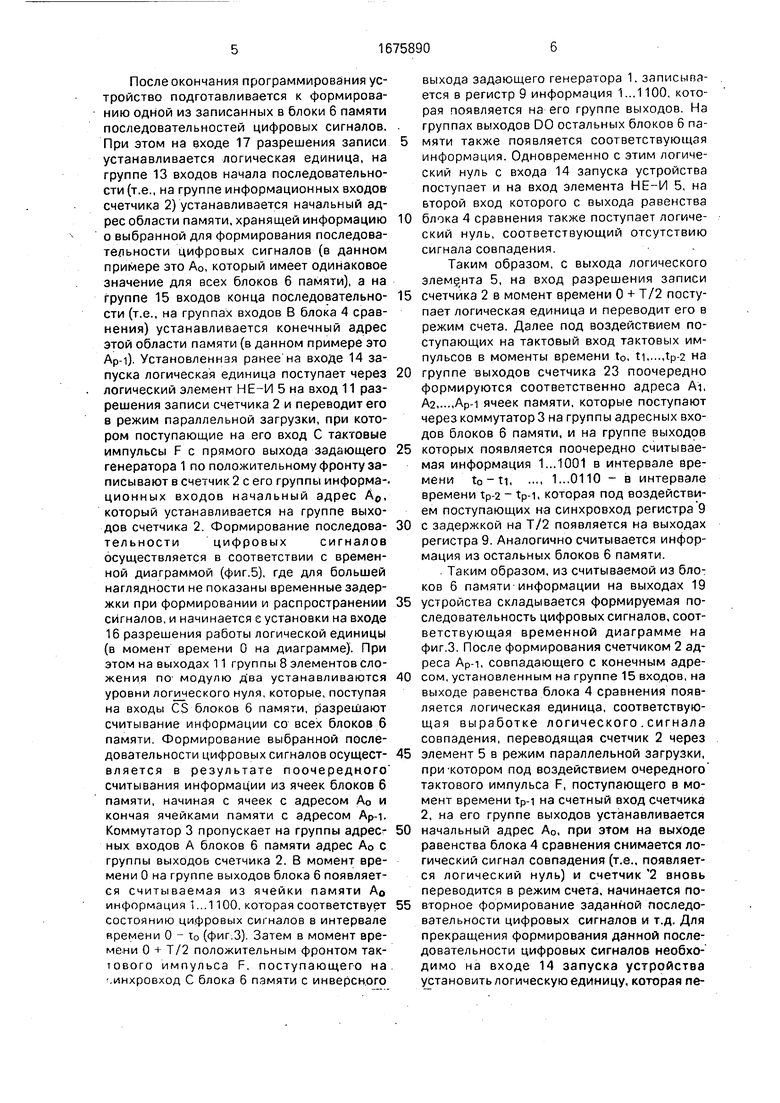

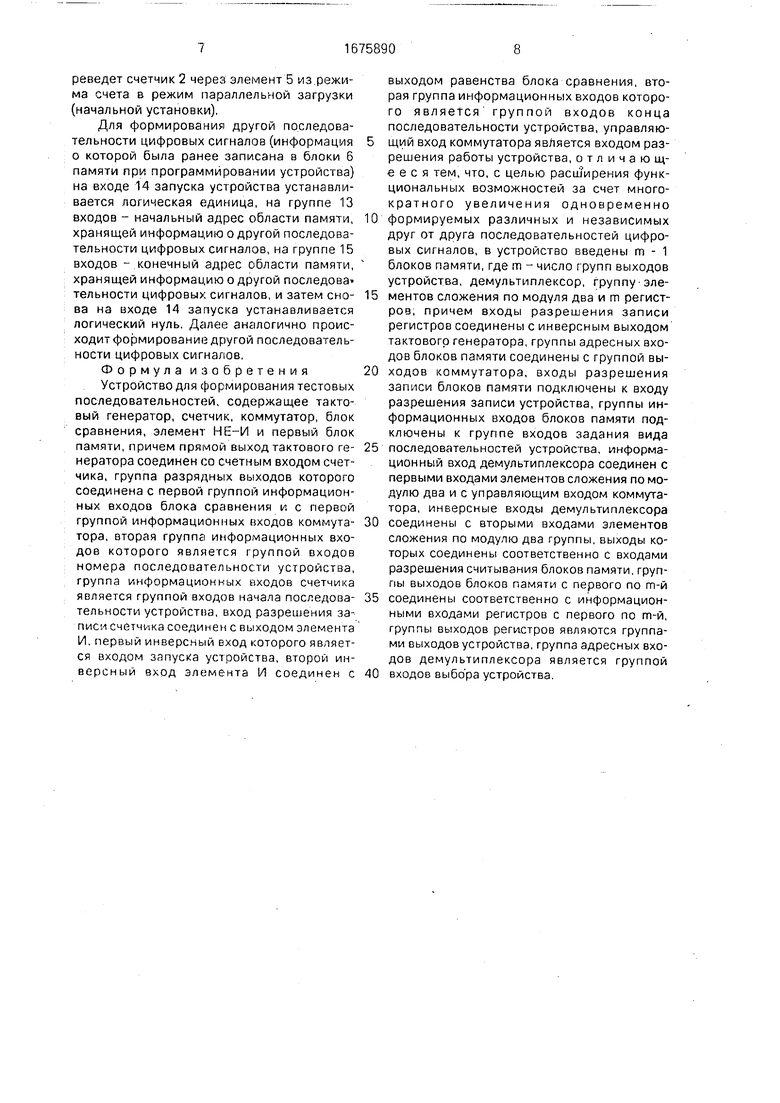

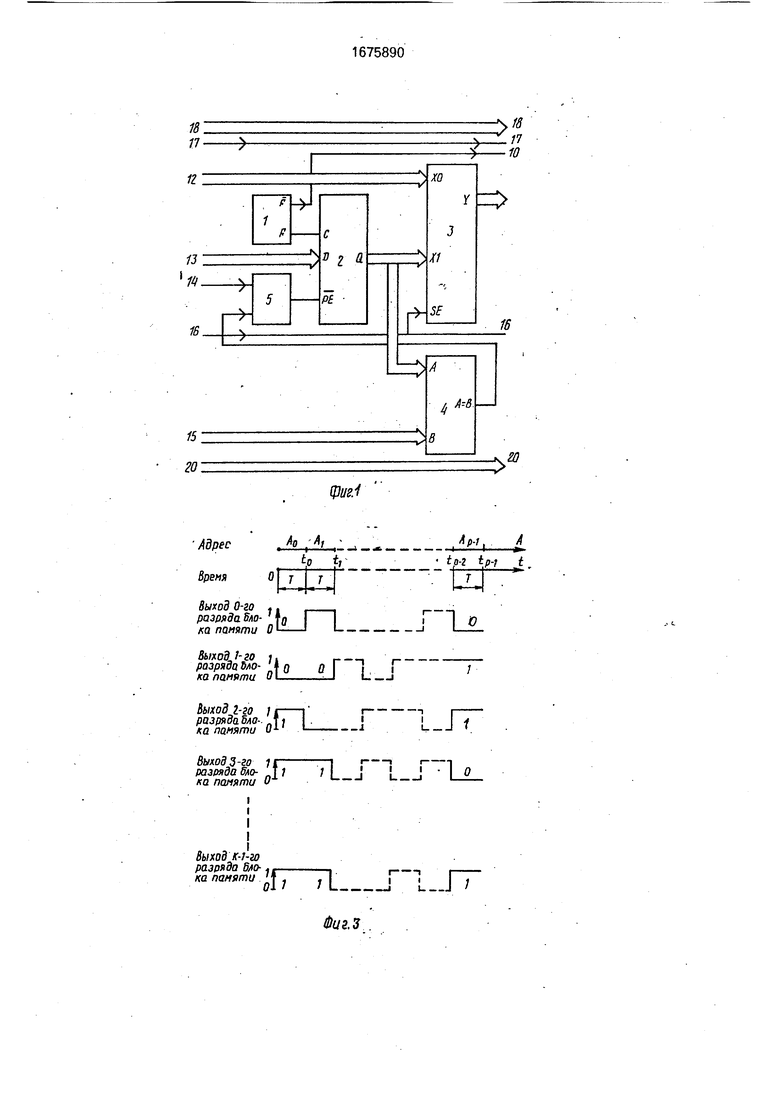

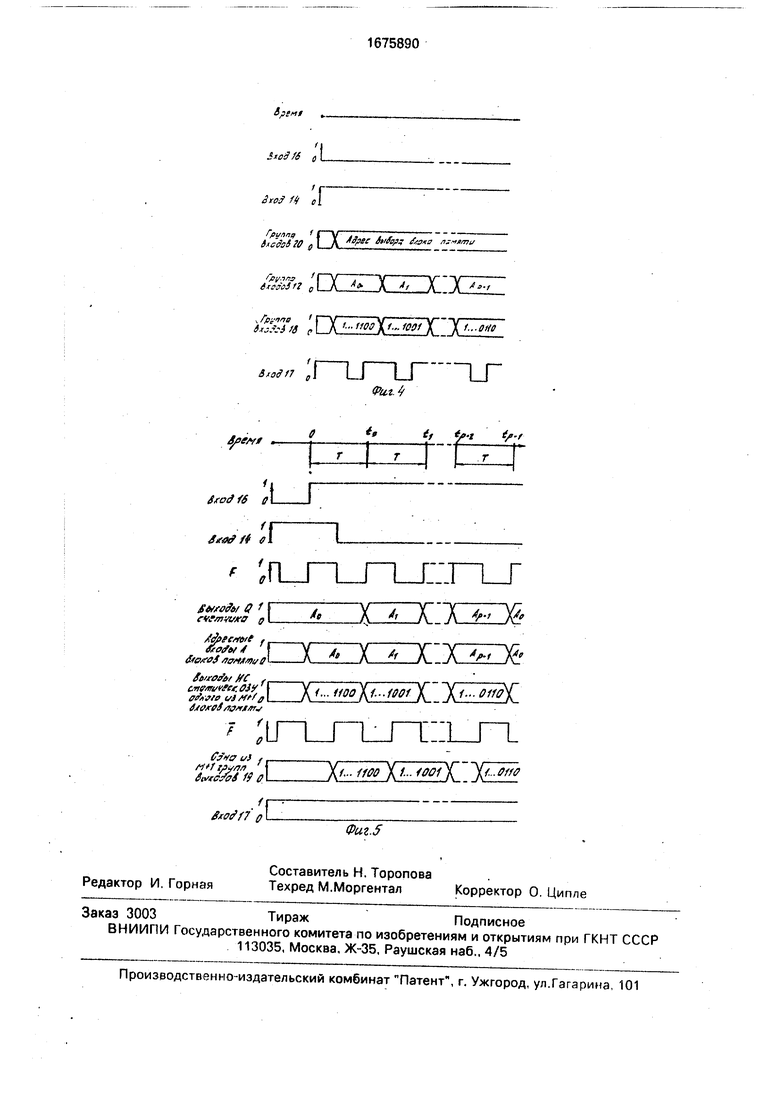

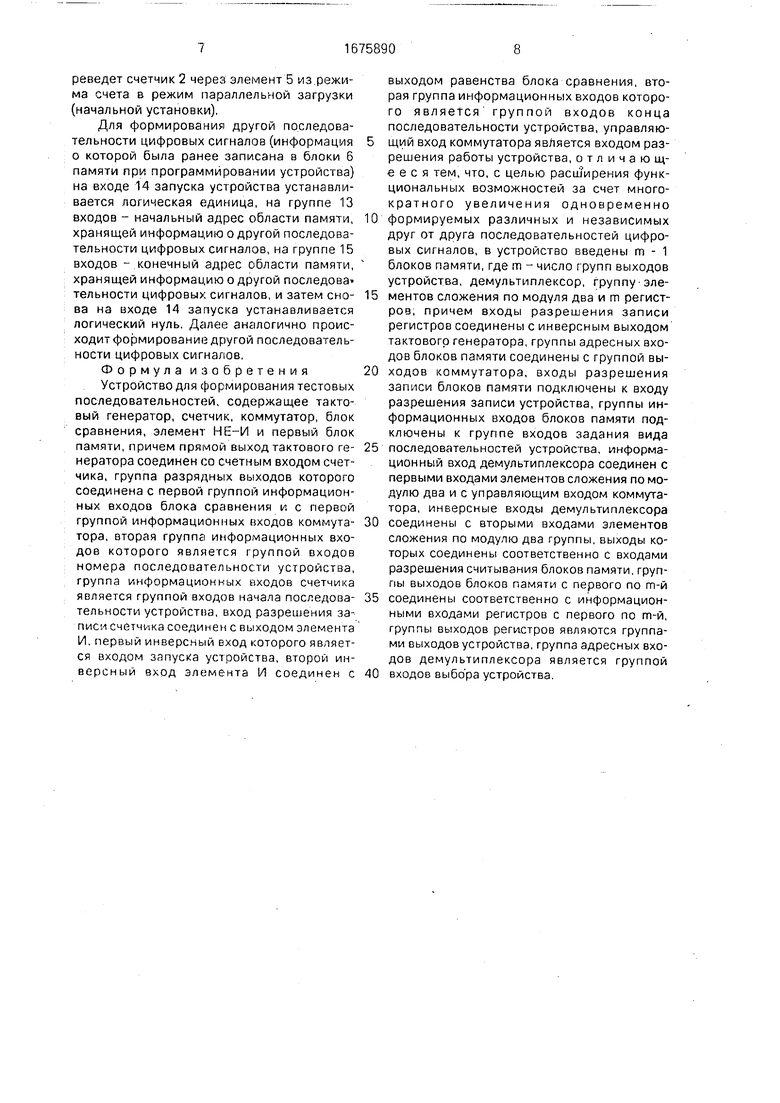

На фиг. 1 и 2 приведена структурная схема предлагаемого устройства; на фиг. 3-5- временные диаграммы работы устройства.

Устройство содержит тактовый генера- тор 1, счетчик 2, коммутатор 3, блок 4 сравнения, элемент НЕ-И 5, блоки 6 памяти, демультиплексор 7, элементы 8 сложения по модулю два, регистры 9, инверсный выход 10 тактового генератора, выходы 11 эле- ментов 8 сложения по модулю два, группу 12 входов номера последовательности, группу 13 входов начала последовательности, вход 14 запуска, группу 15 входов конца последовательности, вход 16 разрешения работы, вход 17 разрешения записи, группу 18 входов задания вида последовательностей, группу 19 выходов и группу 20 входов выбора группы выходов.

Устройство работает следующим обра- зом.

Работа .устройства начинается с его программирования для последующего формирования цифровых сигналов необходимой формы. Программирование осуществляется путем поочередной записи в блоки 6 памяти информации Ј формируемых цифровых сигналах.

Рассмотрим пример записи в один из блоков 6 памяти информации об одной из последовательностей цифровых сигналов, отражающей изменения во времени каждого из формируемых по соответствующему выходу (разряду) устройства цифровых сигналов, и последующего формирования из нее последовательности цифровых сигналов в соответствии с временной диаграммой, приведенной на фиг.З. Дискретность изменений во времени изображенных на фиг.З цифровых сигналов равна периоду Т тактовых импульсов, генерируемых тактовым генератором 1. Состояние цифровых

сигналов по выходам разрядов 0,1(К-1)

блока памяти в течение любого, указанного на фиг.З интервала времени выражается двоичным числом, в котором его нулевому разряду соответствует состояние цифрового сигнала на выходе нулевого разряда блока памяти, первому разряду - состояние цифрового сигнала на выходе первого разряда блока памяти(К-1)-ому разряду-состояние цифрового сигнала на выходе (К-1)- го разряда блока памяти. При этом число 1...1100, соответствующее состоянию цифровых сигналов в течение интервала времени 0 - to, записывается в ячейку памяти с адресом А, число 1...1001, соответствующее состоянию цифровых сигналов в течение интервала времени t0 - ti, - в ячейку памяти с

адресом AI и, наконец, число 1...0110.

соответствующее состоянию цифровых сигналов в течение интервалов времени tp-2 - tp-i, записывается в ячейку памяти с адресом Ар-1.

Рассмотрим процедуру записи информации в один из блоков 6 памяти. Перед записью на входах устройства установлены: на входе 14 запуска (фиг.1 и 2) - логическая единица, на входе 16 разрешения работы - логический нуль,на входе 17 разрешения записи (т.е., на входах WR блоков 6 памяти) - логическая единица, на группе 20 входов (т.е., на группе адресных входов демультип- лексора) - двоичный адрес выбранного для записи одного из М блоков 6 памяти. При этом на выходе одного из М логических элементов 8 сложения по модулю два формируется разрешающий сигнал Е логического нуля для одного из М + 1 блоков 6 памяти.

Коммутатор 3 (фиг.2) пропускает на группы адресных входов блоков 6 памяти адрес, установленный на группе 12 входов номера последовательности (фиг.1). При записи информации в указанные ячейки блока 6 памяти необходимо в соответствии с временной диаграммой (фиг.4) установить на группе 12 входов адрес ячейки памяти, на группе 18 входов задания вида последовательностей устройства - соответствующие значения разрядов двоичного числа, отражающего состояние цифровых сигналов, и затем на входе 17 разрешения записи - логический нуль. Перед установкой на группе входов 12 адреса следующей ячейки памяти на входе 17 разрешения записи устанавливается логическая единица. Таким образом, в области блока 6 памяти, начиная с адреса АО и кончая адресом Ар-1, записывается и хранится информация о последовательности цифровых сигналов, изображенных на фиг.З. При необходимости в другие области блока б памяти (с другими значениями А и Ap-i) может быть записана информация о других последовательностях цифровых сигналов. Аналогично осуществляется программирование остальных блоков 6 памяти, при этом на группах 20 входов (фиг.1 и 2) устанавливается соответствующий двоичный адрес выбора следующего блока 6 памяти.

После окончания программирования устройство подготавливается к формированию одной из записанных в блоки 6 памяти последовательностей цифровых сигналов. При этом на входе 17 разрешения записи устанавливается логическая единица, на группе 13 входов начала последовательности (т.е., на группе информационных входов счетчика 2) устанавливается начальный адрес области памяти, хранящей информацию о выбранной для формирования последовательности цифровых сигналов (в данном примере это А0, который имеет одинаковое значение для всех блоков 6 памяти), а на группе 15 входов конца последовательности (т.е., на группах входов В блока 4 сравнения) устанавливается конечный адрес этой области памяти (в данном примере это Ap-i). Установленная ранее на входе 14 запуска логическая единица поступает через логический элемент НЕ-И 5 на вход 11 разрешения записи счетчика 2 и переводит его в режим параллельной загрузки, при котором поступающие на его вход С тактовые импульсы F с прямого выхода задающего генератора 1 по положительному фронту записывают в счетчик 2 с его группы информа-. ционных входов начальный адрес А0, который устанавливается на группе выходов счетчика 2. Формирование последовательности цифровых сигналов осуществляется в соответствии с временной диаграммой (фиг.5), где для большей наглядности не показаны временные задержки при формировании и распространении сигналов, и начинается е установки на входе 16 разрешения работы логической единицы (в момент времени 0 на диаграмме). При этом на выходах 11 группы 8 элементов сложения по- модулю Два устанавливаются уровни логического нуля, которые, поступая на входы CS блоков 6 памяти, разрешают считывание информации со всех блоков 6 памяти. Формирование выбранной последовательности цифровых сигналов осуществляется в результате поочередного считывания информации из ячеек блоков 6 памяти, начиная с ячеек с адресом А0 и кончая ячейками памяти с адресом Ар-ч. Коммутатор 3 пропускает на группы адресных входов А блоков 6 памяти адрес А0 с группы выходов счетчика 2. В момент времени 0 на группе выходов блока 6 появляется считываемая из ячейки памяти АО информация 1 ...1100, которая соответствует состоянию цифровых сигналов в интервале времени 0 - to (фиг.З). Затем в момент времени 0 -+ Т/2 положительным фронтом тактового импульса F. поступающего на .инхровход С блока 6 памяти с инверсного

выхода задающего генератора 1. записывается в регистр 9 информация 1 ...1100, которая появляется на его группе выходов. На группах выходов DO остальных блоков 6 пэ- 5 мяти также появляется соответствующая информация. Одновременно с этим логический нуль с входа 14 запуска устройства поступает и на вход элемента НЕ-И 5, на второй вход которого с выхода равенства

0 блока 4 сравнения также поступает логический нуль, соответствующий отсутствию сигнала совпадения.

Таким образом, с выхода логического элемента 5, на вход разрешения записи

5 счетчика 2 в момент времени 0 + Т/2 поступает логическая единица и переводит его в режим счета. Далее под воздействием поступающих на тактовый вход тактовых импульсов в моменты времени to, titp-2 на

0 группе выходов счетчика 23 поочередно формируются соответственно адреса AI,

А2Ар-1 ячеек памяти, которые поступают

через коммутатор 3 на группы адресных входов блоков 6 памяти, и на группе выходов

5 которых появляется поочередно считываемая информация 1...1001 в интервале времени to - ti 1...0110 - в интервале

времени тр-2 - tp-i, которая под воздействием поступающих на синхровход регистра 9

0 с задержкой на Т/2 появляется на выходах регистра 9. Аналогично считывается информация из остальных блоков 6 памяти.

. Таким образом, из считываемой из блоков 6 памяти информации на выходах 19

5 устройства складывается формируемая последовательность цифровых сигналов, соответствующая временной диаграмме на фиг.З. После формирования счетчиком 2 адреса Ар-1, совпадающего с конечным адре0 сом, установленным на группе 15 входов, на выходе равенства блока 4 сравнения появляется логическая единица, соответствующая выработке логического.сигнала совпадения, переводящая счетчик 2 через

5 элемент 5 в режим параллельной загрузки, при котором под воздействием очередного тактового импульса F, поступающего в момент времени tp-i на счетный вход счетчика 2, на его группе выходов устанавливается

0 начальный адрес А0, при этом на выходе равенства блока 4 сравнения снимается логический сигнал совпадения (т.е., появляется логический нуль) и счетчик 2 вновь переводится в режим счета, начинается по5 вторное формирование заданной последовательности цифровых сигналов и т.д. Для прекращения формирования данной последовательности цифровых сигналов необходимо на входе 14 запуска устройства установить логическую единицу, которая переведет счетчик 2 через элемент 5 из режима счета в режим параллельной загрузки (начальной установки).

Для формирования другой последовательности цифровых сигналов (информация о которой была ранее записана в блоки 6 памяти при программировании устройства) на входе 14 запуска устройства устанавливается логическая единица, на группе 13 входов - начальный адрес области памяти, хранящей информацию о другой последовательности цифровых сигналов, на группе 15 входов - конечный адрес области памяти, хранящей информацию о другой последова тельности цифровых сигналов, и затем снова на входе 14 запуска устанавливается логический нуль. Далее аналогично происходит формирование другой последовательности цифровых сигналов.

Формула изобретения Устройство для формирования тестовых последовательностей, содержащее тактовый генератор, счетчик, коммутатор, блок сравнения, элемент НЕ-И и первый блок памяти, причем прямой выход тактового генератора соединен со счетным входом счетчика, группа разрядных выходов которого соединена с первой группой информационных входов блока сравнения и с первой группой информационных входов коммутатора, вторая группа информационных входов которого является группой входов номера последовательности устройства, группа информационных входов счетчика является группой входов начала последовательности устройства, вход разрешения записи счетчика соединен с выходом элемента И, первый инверсный вход которого является входом запуска устройства, второй инверсный вход элемента И соединен с

выходом равенства блока сравнения, вторая группа информационных входов которого является группой входов конца последовательности устройства, управляющий вход коммутатора является входом разрешения работы устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет многократного увеличения одновременно

формируемых различных и независимых друг от друга последовательностей цифровых сигналов, в устройство введены m - 1 блоков памяти, где m - число групп выходов устройства, демультиплексор, группу элементов сложения по модуля два и m регистров, причем входы разрешения записи регистров соединены с инверсным выходом тактового генератора, группы адресных входов блоков памяти соединены с группой выходов коммутатора, входы разрешения записи блоков памяти подключены к входу разрешения записи устройства, группы информационных входов блоков памяти подключены к группе входов задания вида

последовательностей устройства, информационный вход демультиплексора соединен с первыми входами элементов сложения по модулю два и с управляющим входом коммутатора, инверсные входы демультиплексора

соединены с вторыми входами элементов сложения по модулю два группы, выходы которых соединены соответственно с входами разрешения считывания блоков памяти, группы выходов блоков памяти с первого по т-й

5 соединены соответственно с информационными входами регистров с первого по т-й, группы выходов регистров являются группами выходов устройства, группа адресных входов демультиплексора является группой

0 входов выбора устройства.

l Г1 / /то

.-I 1-iIit

дощ Q пшвнви он

пшвноиv

L J° О I .owoggdcoft

м ог-iQomy

1 Г1 / /то

1-iIit

пшаиои org oqisaevd ог-i-y дохпд

I

I i i

л пшвнъи ВУ -ovn адкаеоа едох/чд

-| I

I

., пил

Г I Г -ovgадмем -4 IIt ог-едох/чд

т, ,Л nuiKHDU ВУ

i Ч -окд Dg«/f orf . I / ог-2 дощ

дощ Q пшвнви он

пшвноиv

j L J° О I .owoggdcoft

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования цифровых синхроимпульсов | 1985 |

|

SU1348808A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для анализа случайных сигналов | 1985 |

|

SU1327123A1 |

| Устройство для ввода информации | 1988 |

|

SU1580339A1 |

| Устройство для имитации объекта контроля | 1984 |

|

SU1188743A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

Изобретение относится к вычислительной технике, к устройствам для формирования тестов. Преимущественная область использования - создание аппаратуры тестирования цифровых устройств. Особенностью устройства является то, что оно позволяет многократно - в М + 1 раз - увеличивать количество формируемых тестовых сигналов, что имеет первостепенное значение для создания автоматизированных систем диагностики цифровых устройств. Целью изобретения является расширение технических возможностей за счет многократного увеличения одновременно формируемых различных независимых друг от друга последовательностей цифровых сигналов. По- ставленная цель достигается за счет введения дополнительных блоков 6 памяти, демультиплексора 7, группы 8 элементов сложения по модулю два, регистров 9. 5 ил.

0

/V г-oj

/rf

i1 g пшкиои ОУ

° V- °К

ог-о gcxwp Оifwatfj

jatfei .

0689191

З оЗГб о I

Л

ч

w ft A

ГХ

ГЫГ f

ewoi ri с А //

Ј% iDG XZ DCIIZZf

//

„ LJ LJ Фиг 4

fi i

г , rtz

/Г / f(

ft 01

.тпьг я±/; )c::oDe

fimv/ «w/w 7l -Л-Л- --/ -Ј -ЛfwfO&tffЈ f......11/1/ЈдгжЛ11

faff/ret rtffrttffts

;Ln j i rr::L rL

foxyi/} f..y.,1/y/

)C.jЈ

:cn

frojff o

Фиг 5

Фиг 5

| Патент США № 4404644, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования цифровых синхроимпульсов | 1985 |

|

SU1348808A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-09-07—Публикация

1989-06-14—Подача