Изобретение относится к автоматик и телемеханике, может быть применено для ввода информации от внешних устройств в управляющую микропроцессор нуга систему (МС), реализующую алгоритмы управления и контроля, заданное массивами данных в памяти МС с различным порядком следования входны переменных.

Цель изобретения - расширение функциональных возможностей устройства ввода путем обеспечения программного управления порядком расположения вхоных данных в разрядах входного слова

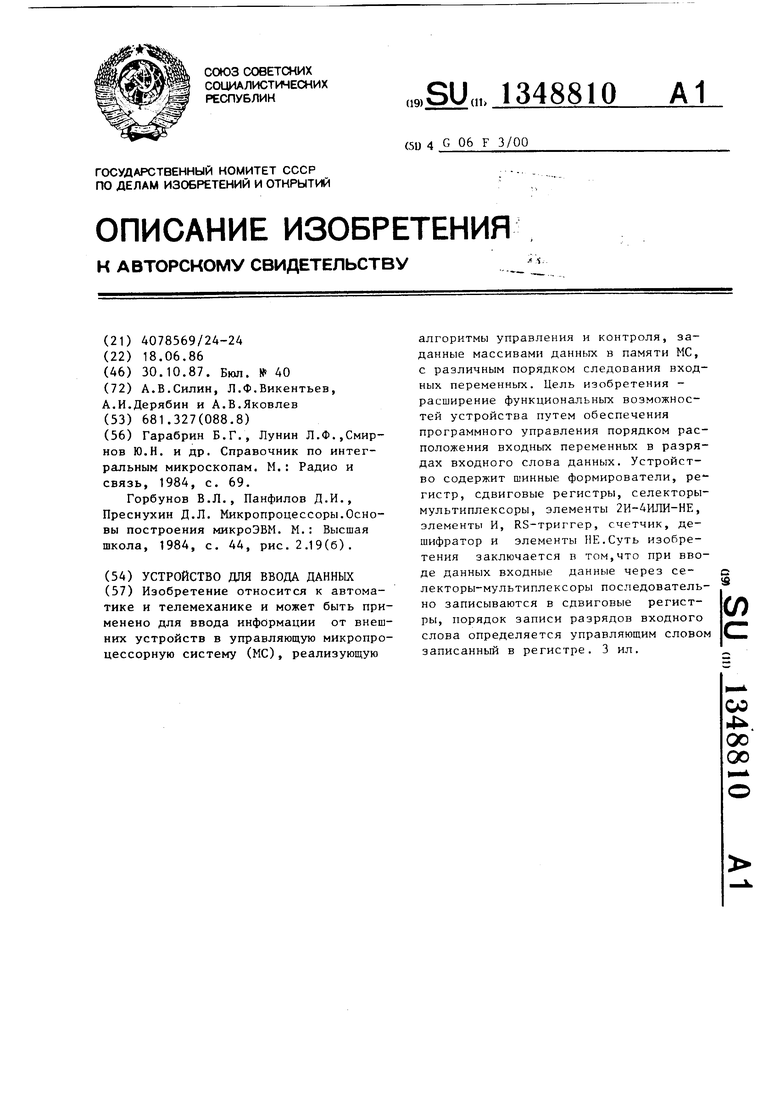

На фиг. 1 показана функциональная схема устройства;на фиг. 2 - вариант схемы подключения предлагаемого устройства к управляющему микропроцессру (типа КР58ИК80А); на фиг. 3 - вре менные диаграммы работы устройства: а) при вводе в устройство управляющего слова, б) при считывании исходных данных в микропроцессор.

Устройство (фиг. 1) содержит ин- формационные входы-выходы 1, управляющие входы 2-8, входы 9,10 данных устройства, шинные формирователи 11, 12, регистр 13, элементы И 14-16, RS-триггер 17, счетчик 18, дешифра- тор 19, злементы НЕ 20-2-, злементы 2И-4ИЛИ-НЕ 25-26, селекторы-мультиплексоры 27-29, регистры 29-30 сдвига.

Устройство 31 ввода через информа ционные входы 1 соединено с соответствующими линиями 32-39 шины данных, которая подключен к нходам D -D,j регистра 40 состояния и входам D -D управляющего микропроцессора 41.Ад- ресные выходы микропроцессора 41 соединеьгы с соответствующими линиями 42-56 шины адреса, линии 52- 56 которой соединены с соответствующими входами дешифратора 57, осу- ществляющего выбор устройства ввода путем подачи соответствующего сигнала на вход 3 устройства 31 ввода. Представленная на схеме упрощенная организация магистрали управления с использованием регистра 40 построена по аналогии с известными схемами формирования магистрали управления. Для управления записью информации в регистр управления устройства 31 ввода пятый выход О регистра 40 состояния подключен к первому входу элемента И 58, второй вход которого через элемент НЕ 59 соединен с выхоЮ

3488102

дом ЗГ1 микропроцессора 41, а выход- с входом 2 устройства 31 ввода и первым входом элемента ИЛИ 60. Для орга- ниазции ввода данн)1х из устройства 31 ввода в микропроцессор 41 седьмой вьгход Q регистра 40 соединен с входом 4 устройства 31 ввода и первым входом элемента И 61, второй вход которого соединен с выходом ПР микропроцессора 41, а вьгход - с вторым входом элемента Ш1И 60. Выход элемента ИЛИ 60 соединен с третим управляющим входо.м дешифратора 57. Для обеспечения cинxpoн oй работы устройства выход Слшхр микропроцессора 41 соединен с входом 5 устройства 31 ввода и ,п-1 входом элемента ИЛИ-НЕ 62, второй вход которого подключен к первому пьгходу Ф генератора 63. а выход - к входу ВК- регистра 40. Для сигнализации о готовности устройства 31 ввода к обмену данных его вьгход 8 соединен с

входом Гот микропргпе1.:сора 4 , Первый и второй- выходы Ф и fT генератора 63 соединены Сч;итветственно с входами Ф и Ф микрон .оцс г 41 и входами 6 и 7 vcTpoMiтва 31 ввода, Входы 9 и 10 гь;1нн; 1х .) йгтва 31 ввода подк.пючаются к сготлетстьу- ющим датчикам об-ьекта л-пг-авления . На пходы R , BK,j, , (, регистра

40через сопротни гг ijnc- R 6-ч ггпдает- ся значение 1.

Работу устройства (фиг. 1) рассмотрим в двух режимах: при вводе в регистр 13 управляющего слова из микропрг-пег гора 41 (фиг. 2) по команде OUT - N и лри считывания информации с нходои /J .м 10 каналов данных на uiHiiy ; aiiFii,ix MUKJIO- пропессора 41 по команде - . N - N (где N - адрес iipe; ;iaraeMor o порта ввода).

С поступлением п микропроцесс:ор

41(фиг. 2) двухбайтной команды OUT К , содержащей адрес выбранного порта внода, микропроцессор начинает ;тработку ттой команды за три машинных цикла . ,n результате выполнения кото)ых ;i;ifinbie (в нашем случае у прав л я и инее слово),, содержащиеся в аккумуп торс микропро- uecc)p;i, должны быть пс)эеданы чероз шину л1анных устропс тлу с аД11еспм N.

В течение парных ,Г;НУ--- циклон , микропроцессор обра:11. к памяти производя выбррку 1. Г;сих Пайтов команды, a в течение третьего цикла М,, содержащего три такта , микропроцессор организует обмен данными с устройством ввода.

Рассмотрим подробное выполнение микропроцессорного цикла М. В течение такта Т микропроцессор А1 выдает на шину адреса адрес N на выход Синхр микропроцессора 41 - си}) хросигнал, а на шину данных слово состояния DQ-D 00001000, которое записывается в регистр 40 на такте

В течение такта Т в соответствии

с выданным адресом на нулевом вмхо- де дешифратора 57 формируется сигнал подготавливающий устройство 31 ввода к работе. Кроме того, в течеине Т и Т микропроцессор 41 осушест- вляет анализ сигнала на входе Гот, значение которого формируется на инверсном выходе RS-трмггера 17 и при взаимодействии устройства 31 ввода с микропроцессором 41 по ко- манде OUT будет равно 1. Единичный сигнал готовности через вход 8 устройства 31 ввода поступает на вход Гот микропроцессора 41, разрешая запись данных из аккумуля- тора микропроцессора 41 в устройспзо 31 ввода на следующем такте работы микропроцессора. I

На такте Т , на выходе ЗП микрс - процессора 41 появляется сигнал, который совместно с единичным сигналом на выходе Q регистра 40 формирует на выходе элемента И 58 единичный сигнал, поступающий через вход 2 устройства 31 ввода на входы УВ шинных формирователей 11,12. Одновременно с этим на такте Т микропроцессор 41 помещает на шине данных вводимые в устройство данные, которые через информационные входы 1 устройства 31 поступают на соответствующие входы B|j-B,j шинных формирователей 11, 12 и далее через соответствующие выходы тех же формирователей на входы регистра 13 (фиг. За записанная в регистр 13 информация определяет порядок расположения входных переменных в слове данных вводимых в микропроцессор 41 с обеих

каналов ввода 9 и 10 данных. После

I дг

; N заканокончания такта Т и обмена данными

выполнение команды OUT чивается.

,

г, г,

с, 0 g Q

5

При считмнли ; ir JH 1л:алии г заданным pacno. n.bf CtuirNi рхолн1 ; иеррмоиных с входов 9 1 10 ка;:а-;с1н уст- poiicTpa М11г:ропп 1цес сир выполняет двухбайтную к ом а и л, у I N N . Выполнение ;г1-ой К11;.ЛИЛ111 r- i схоже с яыиолнс.чисм 1::омл11Л1-1 OUT

i N , потто -:у б(;лео полробно рассмотрим гэакл10ча с;лт. цикл М выполнения соманлм / N N . li течение Т и Т,, ЛИ.ГмЧЛ Ч Л1:Л1СТгл .ими по К : ил1Л .- Л М па ) мпкролроцр с iip;i И- -i. тлреса дан- И1.1Х и и у 1.чл 11 п- j-i - i/vj л - ИфГ . Лгора 57 И1лл1иирук1тс и олл:ч1 nil v. р. шгл сигналы, л н pern, i;i л Л . ынлеч с i слово состоял:;. 0|П(10()10, фор- миру1ошие i,-; 1Л ::-,1Л О р л истра 40 и ьиоде 4 ус i :ii лкл : л 31 сигнал залроса на илформ.гии из уст- рсГк тиа 31. ( i г пг.рлсл и сигнал . и ;-0 icniic такта I ,. чорсз }л-,( л 5 устр .л к тна 31,фор- ми;5у1от Fia рых.у и; : ;ii -ieHT, i И 14 (фиг. 1) е1лл1ич 1 11 сЛ1г; а.л, лсрсволя- 111ИЙ HS--11 И1 )л. р 17 ; . лшл лпюе состоя- Hi t: . На ). и1, :-;,,ц- i риггера 17 плянл.чс 14 я лу-|(л-; , 1 1Л н,), :, лрохо- Л 1;ии;1 I : . : . . /I р. ЛIС Т И а на

i I т 1

I -i;; I , Л : :,Р| Mi. . ор: 1 1

( I l i . 1 1ил кч11 Л; : ,Н 1ЛП-; о.пИДЛ.Л1Я. Оди;);Л;( - :ЛЛ 1 М Л ч 1ЛЛНЛЧИЫ1: сигиз:; с ирнг-: i л ; ь::-л лл триг1Л:ра 17 открывает ч/и- -и/Л Л i И iS и 16, le- рсз которые имп% л1)СЫ тпктопо : частоты Ф и Ф , гф тходягше по пходам f ji 7 устро. с : на , нлчпу поступать COG гнетственно па елп1-лллл:;е С-РХОДЫ рег истрор 29, 30 и с чсть -; С-вход счслчика 1с. IljiH -зт -у -лтл i р.м, что импул1)СЫ Ф, Оудут .ко опережать икпул1лл.; Ф ( фиг, Зб) . Импульсы il,, , поступампцл с :- а СЧ(.-Т11ЛЙ С-вход счетчика 18, формируй i;a его выходах сигналы, инилиир Ы1ци на выхо- ,чах деигифратора и м.чимслнглх 20- 23 соответству1 -)шие сиг лалм, пти сигналы поступав - ;;л с( Г Т 1лл С ГБуютис входы элементов ., 1Я-Иг: и орг-ани- зуют на их выхо;1лх жль трп.е формирование управляющих сигналов н соответствии с парами зпа -ллл и разрядов регистра 13. Пары yriiviB-UHioiKnx сигналов с выходов элементов 25 , 26 , поступая на управляюшиг ;л;г;л -: S,, Sj селекторов-мультиллеь л Лл л 27 , 28 , формируют на выхс ла:-; мтях селекторов и D-входах регистров 29,30 задан51

ную последовательность следования входных переменных. Импульсы с частотой Ф , поступающие через элемент И 15 на сдвиговые входы с регистров 29,30, обеспечивают запись в регистры 29,30 заданной последовательности входных переменных (фиг. Зб).

С поступлением на управляющий вход 7 пятого импульса частотой Ф на выходе пятого элемента НЕ 24 появляется единичный сигнал, обнуляющий триггер 17. При переходе триггера 17 в нулевое состояние закрываются элементы И 15, 16, обнуляется счетчик 18 и через вход 8 устройства выдается единичный сигнал готовности на вход Гот микропроцес ора 41, выводя его из режима ожидания (фиг. 2).

С приходом сигнала готовности мик процессор 41 переходит к заключителному такту в цикле У,, в течение которого значения слова данных, сформированные в регистрах 29,30 через соответствующие входы , и выходы BQ-BJ первого 11 и второго 12 шинных формирователей (фиг.1), вьщаются на информационные входы 1 устройства, шину данных и в микропроцессор (фиг. 2).

Таким образом, устройство ввода данных позволяет микропроцессорной системе осуществлять ввод исходных данных от объектов управления или контроля в виде 24 комбинаций разрядов входных слов данных, в то время как для реализации тех же функций с помощ1 ю устройства-прототипа, необходима либо перекоммута- ция линий связи датчиков объекта управления с входами устройства, либо введение вспомогательных программ, осуществляющих реализацию подобных операций программным способом, что, в свою, очередь, приводит к увеличению времени обработки исходных данных и дополнительным затратам памяти.

Формула изобретения

Устройство для ввода данных, содержащее два шинных формирователя информационные входы-выходы которых

являются информационными входами-вы

д 0

5Q

5 0 5

0

5

106

ходами устройства, входы выбора кристалла шинных формирователей объединены и являются входом выборки устройства, входы - направления передачи шинных формирователей объединены и являются входом записи устройства, отличающееся тем,что, с целью расширения функциональных возможностей устройства за счет программного управления порядком расположения входных данных в разрядах входного слова, в него введены регистр, два селектора-мультиплексора, два сдвиговых регистра, два элемента 2И-4ИЛИ-НЕ, три элемента И, RS- триггер, счетчик, дешифратор и элементы НЕ, причем информационные выходы шинных формирователей соединены с информационными входами регистра, информационные входы шинных формирователей соединены с выходами сдвиговых регистров, информационные входы селекторов-мультиплексоров являются информационными входами устройства, выходы селекторов-мультиплексоров соединены с информационными входами сдвиговых регистров, одноименньге управляющие входы селекторов мультиплексоров объединены и подключены к выходам элементов 2И-4ИЛИ-НЕ,входы первого элемента И являются соответственно входом чтения и стробирующим входом устройства, а выход первого элемента И соединен с S-входом RS- триггера, прямой выход которого соединен с одними входами второго и третьего элементов И, другие входы которых являются тактовыми входами устройства, выход второго элемента И соединен с синхровходами сдвиговых регистров, а выход третьего элемента И соединен с синхровходом счетчика, инверсный выход RS-триггера Соединен с входом сброса счетчика и является выходом готовности устройства, выходы счетчика подключены к входам дешифратора, вкоды которого соединены с входами элементов НЕ, одни входы элементов И элементов 2И-4НЛИ-НЕ соединены с выходами регистра, а другие входы элементов И каждого элемента 2И-4МИ-НЕ соединены с выходами первых четырех элементов НЕ, выход пятого элемента НЕ подключен к R-нходу RS-триггера.

-- i I }

m:bdv

flii li

-Т

Srrr :;:rzt i-г- „ J Г

I :::T- -. i J

-- ,..., i iLiikill

.-.;:;:.;. ;.:-J jp: Л .i .-pn-v, J Jr|lJ

-- - :- ; T p:±4iViF

; I 1TT1-Г

- .i i

-1. k|::; r

.;-...- - .

f: -::i::1i i -

ff.-i

-.|7Л

KV

to.-

-БрТд п Д4 | ь;-

Liikill

г

г..

-t . }к V-JrfJ

jitj;-

::.u

,С«А ,

Pfln

9j

UHirl

np9n.tn4

T17 t Инв.вых ТП

Рь л-. I

H1$ - Вых. t HIS Вьух. f

Э/1.НЕ20

Вы)с. за. HE 21

Вых. y.Hfzi

.

/.// 23

fffc X.

за. и 24 .25

Si y.

8u;x. 2)eiyr29,JO

бых J}i3A. 29,30

fib/x. Da J/i- 23,5(

fil X. Jj 9.29,30

В X.I

Bx.l

Bx Bp-Bj 3/1.11,12

, 3/7. ff/

Bbix., 3/}. 2930

U23

n

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления каналами ввода-вывода | 1982 |

|

SU1086422A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Канальный кодек | 1990 |

|

SU1798922A1 |

| Процессор для мультипроцессорной системы | 1987 |

|

SU1517035A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

Изобретение относится к автоматике и телемеханике и может быть применено для ввода информации от внешних устройств в управляющую микропроцессорную систему (МС), реализующую алгоритмы управления и контроля, заданные массивами данных в памяти МС, с различным порядком следования входных переменных. Цель изобретения - расширение функциональных возможностей устройства путем обеспечения программного управления порядком расположения входньк переменных в разрядах входного слова данных. Устройство содержит шинные формирователи, регистр, сдвиговые регистры, селекторы- мультиплексоры, элементы 2И-4РШИ-НЕ, элементы И, RS-триггер, счетчик, дешифратор и элементы НЕ.Суть изобретения заключается в том,что при вводе данных входные данные через селекторы-мультиплексоры последовательно записываются в сдвиговые регистры, порядок записи разрядов входного слова определяется управляющим словом записанный в регистре. 3 ил. i (Л со 4. 00 00

Составитель A.Женин Редактор Н.Слобоцяник Техред М.Ходанич

Заказ 5190/47Тираж 670Подписное

ВНРМПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор В.Бутяга

| Гарабрин Б.Г., Лунин Л.Ф.,Смирнов Ю.Н | |||

| и др | |||

| Справочник по интегральным микроскопам | |||

| М.: Радио и связь, 1984, с | |||

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| Горбунов В.Л., Панфилов Д.И., Преснухин Д.Л | |||

| Микропроцессоры.Основы построения микроэвм | |||

| М.: Высшая школа, 1984, с | |||

| Приспособление для плетения проволочного каркаса для железобетонных пустотелых камней | 1920 |

|

SU44A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-10-30—Публикация

1986-06-18—Подача