1

(1Г.( OlHOCHTcn к МЧИГ.1ТИт 1ЫЬ й технике ;UIH (ii i оГфаПот ivii 44Mi( iui4Hr)inn IX тоПрпже.иш и можот fii.i i i. ii(,4(inano Д.пп 1И)С гр( опе pnTiuiHiMX : anoMiinaioiuMx устройств ОЗУ систем оfiijafxTTKH лидо()1пи|юрмаиии .

Це. п. и.чобретеиии - pncpinpoiiiic фуик1и1ОН;1Л1,ных (i3Momn( ycTimii- с тна за счет оргагшчации трс хсторон- неп) чПмона ииформацие1(.

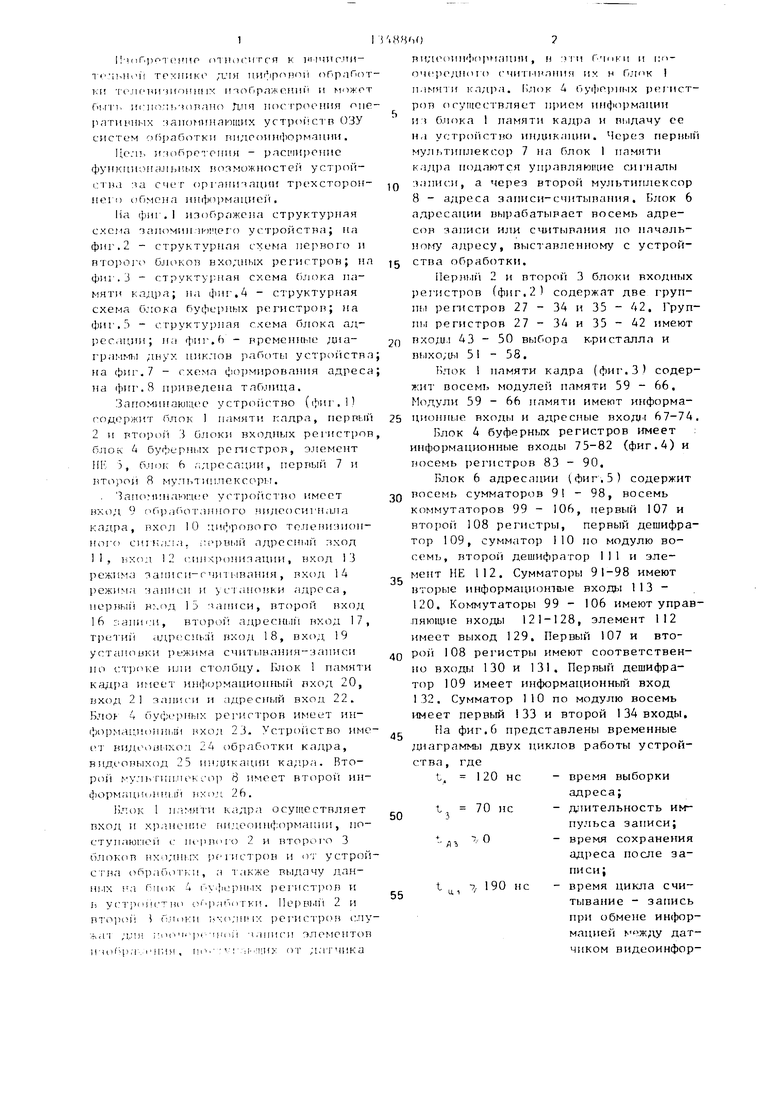

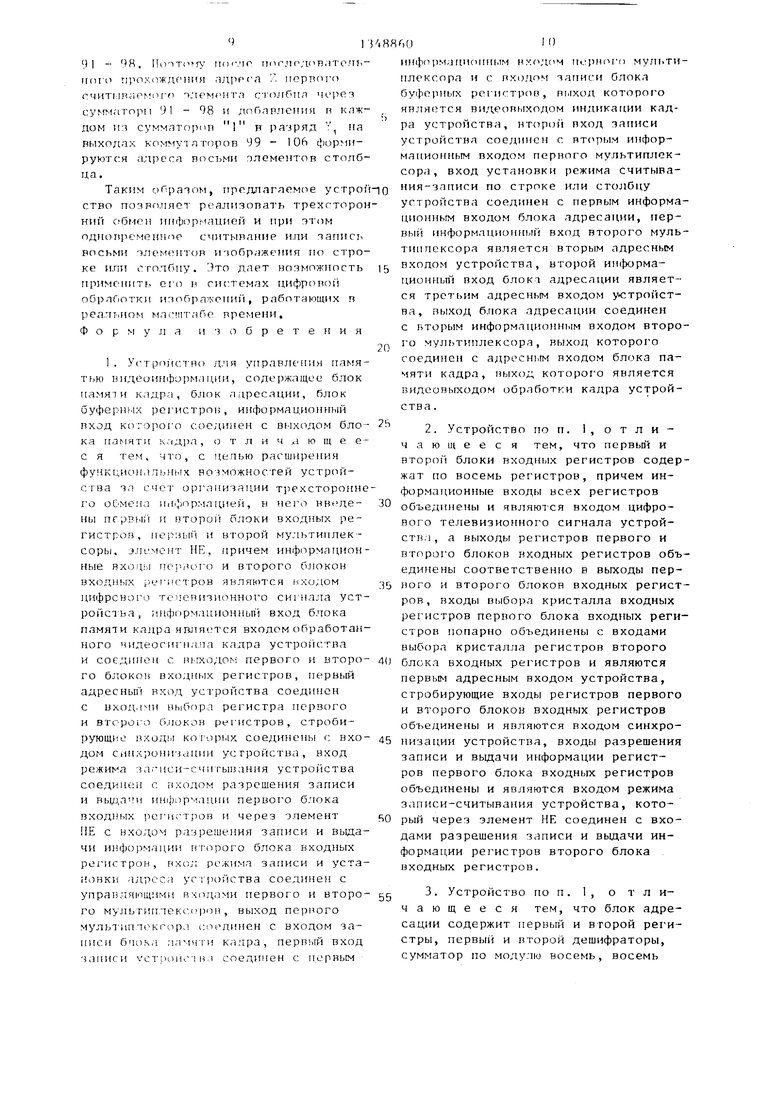

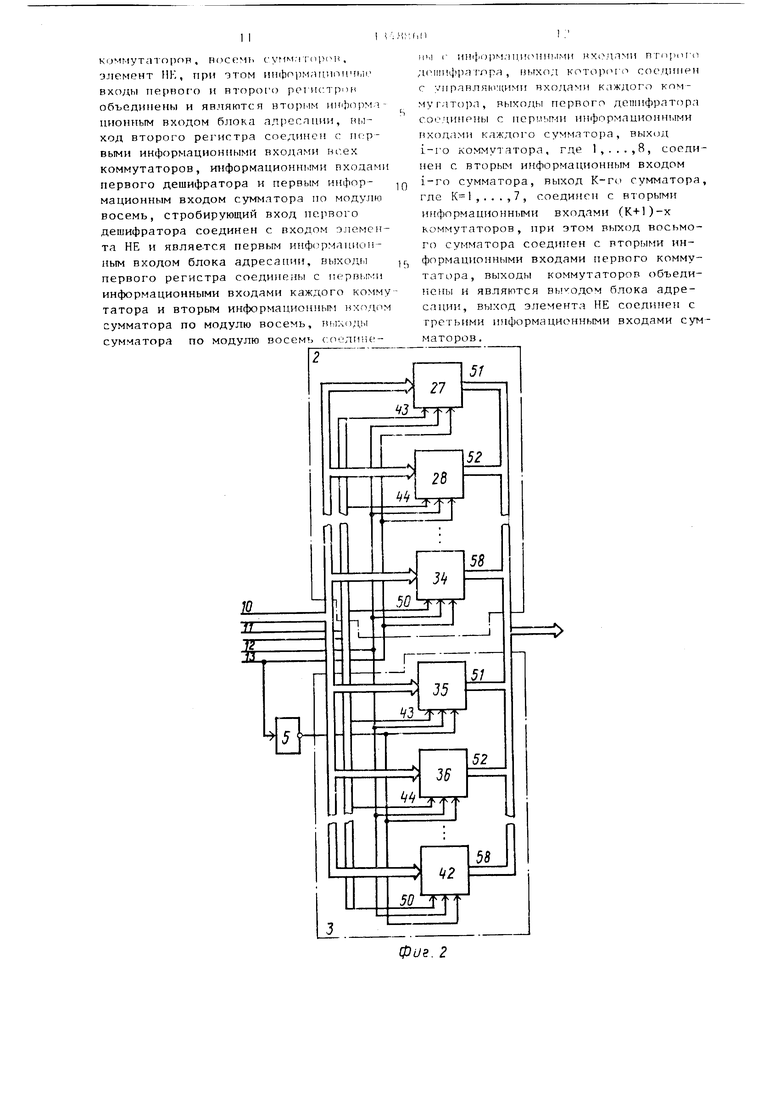

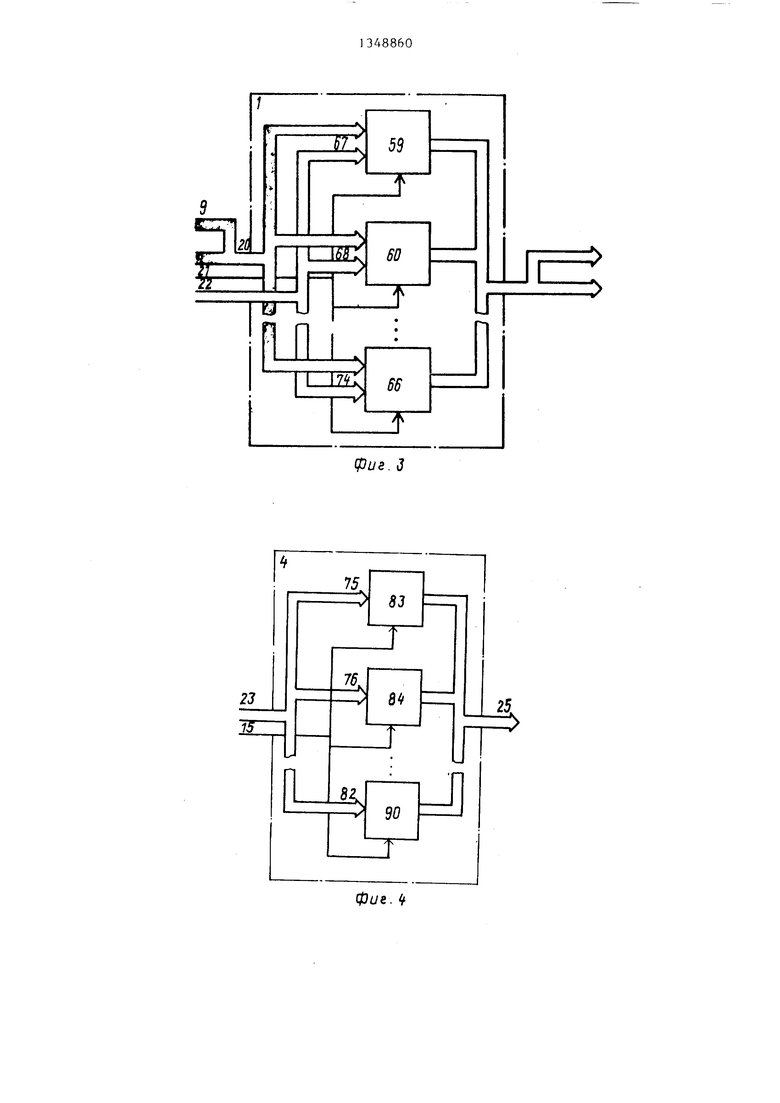

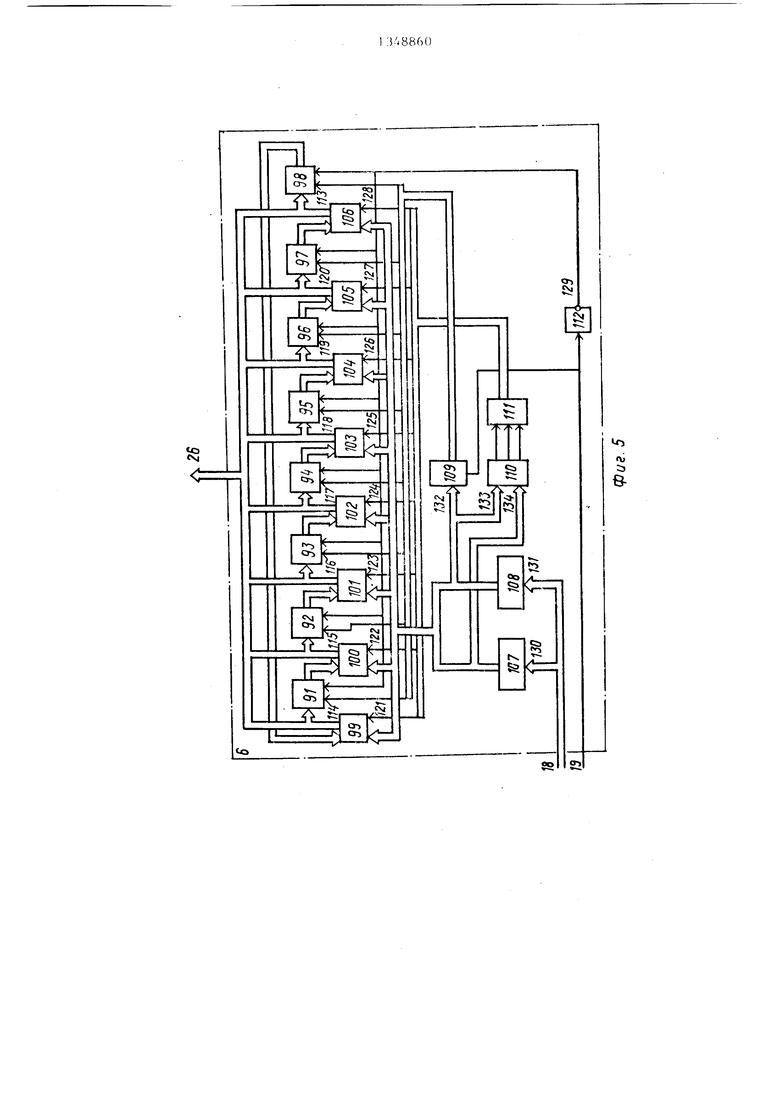

На (1)иг.1 игзоГфпжеиа структурная схена за11оми11,)р)1п,ег о устройства; на фиг.2 - структурная схема первого и пторогс GjioKon BXo;i,Hhix регистров; на фиг. 3 - структурная схема блока памяти клдра; на фиг,4 - структурная схема блока буферных регистроп; на фиг.З - сгрукту1)ная схема блока адресации; на (.b временные диа- rpaMMiii двух циклов работь ycTpoiicTBa на ()иг.7 - схема формирования адреса на (} 1иг.8 приведена таблица.

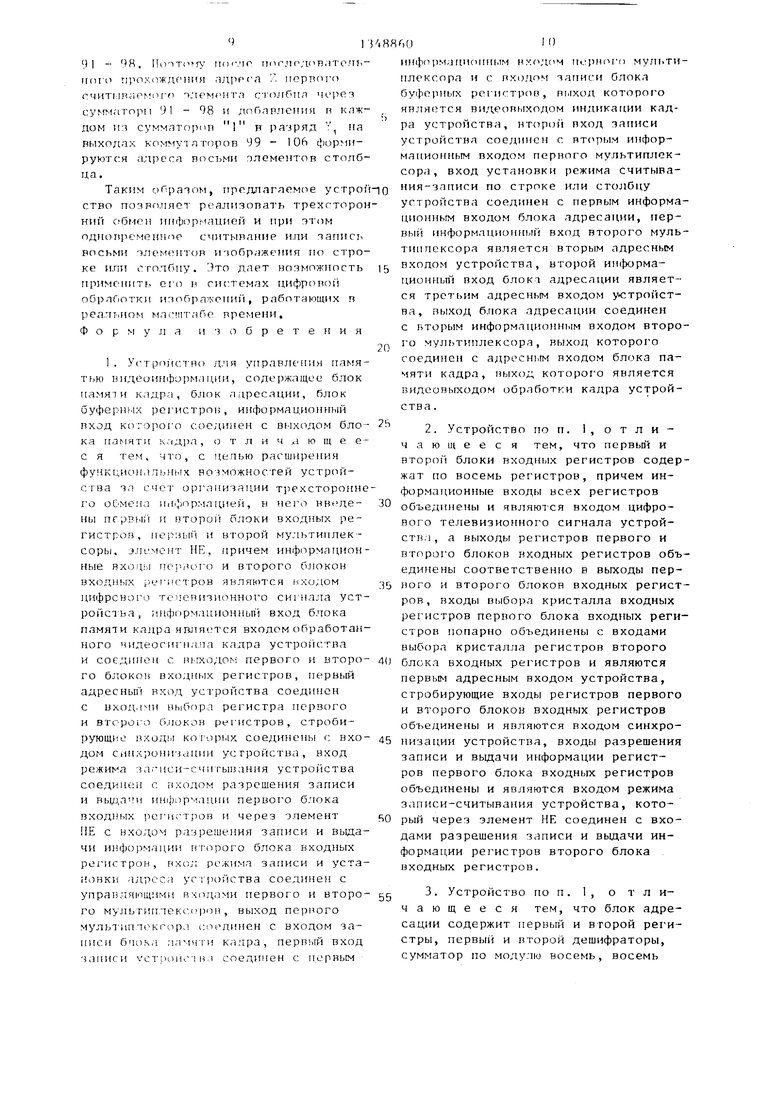

Заноминаю1цее ycTpc iicTHO (фиг.П сод(ржит блок 1 памяти 1;адра, nepBbii i 2 и pTopoi i 3 блоки вх(7дных регистров блок и буферных pcnicTpon, элемент 111 3, блок- 6 адресации, первый 7 и liTopoi) 8 му.чыкплексорм.

Запомииаюгдее )i iCTHo имеет нход 9 с бработаииогс нид.ес) кадра, вход 10 цифрового трлепизион- ного ci .rH,-.:ia. iu pBi.ii i адресный зход 1 i, нхол 12 сипхронизадии, вход 13 режима записи-считывания, вход 14 режима запИ|.;и и }, стаповки адреса, первый вход 15 записи, второй вход 16 :1апи1:и, второй адресН1Л1 1 вход 17, трети) адресньп вход 18, вход 19 у cTiin TUKH режима считывай ий-записи но cTjKiKe или ст о.пбцу. Елок 1 намяти Kaj-ipa имеет инф(-)рмационны11 пход 20, 21 записи и адресный вхоц 22. Бло 4 6y( ;i pnhix регистров имеет ии- (})орма1 иопи1 Б1 нход 23. УстроГютво име- (т вид1М1П-1хо;1 24 обработки кадра, видеот ыход 25 и1Ь 01кацни ка;фа. Вто- poii му:1)1тип.пекv op 6 имеет BTopoii ин- формади Л1 1лй вход 26.

1 осуществляет вход и хра.непме пидеон)1формапии, по- ступаю1;1е1 1 с пер пего 2 и второг О 3 б.ттков входных регистров и от устройства обработки, а также выдачу дан- iiMX на б1|(1к 4 i V liepHhix регистров и I-, у ст кчн-тщ о1 р;|Г1(1тки. lle :iBbii i 2 и второй блики i xo;пl lx регистров слу- .т,а 1 д, KiMTi pi niMii ч.шиси элементов H3ofM a I lr.iM , псм i:;- ;|,, от датчика

; ;

,

5

) tH8 i()

вмдеоип Ьормадии, в ;п м бчпки и Н - очередного считмвания их н блпк I пами ги 1сад11а. ..пок 4 буферн.1Х регистров осуществляет прием ир|форманин из блока 1 ттамяти кадра и П1 1дачу се и,) устройство индикации. Через первый мультиплексор 7 на блок 1 намяти кад1)а подаются управляющие сигналы Q записн, а через второй мультиплексор 8 - адреса записи-считывания. 6 адресанни вырабатывает восемь адресов записи или (1вания но начоль- Horfy адресу, выставленному с устрой- 15 стпа обраб(5тк11.

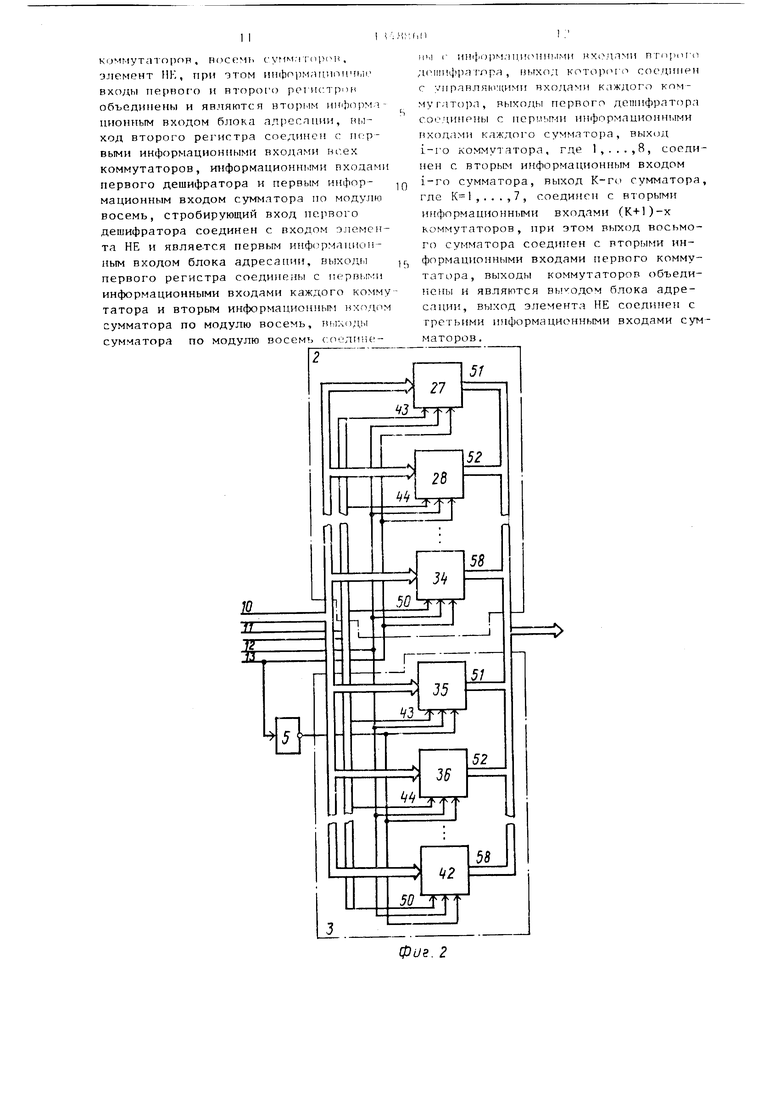

ilepBbiii 2 и второй 3 блоки входных регистров (фиг,2) содержат две груп- п(,1 решстров 27 - 34 и 35 - 42, Группы регистров 27 - 34 и 35 - 42 имеют 20 вхо;и,1 43-50 выбора к.ристаплл и выхо;ц11 51 - 58.

Клок 1 намяти кадра (фиг.З) содержит восемь модулей памяти 59 - 66. Модули 59 - 66 намяти имеют информа- 25 иио1П1ые входы и адресные вход|.1 67-74. Блок 4 буферных регистров имеет ; информационные входы 75-82 (фиг.4) и восемь регистров 83 - 90.

Блок 6 адресации (фиг.5) содержит 20 восемь сумматоров 91 - 98, восемь коммутаторов 99 - 106, первый 107 и второй 108 регистры, первый дешифратор 109, сумматор ПО по модулю восемь, BTopoi i дешифратор 111 и элемент НЕ 112. Сумматоры 91-98 имеют вторые информационные входы 113 - 120. Коммутаторы 99 - 106 имеют управ- ляю1ц)1е входы 121-128, элемент 112 имеет выход 129. Первый 107 и вто- д poii 108 регистры имеют соответственно входы 130 и 131. Первый дешифратор 109 имеет информационный вход 132. Сумматор 110 по модулю восемь имеет первый 133 и второй 134 входы, Па фиг.6 представлены временные

35

45

50

55

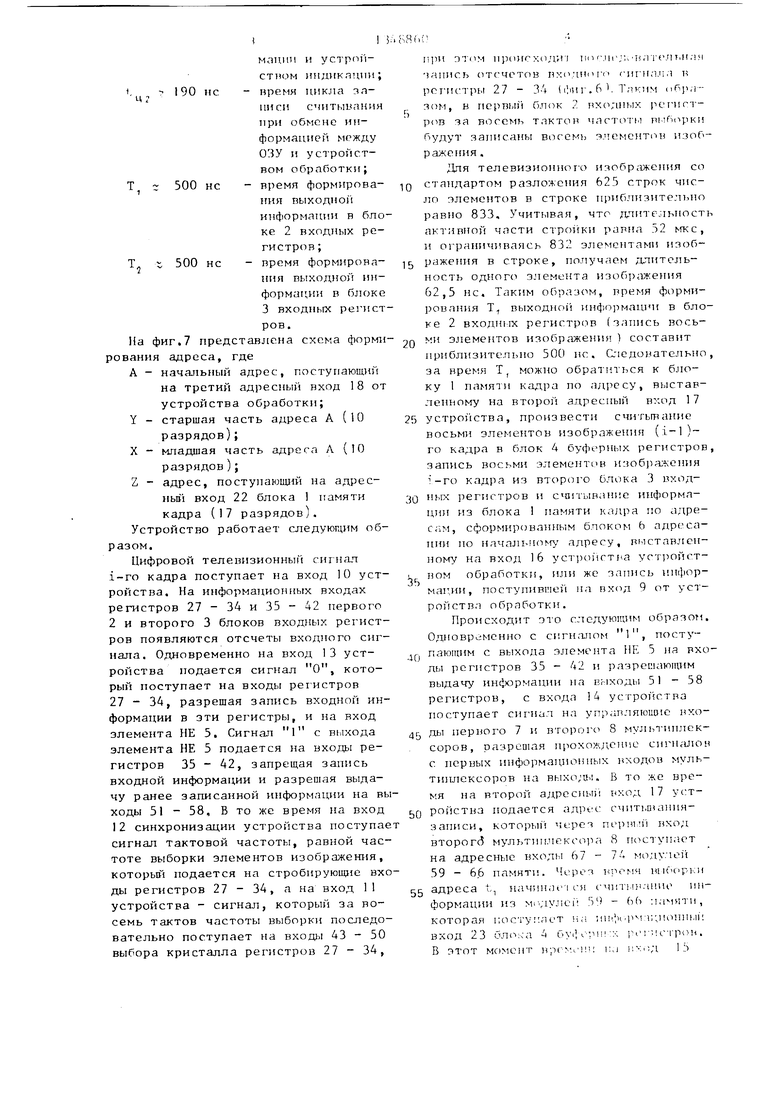

;ц1аграммы двух циклов работы устройства, где

t, 120 НС - время выборки адреса;

t 70 НС - днительность импульса записи;

1д, 70 - время сохранения адреса после записи;

t ц 7/ 190 НС - время цикла считывание - запись при обмене информацией .жду датчиком видеоинфорц:

мании и устрои- стном иядикл иш; 190 ис - нремя цикла зл- ииси считывания при обмене информацией между ОЗУ и устройством обработки;

Т 500 НС - время формирования ВЫХОДНОГ

информации в блоке 2 входных регистров ;

Т 500 НС - время формирования выходной информации в блоке 3 входных регистров.

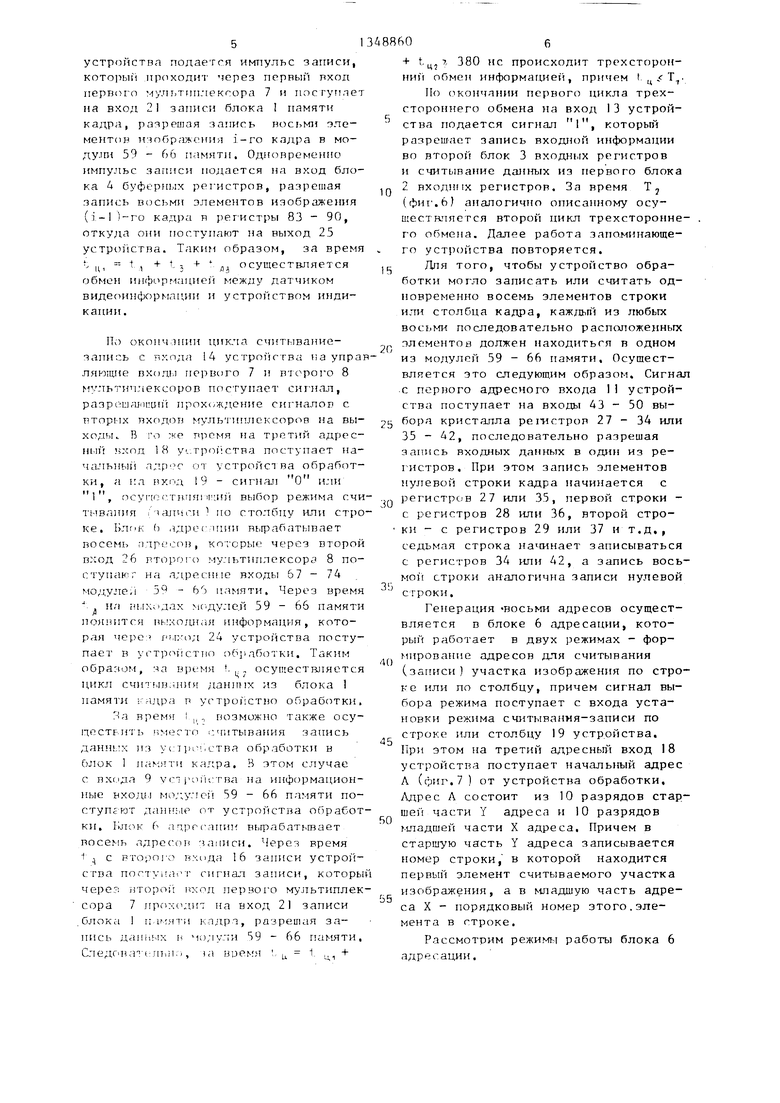

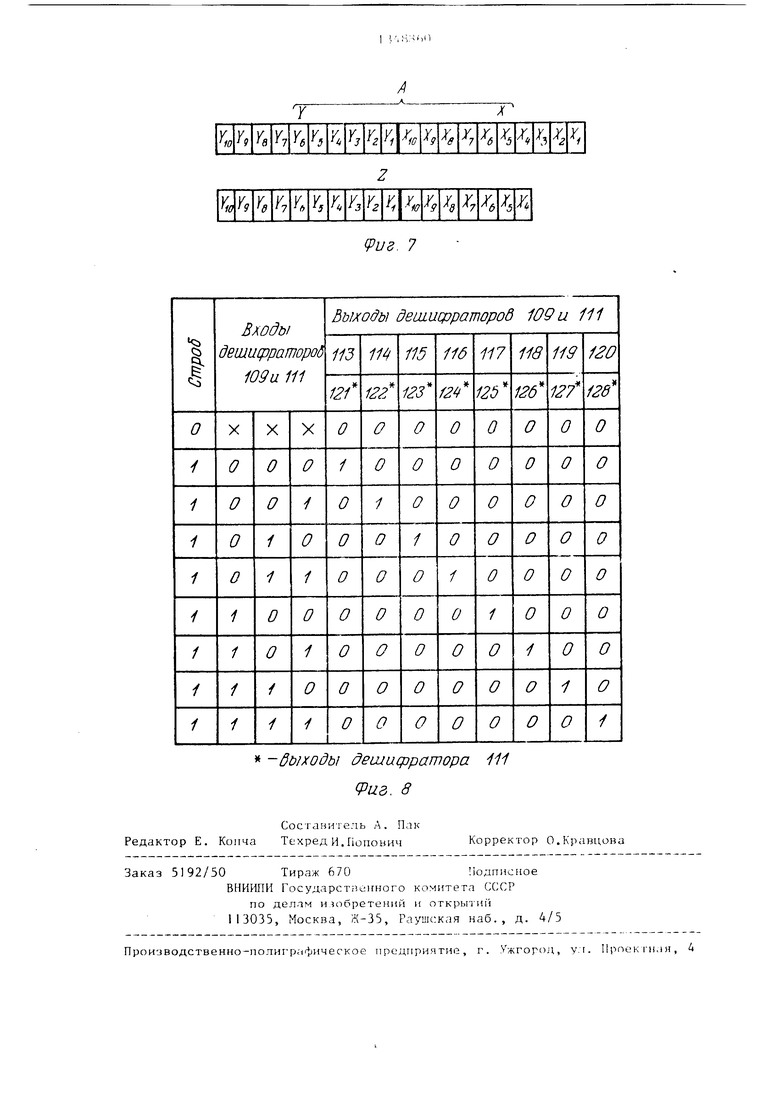

На фиг.7 представлена схема формирования адреса, где

А - начальный адрес, поступающий на третий адресный вход 18 от устройства обработки; Y - старшая часть адреса А (10

разрядов); X - младшая часть адреса А (10

разрядов);

Z - адрес, поступающий на адрес- Hbrii вход 22 блока 1 памяти кадра (17 разрядов). Устройство работает следуюгдим образом.

Цифровой телевизионный сигнал i-ro кадра поступает на вход 10 устройства. На информационных входах регистров 27 - 34 и 35 - 42 первого 2 и второго 3 блоков входных регистров появляются отсчеты входного сигнала. Одновременно на вход 13 устройства подается сигнал О, который поступает на входы рег истров 27 - 34, разрешая запись входной информации в эти регистры, и на вход элемента НЕ 5. Сигнал 1 с выхода элемента НЕ 5 подается на входы регистров 35 - 42, запрещая запись входной информации и разрешая выдачу ранее записанной информации на выходы 51-58, В то же время на вход 12 синхронизации устройства поступае сигнал тактовой частоты, равной частоте выборки элементов изображения, который подается на стробирующие входы регистров 27-34, а на вход 11 устройства - сигнал, который за восемь тактов частоты выборки последовательно поступает на входы 43 - 50 выбора кристалла регистров 27 - 34,

5

0

5

0

5

О

5

О

5

1П И ЭТ(1М пр(1нсх(1д;г1 пи r-ju-;;, ,н;,ч чапись отсчетов входингс сиг нп.чл и регистры 27 - 34 (iliMr.6V Тяким образом, в Г1ерв1лй блок 2 tix(i;Liibix рст пгт- за восемь тактов частотн. п1.Порки будут записаны восемь элементов изображения .

Для телевизионног о изобр;1жения со стандартом разложения 625 строк число элементов в строке приб-чизителтлю равно 833, Учитывая, что длительность активной части стро11ки равна 52 мкс, и ограничиваясь 832 элементами изображения в строке, получаем д.литель- ность одного элемента изобр;1жения 62,5 НС. Таким образ(1м, время формирования Т, выходно информащ и в блоке 2 входных регистрств (запись восьми элементов изображении 1 составит приблизительно 500 не. Следовательно, за время Т можно обратиться к блоку 1 памяти кадра по адресу, выстав- лешчому на второй адресный вход 17 ycTpoiicTBa, произвести считывание восьми элементов изображения (i-l)- го кадра в блок 4 буферных регистров, запись восьми элементов и;юбра;-кения 1-го кадра из второго блока 3 входных 1егистров и с пп ывание информации из блока 1 памяти кадра ио адресам, сформированным блоком 6 адресации но начальиот адресу, piiicTaBjieH- ному на вход 16 ycTpoiicTjia устройством обработки, или же запись инфор- мап.ии, поступившей на вход 9 от устройства обработки.

Происходит это следующим образом. OiyioBpiiMCHHO с сигналом 1, поступающим с выхода элемента НЕ 5 на входы регистров 35 - 42 и разрешающим выдачу информации на выходы 51 - 58 регистров, с входа 14 устройства постунает сигнал на упрапляюио1е входы первого 7 и второгс 8 мультиплексоров, разрешая нрохождеиче с нервых информационных нходон мультиплексоров на выхо;цл. В то же время на второй адресньг иход 17 устройства подается адрес: счит1,п(анця- записи, которьп через первьп вход BTopord мультиплексора 8 гк ступает на адресные входы Ь7 - 74 модуле 59 - 66 памяти. Через нремя nnt 4ipi:ii адреса t;, начинав гя с-чит1.1)1апио ип- формащн из мг.дулсГ; S9 - ЬЬ па-чити, которая поступает на ,H p -ri;;i onn,ir. вход 23 4 Ovt , i- pii: :х U гисч рои. В этот момент нр(л-. 1М |: -:од 13

устр(.1Йствл подается импульс записи, KOTopbii i ПРС1ХОДИТ через первый лход первого му.П1)ТП11:1ексора 7 и посгуплет на вход 21 записи блока I памяти кадра, разрешая запись восьми эде- ментов пзобр;1дспия i-ro кадра в модули 59 - 66 памяти, Одиовремепко импульс записи иодается на вход блока А буферных регистров, разрешая запись В(зсьми элементов изображения (J-I )-го кадра я рег истры 83 90, откуда опи поступают на выход 25 устройства. Таким образом, за время о ц, t , + t, + л осуществляется обмен информацией между датчиком видеоинформации и устройством инди- капии.

По окончании пикча считывание- запись с входа 14 устро11ггв 1 па управ ПХОД1Л первого 7 и второго 8 мульти ъчексоров поступает сигнал, разрГ Шгииццп прох(/ждепие сигналов с птормх пходоп муль 1 иплексороо на вы- ходы в го ;ке премя на третий адг)ес- Н1,1Й нход 18 У ,1трог.ства поступает начальный адрес от ycтpoйc ва обработки, а на 19 - сигнал О или 1, осупгмггнп. п 11 ;ий выбор режима считывания i китисп но столбцу или строке, Блг К ( лдрегппии вырабатывает восемь nnpt i oB, которые через второй в:сод 26 второго мультиплексора 8 по- cTyiuiKjr на ад.реснпе входы 57 74

модуле, . на

SQ J

65 памяти. Через время

t, 1,, осуществляется c4mhiH:un H данных из блока 1

выходах мс дулей 59-66 памяти появится выходная информация, которая чере: рьпгод 24 устройства поступает в уcTpcifiCTiio об)аботки. Таким образом, за время цикл

памяти ; .-1дра Р устройст}К) обработки, ла время I ,, , возможно также осу- iTOCTFHTb вмегто ::читываиия запись данных 1ТЗ ycTpi-i .ства обработки н блок 1 п;1М,чти кадра, В этом случае с вх(.|да 9 УС го1 и:тва на ипформацион- ные входы мо;;уле 59 - 66 памяти по- дашгые от устройства обработки. Кл ок 6 лцррсапии вырабатьшает восемь адресов г аниси. Через время 1 :| с BTOpoi o входа 16 записи устройства погту1 а.т сигнал записи, которы через HTopoii вход первого мультиплексора 7 прохс дит на вход 21 записи блока 1 II кпдрт, разрешая запись данных н модули 59 - 66 памяти, Следг1ва -(:лт,11;), la Биеь,ч , ц 1, , +

48860

+ t

10

1й

40

45

50

35

ш

380 НС происходит трехсторонниГг обмен информагщб, причем ц/Т.

По (1кончании первого цикла трехстороннего обмена на вход 13 устройства подается сигнал 1, которьй разрешает запись входной информации во второй блок 3 входных регистров и считывание данных из первого блока 2 входных регистров. За время Tj (фиг.6) аналогично описанному осу- шесталяется второй цикл трехстороннего обмена. Далее работа запо.минающе- го устройства повторяется.

Для того, чтобы устройство обработки могло записать или считать одновременно восемь элементов строки или столбца кадра, каждьй из любых восьми последовательно расположенных элементов должен находиться в одном из модулей 59 - 66 памяти. Осушест- вляется это следующим образом. Сигнал с первого адресчого входа 1I устройства поступает на входы 43 - 50 выбора кристалла ретстров 27 - 34 или 35 - 42, последовательно разрешая запись входных данных в один из регистров. При этом запись элементов нулевой строки кадра начинается с регистров 27 или 35, первой строки - с регистров 28 или 36, второй строки - с регистров 29 или 37 и т.д. , седьмая строка начинает записываться с регистров 34 или 42, а запись вось- Moii строки аналогична записи нулевой строки.

Генерация -восьми адресов осуществляется в блоке 6 адресации, который работает в двух режимах - формирование адресов для считывания (записи ) участка изображения по строке или по столбцу, причем сигнал выбора режима поступает с входа установки режима считывания-записи по строке или столбцу 19 устройства. При этом на третий адресный вход 18 устройства поступает начальный адрес Л (фиг.7 ) от устройства обработки, Л состоит из 10 разрядов старшей части Y адреса и 10 разрядов младшей части X адреса. Причем в старшую часть Y адреса записывается номер строки, в которой находится первый элемент считываемого участка изображения, а в младшую часть адреса X - порядковый номер этого.элемента в строке.

Рассмотрим режимы работы блока 6 адресации.

Формирование адресо}) счгггыпл- пия {записи) по стр(же.

С ихода 19 устройства на строби- рующи вход первого дешифратора 109 и вход элемента НЕ 112 поступает сигнал I. Сигнал t разрешает работу первого дешифратора 109. Си:- нал О с выхода элемента НЕ 112 подается на третьи входы сумматоров 91 - 98, Младшая часть X адреса поступает на вход 130 первого регистра 107, а старшая часть У адреса - на вход 131 второго регистра 108, С выхода первого регистра 107 семь старших разрядов

(4 младп еи части X адреса поступают на первые входы коммутаторов 99 - 106, а три младших разряда (Х - Xj) - на второй вход 134 сумматора 110 по модулю восемь. С выхода второго регистра 108 старшая часть Y адреса поступает на первые входы коммутаторов 99 - 106, причем три младших разряда (У - У.) подаются на информационный вход 132 первого дешифратора 109 и первый вход 133 сумматора 110 по модулю восемь. Таким образом, на первых входах коммутаторов 99 - 106 будет сформирован адрес Z (17 разрядов), который в дальнейшем используется для адресации блока 1 памяти кадра.

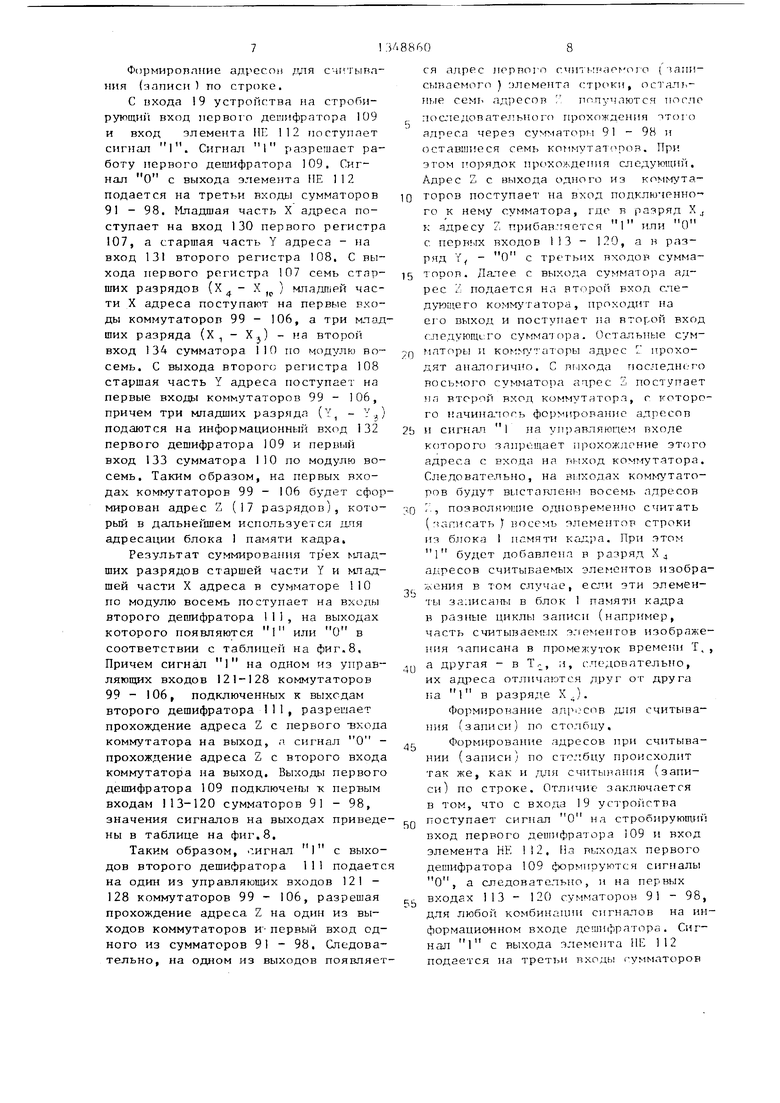

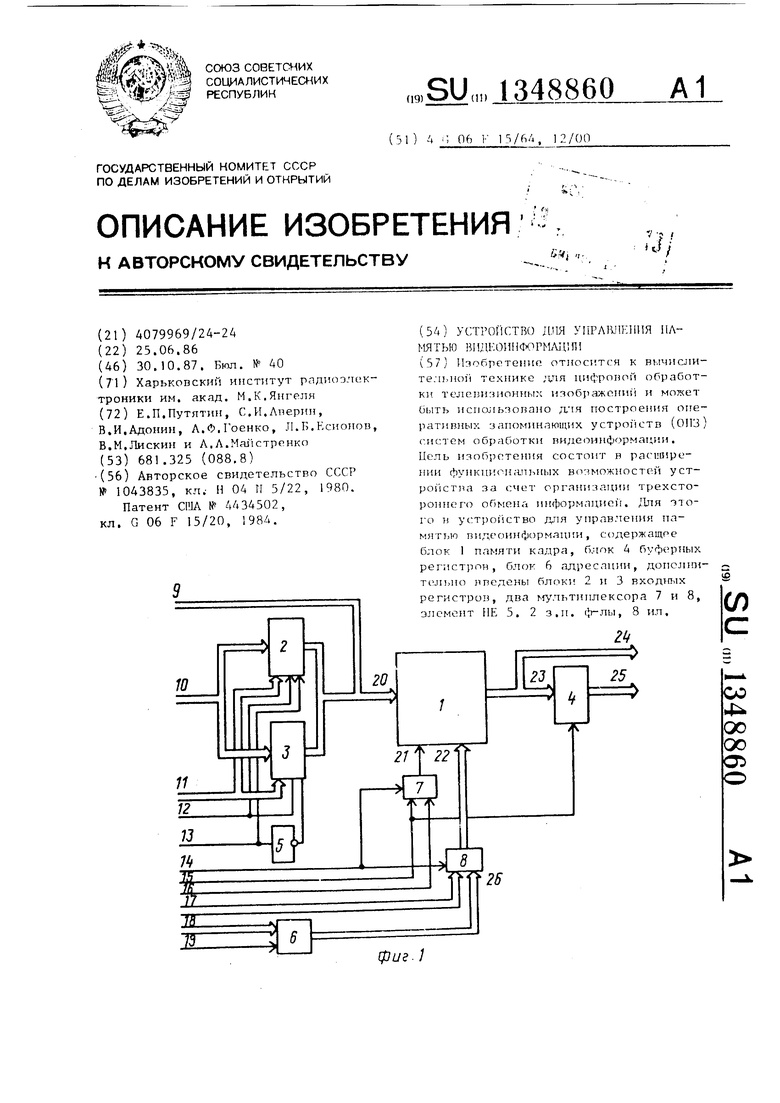

Результат суммирования тр ех младших разрядов старшей части У и младшей части X адреса в сумматоре 110 по модулю восемь поступает на входы второго дешифратора 111, на выходах которого появляются 1 или О в соответствии с таблицей на фиг.8, Причем сигнал 1 на одном из управляющих входов 121-128 коммутаторов 99 - 106, подключенных к выходам второго дешифратора 111, разрешает прохождение адреса Z с первого входа коммутатора на выход, а сигнал О - прохождение адреса Z с второго входа коммутатора на выход. Выходы первого дешифратора 109 подключены к первым входам 113-120 сумматоров 91 - 98, значения сигналов на выходах приведены в таблице на фиг.8.

Таким образом, сигнал l с выходов второго дешифратора 111 подаетс на один из управляюш 1х входов 121 - 128 коммутаторов 99 - 106, разрешая прохождение адреса Z на один из выходов коммутаторов и первый вход одного из сумматоров 91 - 98. Следовательно, на одном из выходов появляет

ся адрес перпогп о (чапи- сынаемого } элемента строки, остальные семь ад11есоп / получаются тюгле последовательного прохождения ттого адреса череа сумматоры 91 - 9В и (5ставшиеся семь копмутатор(1в. При этом тторядок прс. хождения следующий. Адрес Z с выхода одного из торов поступает на вход подключенное го к нему сумматора, где в разряд Xj

Ь

Ь

М 1 II

К адресу /. прибавляется 1 или О с первых входов 113 - 120, а н разряд У - о с третьих входов сумма- 1орол. Далее с выхода сумматора адрес Z подается на второй вход следующего комм татора, проходит на его выход и поступает на второй вход следующего сумматора. Остальные сумматоры и ком -г/т-аторы адрес L проходят аналогично, С лг,|хода последнего восьмого сумматора ацрес Z поступает ил второй вход коммутатора, с которого начиналось формирование адресов и сигнап 1 на управляющем входе которого запрещает прохождение этого адреса с входа на вмход коммутатора. Следовательно, на В1лходах коммутаторов будут выстагшенм восемь адресов ., позволяющие одновреме1П{о считать (г аписать J восемь элементов строки из блока I памяти Kajvpa, При .этом 1 будет добавлена в разряд Х4 адресов считываемых элементов изобра- -/кения в том случае, если эти элементы залисаш. в блок 1 памяти кадра в разньте циклы записи (например, часть считываем :.1Х э.чементов изображения записана в промежуток времени Т, ,

40

а другая - в

Т.

следовательно,

5

0

Ь

их адреса отличаются друг от друга па 1 в разряде Х).

Формирование адр1}спв д;1я считывания (записи) по столбцу.

Формирование адресов при считывании (записи) по столбцу происходит так же, как и для считывания (записи) по строке. Отличие заключается в том, что с входа 19 устройства поступает сигнал О на стробирующий вход первого дешифратора 109 и вход элемента НЕ 112, На выходах первого дешифратора 109 формируются сигналы О, а следовательно, и на первых входах 113 - 120 сумматоров 91 - 98, для любой комбинации сигналов на информационном входе дешифратора. Сигнал 1 с выхода элемента НЕ 112 подается на третьи входы гумматоров

91 - 98. Поптшгу гкх-.чо ппглрдоплтоль- ппго прохождении пдррсл Z irepnoi o ГЧИТ1 ip;;pN or4i тлрМ(М1т,т стсигбил чс рез

сумма гори

98

кпж- на

дпблплеиия п

дом из суммлторпп I в ря зряд , выходах комму л торов 99 - 106 формируются адреса восьми племеитое столбца.

Таким образом, предлагаемое устроило ния-злписи по строке иди столбцу

устройства соединен с первым информационным входом блока адресации, перство позволяет реализовать трехсторонний информацией и при этом

одноу ремеинпе считьтание иди запис, восьми 3JipMeHT(jB изображения по строке или столбцу. Зто дает возможность применить ei o в системах цифрово обработки изображр1П Й, работающих п реалт.ном масштабе времени. Формула изобретения

1. ycTpoiicTfU) для управлс ния тью видeoинфop,luни, содержащее блок памяти кадра, блок адресации, блок буферных регистров, информационный пход когорого соединен с В л1ходом бло ка памяти кадра, (З т л и ч ,а ю щ е е- с я тем, что, с цепью расширения функциональных возможностей устрой- С1ва зп счет организации трехстороннего оС Мепа информацией, н него введе- ны nrppf-ii i и tJTopoi блоки входных регистров, нерньп и второй мультипдек- соры. элемент НЕ, причем информационные вхоцг-л пер. К ГО и второго блоков

входных е1 ИСТрОВ ЯВЛЯМТСЯ 1ХОДОМ

цифрсвого тех евизионного сигнала уст- poAcibaj и}1формационньп) вход блока памяти кадра является входом обработанного чидеосигна.па кадра устрО11Ства и соединен с первого и второ- го блоков вх 5дных регистров, первый адресный вход устройства соединен с входами Bhi6opn регистра первого и второго блоков регистров, строби- рующие входы когорых соединены с вхо- дом синх;5онпзации устройства, вход режима загиси-сч1ггывания устройства соединен с входом разрешения записи и выд,ачи ин||)ормации первого блока входных регистров и через элемент 1Е с нхо,г;ом разрешения записи и выдачи информации второго блока входных регистров, Ftxo;; режима записи и установки адреса ус 1-ройства соединен с упрап; Я1лщ11ми входами первого и второ- го мультиплексо|)он, выход первого мультиплексор, соединен с входом записи бгюка :ia -i4TH кадра, первый вход записи vcTpono i на соединен с п.ервым

ииформаиисипцим иход(1м первого мультиплексора и с лходом записи бдокл буферных регистров, пыход KOTOpoi o является ви;1.еопыходом индикации кадра устройства, HTopiM i пход записи устройстнл соединен с вт(1рым инфор- манионным входом первого мультиплексора, вход установки режима считывавый информационный вход второго муль тинлексора является вторым адресным входом устройства, второй ин(юрма- ционньп вход блока адресации является третьим адресным входом у-стройст- на, выход блока адресации соединен с вторым информационным входом второго мультиплексора, выход которого соединен с адресн1,гм входом блока памяти кадра, т)ыход которого является видеовыходом обработки кадра устройства .

2.YcTpoficTBo по п. 1 , о т л и - чающееся тем, что первьоЧ и втор( блоки входных регистров содержат по восемь регистров, причем информационные входы всех регистров объединены и являются входом цифрового телевизионного сигнала устройств,), а выходы регистров первого и второго блоков входных регистров объединены соответственно в выходы первого и второго блоков входных регистров, входы выбора кристалла входных регистров первого блока входных регистров нонарно объединены с входами выбора кристалла регистров второго блока входных регистров и являются первым адресным входом устройства, стробирующие входы регистров первого и второго блоков входных регистров объединены и являются входом синхронизации устройства, входы разрешения записи и вьщачи информации регистров первого блока входных регистров объединены и являются входом режима записи-считывания устройства, который через элемент НЕ соединен с входами разрешения записи и выдачи информации регистров второго блока . входных регистров.

3.Устройство по п. 1, о т л и- чающееся тем, что блок адресации содержит первый и второй регистры, первый и второй дешифраторы, сумматор по модулю восемь, восемь

коммутаторор . HuceMti супмп i (ipiM. элемент ПК, при этом ииформпцш-иг М. входы перног о и нторос о регистром объединены и являются BTOPI.IM niuJxipMa ционньгм входом блока ллреспцин, tu.i- ход второго регистра соединен с п(;р- выми информационными входами нг.ех коммутаторов, информационными входами первого дешифратора и первым информационным входом сумматора по модулю восемь, стробирующий вход первого дешифратора соединен с входом элемента НЕ и являе-тся первым инф(1рмапион- ным входом блока адресапии, выходь первого регистра соединены с первглми информационными входами каждого комму татора и вторым информационным 1 хпдс1м сумматора по модулю восемь, В1)1хс)д1,1 сумматора по модулю восемь ссюлине

6

iiM г инф1 )р. Н1,)Н1.1ми nrnpni ii Д(М11ифр;гг лра , ныхпл KOTOpcr-i i соединен г унрлвляницими входами каждого комму )п, выходы первого дешифратора соединены с пермыг-ш информационными входами каждого сумматора, выx(JД i-ro коммутатора, где 1,...,8, соединен с BTOphc i информационным входом i-ro сумматора, выход K-rc.i сумматора, где ,...,7, соединен с вторыми информационными входами (К+1)-х коммутаторов, при этом выход восьмого сумматора соединен с вторыми информационными входами первого коммутатора, выходы коммутаторов объединены и являются выводом блока адресации, выход элемента НЕ соединен с третьими информационными входами сумматоров .

фи. 2

IJ

фиг. J

фие.

ip

Ч|

tfi

«

:э

еTnKTOSO

f acroTO В ход 12

Фи.б

Т

-6ь1ходы дешасрратора 111 (Риз. 8

Составитель А, Пак Редактор Е. Копча Техред и.Попович

Заказ 5192/50 Тираж 670Подписное

ВНИШИ Государстпе1гного комитета СССР

по делам изобретений и открытиГ 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Прпекгиая, «

/ А

Т

9us. 7

Корректор О.Кравцова

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Имитатор для тестирования компонентов моноканальной локальной вычислительной сети | 1987 |

|

SU1446621A1 |

| Устройство для формирования адреса видеопамяти растрового графического дисплея | 1987 |

|

SU1462407A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

| Устройство памяти на кадр цифрового теливизионного изображения | 1988 |

|

SU1600002A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

| Устройство для запоминания цифрового телевизионного сигнала | 1980 |

|

SU1043835A1 |

| Устройство для отображения и хранения информации телевизионного изображения | 1981 |

|

SU1277910A3 |

Изобретение относится к вычисли- тельно11 технике ;у1я цифровой обработки телевиаионныУч изображений и мотхет быть использовано дчя построения оне- ративных заноминающих ycTpoiiCTB (ОПЗ) систем обработки видеоинформации. Цель изобретения состоит в paci Oipe- нии функнионапьных возможностей устройства за счет организации трехстороннего обмена информпциеГ. Для тто- го я ycTpoiicTBO ДД1Я уиравления иа- мятью Бидеоинформадии, содержащее блок I памяти кадра, блок 4 буферных регистров, блок 6 адресации, дополнительно введены блоки 2 и 3 входтппх регистров, два fyльтннлeкcopa 7 и 8, злемент НЕ 5. 2 з.п. (г-лы, 8 ил. б (Л оо 4 ОО СХ) а: о фиг- /

| Устройство для запоминания цифрового телевизионного сигнала | 1980 |

|

SU1043835A1 |

| Патент СИА № 4434502, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-30—Публикация

1986-06-25—Подача