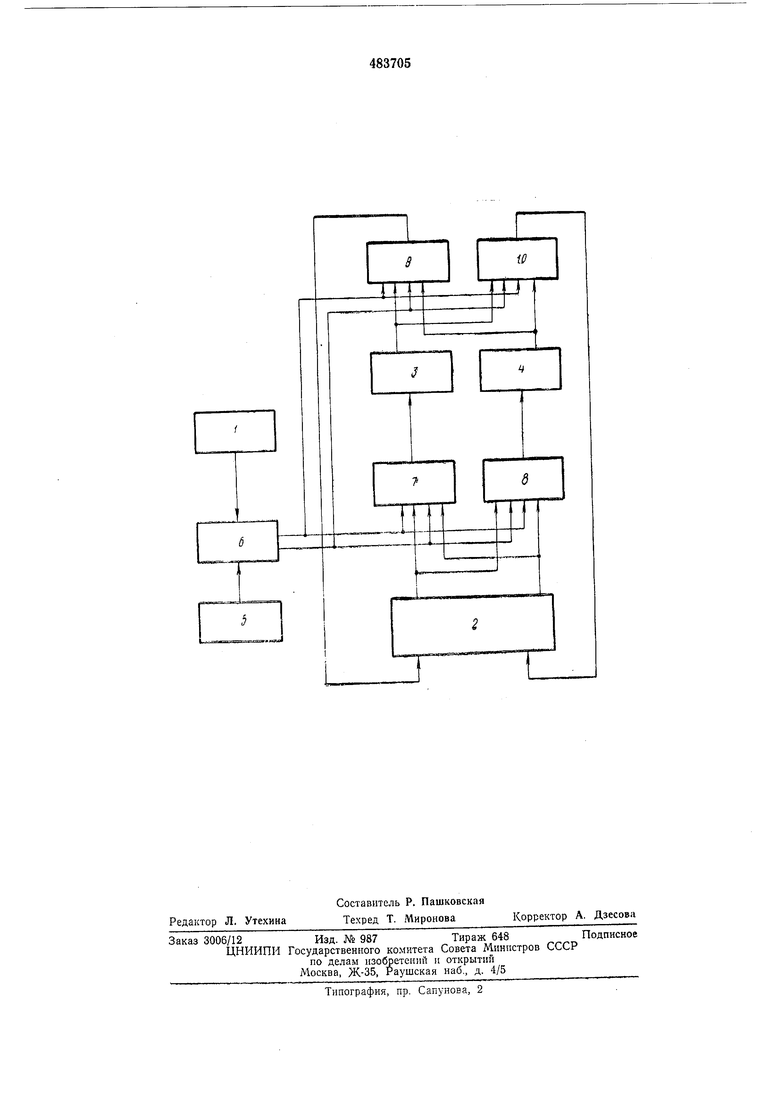

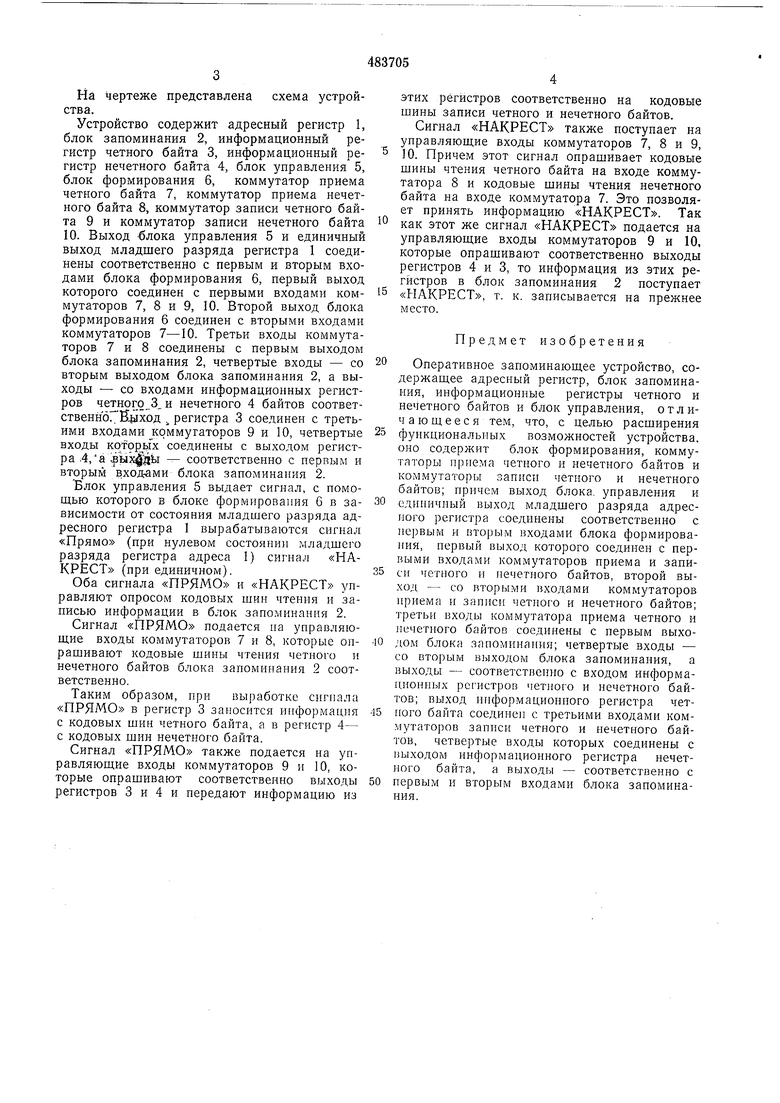

На чертеже представлена схема устройства. Устройство содержит адресный регистр 1, блок запоминания 2, информационный регистр четного байта 3, информационный регистр нечетного байта 4, блок управления 5, блок формирования 6, коммутатор приема четного байта 7, коммутатор приема нечетного байта 8, коммутатор записи четного байта 9 и коммутатор записи нечетного байта 10. Выход -блока управления 5 и единичный выход младшего разряда регистра 1 соединены соответственно с первым и вторым входами блока формирования 6, первый выход которого соединен с первыми входами коммутаторов 7, 8 и 9, 10. Второй выход блока формирования б соединен с вторыми входами коммутаторов 7-10. Третьи входы коммутаторов 7 и 8 соединены с первым выходом блока запоминания 2, четвертые входы - со вторым выходом блока запоминания 2, а выходы - со входами информационных регистров четног о,.3 и нечетного 4 байтов соответственноГНуход .. регистра 3 соединен с третьими входами коммугаторов 9 и 10, четвертые входы Kof9pbfx соединены с выходом регистра 4,а - соответственно с первым и вторым вход-ами блока запоминания 2. Блок управления 5 выдает сигнал, с помощью которого в блоке формирования б в зависимости от состояния младшего разряда адресного регистра 1 вырабатываются сигнал «Прямо (при нулевом состоянии младшего разряда регистра адреса I) сигнал «НАКРЕСТ (при единичном). Оба сигнала «ПРЯМО и «НАКРЕСТ управляют опросом кодовых шин чтения и записью информации в блок запоминания 2. Сигнал «ПРЯМО подается на управляющие входы коммутаторов 7 и 8, которые онрашивают кодовые шины чтения четного и нечетного байтов блока запоминания 2 соответственно. Таким образом, при выработке сигнала «ПРЯМО в регистр 3 заносится информация с кодовых шин четного байта, а в регистр 4- с кодовых шин нечетного байта. Сигнал «ПРЯМО также подается на управляющие входы коммутаторов 9 и 10, которые опрашивают соответственно выходы регистров 3 и 4 и передают информацию из этих регистров соответственно на кодовые шины записи четного и нечетного байтов. Сигнал «НАКРЕСТ также поступает на управляющие входы коммутаторов 7, 8 и 9, 10. Причем этот сигнал опрашивает кодовые шины чтения четного байта на входе коммутатора 8 и кодовые шины чтения нечетного байта на входе коммутатора 7. Это позволяет принять информацию «НАКРЕСТ. Так , Q сигнал «НАКРЕСТ подается на управляющие входы коммутаторов 9 и 10, которые опрашивают соответственно выходы регистров 4 и 3, то информация из этих регйстров в блок запоминания 2 поступает «НАКРЕСТ, т. к. записывается на прежнее Предмет изобретения Оперативное запоминающее устройство, солЧержащее адресный регистр, блок запоминания, информационные регистры четного и нечетного байтов и блок управления, отличающееся тем, что, с целью расширения функциональных возможностей устройства, оно содержит блок формирования, коммутаторы приема четного и нечетного байтов и коммутаторы записи четного и нечетного байтов; причем выход блока, управления и единичный выход младшего разряда адресного регистра соединены соответственно с первым и вторым входами блока формирования, первый выход которого соединен с первыми входами коммутаторов приема и записи четного и нечетного байтов, второй выход - со вторыми в.ходами коммутаторов приема и записи четного и нечетного байтов; третьи входы коммутатора приема четного и нечетного байтов соединены с первым выходом блока злпоминания; четвертые входы - со вторым выходом блока запоминания, а выходы - соответственно с входом информаплонных регистров четного и нечетного байтов; выход ипформационного регистра четнего байта соединен с третьими входами коммутаторов записи четного и нечетного байтов, четвертые входы которых соединены с 1 ыходом информационного регистра нечетнего байта, а выходы - соответственно с первым и вторым входами блока запоминания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1986 |

|

SU1322298A2 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

Авторы

Даты

1975-09-05—Публикация

1972-07-10—Подача