Изобретение относится h, па,-,1-;Оте--с- нике и может иcпoлpJЭoвaт:ь ;я п ctfcre- мех автоматического контро.гьч

Цель изобретения упрсипение при одновремен ;ом повьниенни тсгчнос- ти ,, быстродействия и ут-1е:;ьи;еи5--;я уроггкя импульсных помех а 5 Е;1ход : ом скгняле,

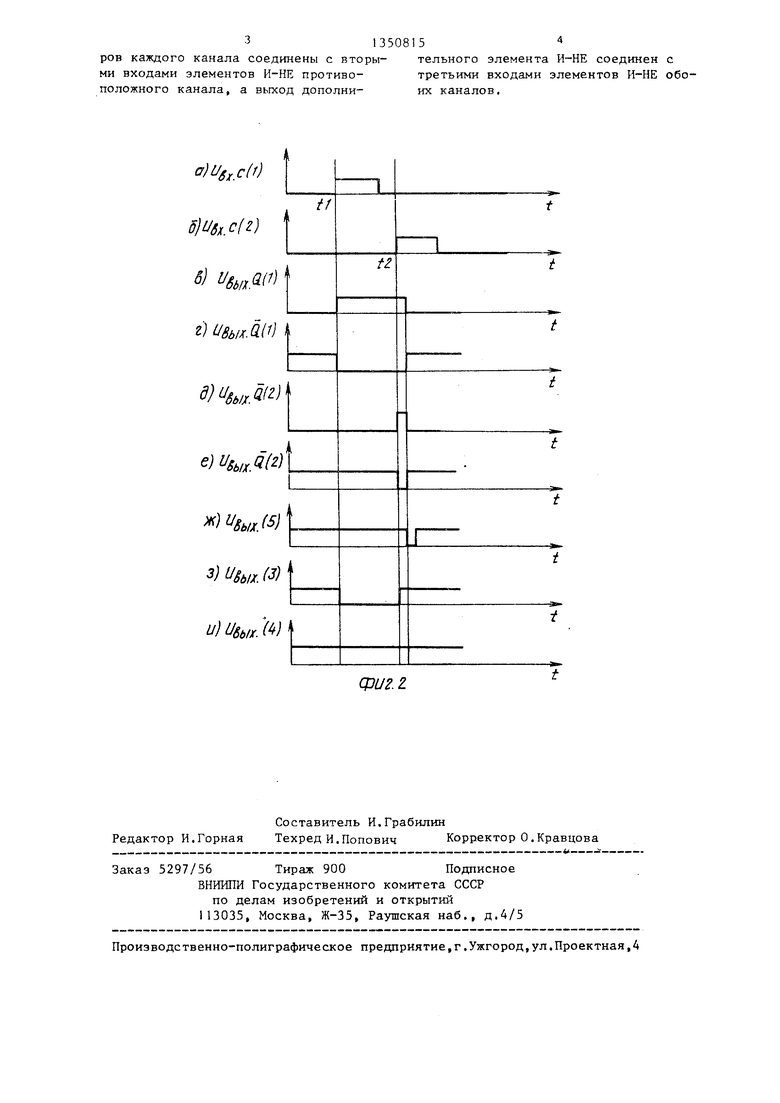

На фиг,1 npiiBexi,ena структурная электрическая схема )::редлг.гаемого временного дис1сримг 1натора ; на фиг , 2 - временные диаграммы, поясзгяюпгие работу дискриминатора,.

Временной дискриминатор содержит D-триггеры 1 и 2, элементы И-НЕ 3 и 4 и дополнительный элемент И-ИЕ 5,

Времетьчой дискр р-кнтатор работает следующим образом.

При первоначальном пуске при подаче напряжения на временной дискриминатор D-триггеры 1 и 2 устананли- ваются н нулевое сос гоянке „ Лри эт,ом на прямых О выходах 1)-триг геров 1 к 2 устанавливаются низкие,, а на ннвв)- сных Q BbicoKi-te потенциалы. На зыхо- дах элементов И-НЕ 3 и . устанавливаются высокие потенциаль;:.

Пусть сигнал на входе с -шхрониза- ции D-триг гера 1 (фиг ,. 2 а) опережав г по времени сип-ал, поступаюппгй f;a вход сияхрониза.ции В-триггера L (фиг. 26), При передаче уровня из О

Q и инверсном Q выходах Э-триг- ерй 1 устанавливаштся cooTBBTCTPievb o уровни логической единицы Сфиг,2е). и логигсеского нуля (фиг „2 ) . ние уровня логической единицы на пря мом Q выходе D-триггера 1 приводит к изменению состояния элемен ь И-НЕ 3 из единичного в нулевое (фиг , 2 з) ,, поскольку на его втором и ретьем входах в это время присутс ii S TOT уровни логической единицы, пос 1 упаю;иие соответственно с инверсп-оги О выход;; D-триггера 2 Сфит„2е) н 1 ьг/;с-,:г,а эля-мента И-НР 5 (фиг„2;к), В момент t, (фиг,2б) пркгхода запаэдыла101Еег1 импульса на вход симхронизац -11 : 1 -триг- гера 2 на прямом выходе последиегс устанавливается уровень лог ической единицы (фиг. 2 з) на HHBeiJCHOiM - уровень логического нуля (()иг„2е) , Изменение выходкого уровня инверсного выхода D-триггера 2 из Г в О приводит к изменению выходкого уровня элемента 3 из О в 1. При этом на выходе элемент з. И-НЕ 3 с1юр-- мируется импульс (фиг,За),, плительriocTj котс- 5ого рапна величине фазового сдвига между опережающим и за- ггяздывающим имгА Л1зсами, Состояние элемента 4 не изменяется (фиг,. 2и). Кроме того, поязлениа уровня логической на прямом Q вы- коде D-Tp;irrepa 2 приводит к срабатыванию эла -ie.MTa 5s на его пыхо/ е появ.ляется уровень .п.огк /еско- го нуля (фиг,2ж)., поступающий f-:a входы сброса триггеров 5, сбрасываюгций

григ геры

V. 0

Кроме того,, урС1венъ логического нуля, лоступаюигий с БЬ хода элемента il-HE 5 ив рходы злементов 3 н 4j препя1 ствует появлекию иросг чек на выход.-,х этих з,пементов П-НЕ во время сбрсса D-триггеров 1 и 2.

Уровни лог ическаго HynHj устанав- ливаюи-иеся ка :(рямьгх выходах D-триг- 1 еров 1 и 2 (фиг,2 ), переводят

:;лемс; :т И-ПЕ 5 в исходное состояние ;:)иг.2л;) Iloc.ie этого временной дис- римин ; тор г стов К приему следующих ,-;миул; сов, Если сигнал на входе синхронизации D- триггера 2 опережает

((Ь - нал, поступаю)ций на вход синхро- гт заци : D-триггера К импульсj. дли- тель гсс;т ь которого равна величине фазозог о сдвига появ,ляется на эле- :.гите И--НЕ 4, В случае, если величи- а фазового c,3;;iiirfL и меньше д:1итель- ;ости у:м1тул:ьса v . лременной дискри- у и н а т э р раб ; тает а ч ал о г и ч н о ,

ор

V л а

о

Р

е н и я

5

0

Временной ,цискриминагор J содержа- два канала, ка:вдый из которЕ)К содержит последоза ге,; (ьно соединенные О триггер и элемент И-НЕ. зыходы которых являются вых;здами зременкого ,г:искримина горг1 J и дополнительнь й эле- 1ент i-v-t IE, входы которого соедннекь; / зьЕходами соотЕетствуюк{и :: D-тригге- ров 5 а выход - с вхе1,дами сброса D- риггеров 3 ггэиче ,м й-вхс,а,ы и--тригге- ров соединены с источником логической единидь,, а входз синхронизации D- Триггеров /1ллиют;;я входами временного диск РИМ и,на тора, отличаю- щ и и с я тем чтс:ч с целью упрощения при одновременком повышени,к точности,, Зыстродейстция и уменьшения уровня н ту;гьсных помех в вькоднок сигнале,, инверсные вькоды П триггеми входами элементов И-НЕ противоположного канала, а выход дополнитретьими входами элементов И-НЕ обоих каналов.

фиг. 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый дискри-МиНАТОР | 1979 |

|

SU843163A2 |

| Фазовый дискриминатор | 1984 |

|

SU1376229A1 |

| Устройство автоподстройки фазы тактовых импульсов | 1986 |

|

SU1527718A1 |

| Частотно-фазовый дискриминатор | 1977 |

|

SU699666A1 |

| Устройство воспроизведения информации с оптического носителя | 1986 |

|

SU1345248A1 |

| Устройство восстановления тактового сигнала из цифрового потока | 1991 |

|

SU1757114A1 |

| Устройство тактовой синхронизации приемника сигналов NRZ-L | 1988 |

|

SU1523030A1 |

| Цифровой частотно-фазовый дискриминатор | 1987 |

|

SU1494204A2 |

| Преобразователь кода во временной интервал | 1987 |

|

SU1474848A1 |

| Импульсный частотно-фазовый детектор | 1980 |

|

SU985929A1 |

Изобретение относится к радиотехнике. Цель изобретения - упрощение при одновременном повышении точности, быстродействия и уменьшения уровня импульсных помех в выходном сигнале, Временной дискриминатор содержит D-триггеры I и 2 и элементы И-НЕ 3 - 5. Если сигнал на входе синхронизации D-триггера 1 опережает по времени сигнал синхронизации D- триггера 2, изменение выходного уровня инверсного выхода D-триггера 2 из 1 в О приводит к изменению выходного уровня элемента И-НЕ 3 из О в 1. При этом на выходе элемента И-НЕ 3 формируется импульс, длительность которого равна величине фазового сдвига между опережающим и запаздывающим импульсами. Состояние злемента И-НЕ 4 не изменяется. Если сигнал на входе синхронизации D-триггера 2 опережает сигнал на входе синхронизации D-триггера 1, импульс, длительность которого равна величине фазового сдвига, появляется на элементе И-НЕ 4, Временной дискриминатор работает аналогичным образом и в случае, если величина фазового сдвига меньше длительности импульса. 2 ил.

| Частотно-фазовый детектор | 1982 |

|

SU1095351A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Фазовый дискриминатор | 1982 |

|

SU1026283A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-11-07—Публикация

1984-07-06—Подача