Изобретение относится к автома- и вычислительной технике и может быть использовано в АСУ ТП для управ- .|1ения динамическими процессами. ; Целью изобретения является повыше- 1ие быстродействия.

Сущность изобретения заключается 1в обеспечении высокой гибкости адресации микрокоманд путем обеспечения Ветвлений как по значениям логичес- ;ких условий, проверяемых после выпол- |нения текущей микрокоманды, так и по наборам значений булевых производных в заданных точках выполняемой микропрограммы.

Контроллером реализуются простые и сложные ветвления. При реализации ; простого ветвления адрес А;, очередной микрокоманды определяется выражением

U A /(AVx;),

(1)

; гдеА -. код немодифицируемой части

.адреса; .

:А - значение модифицируемой

: части адреса (один разряд);

. X - значение проверяемого логи-

ческого уровня.

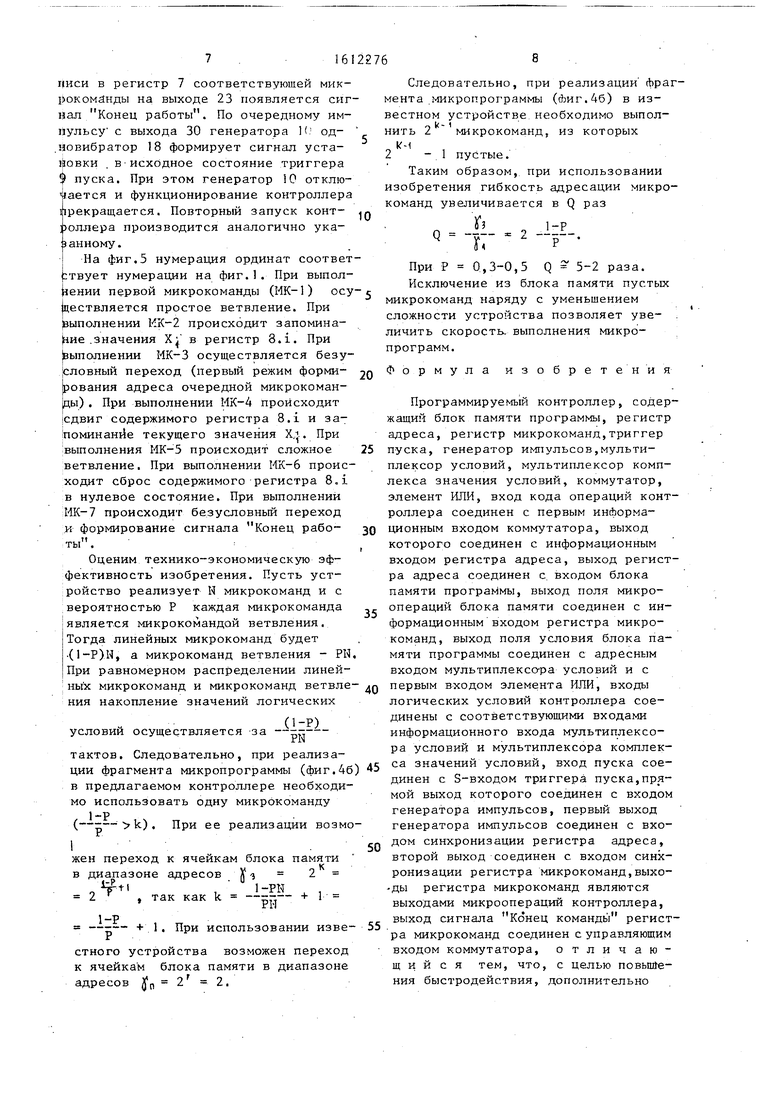

Следовательно, в этом случае после выполнения текущей микрокоманды возможен переход по двух направлениям (А ; А /О, А%, А /1). Дня реализации сложных ветвлений в ходе выполнения микропрограммы запоминаются значения логических ус .ловий в заданных контрольных точках Комплекс этих условий используется при реализации сложного ветвления. Адрес А 4 очередной микрокоманды при реализации сложного ветвления определяется выражением

А., А /У,/УД/.../УК,

(2)

где А - код немодифицированной час- .ти адреса;

у;

А; - значение i-ro разряда модифицируемой части адреса; Хч - значение проверяемого логи- . ческого условия Xj в i-й

контрольной точке; k - число значений логического

условия Xj(J 1,1), ис- 0 пользуемых при реализации

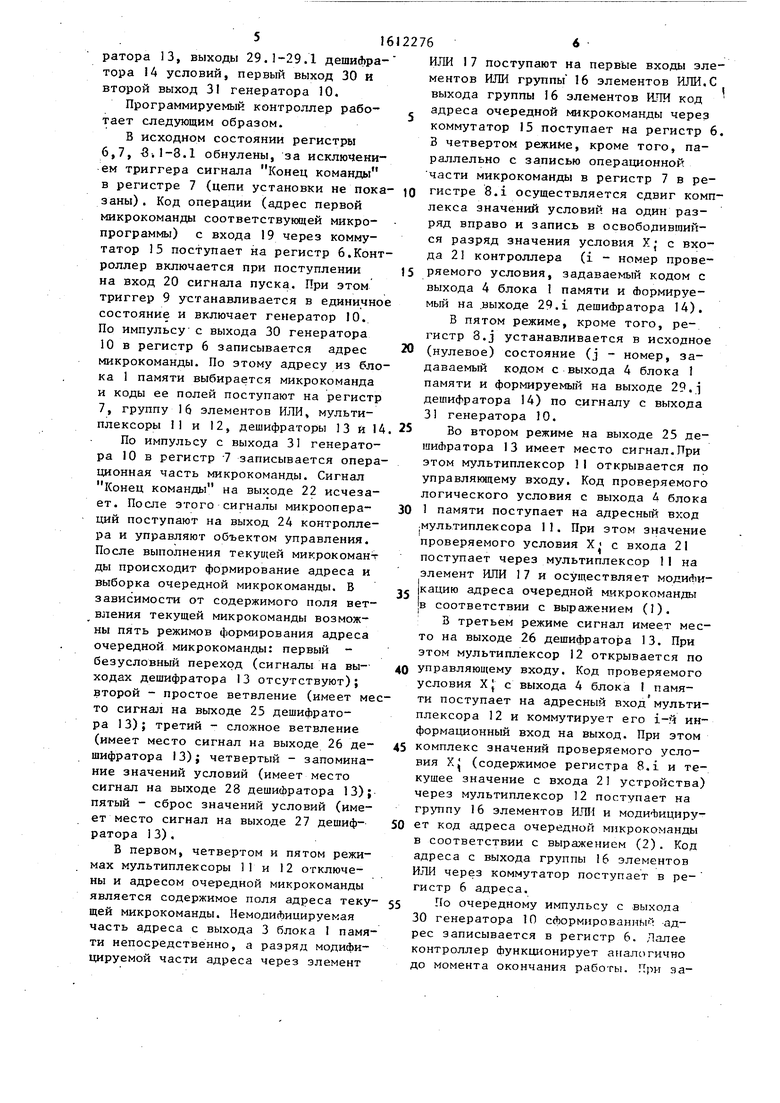

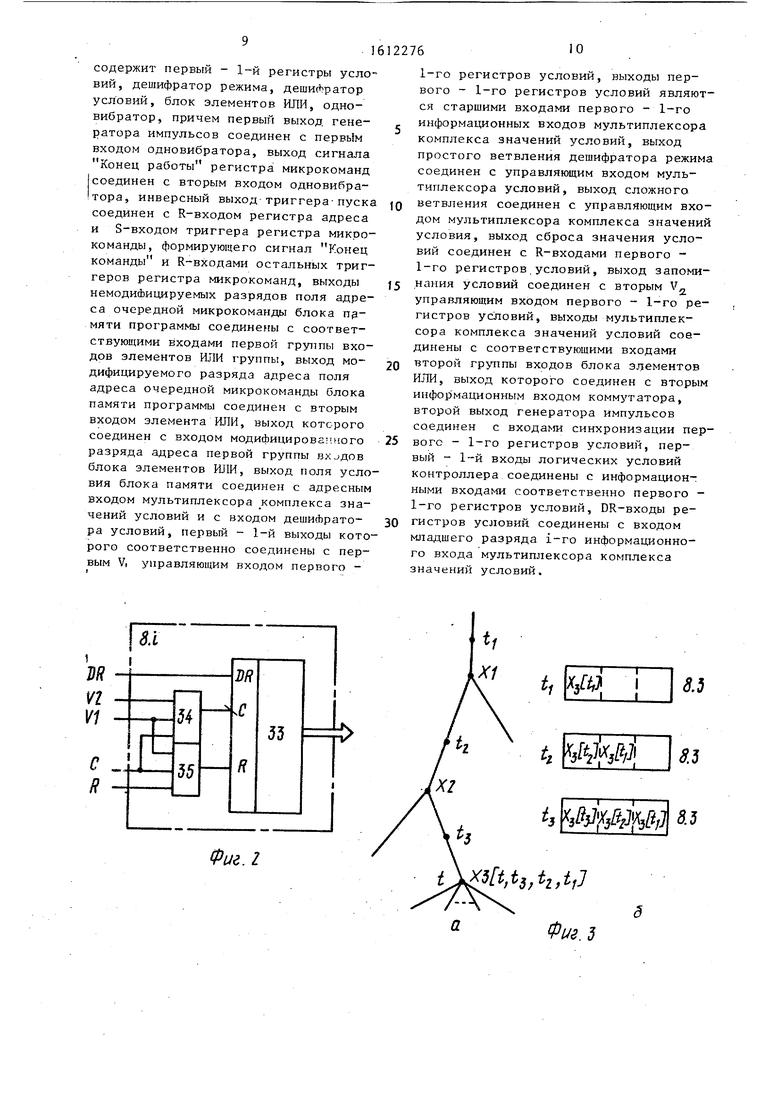

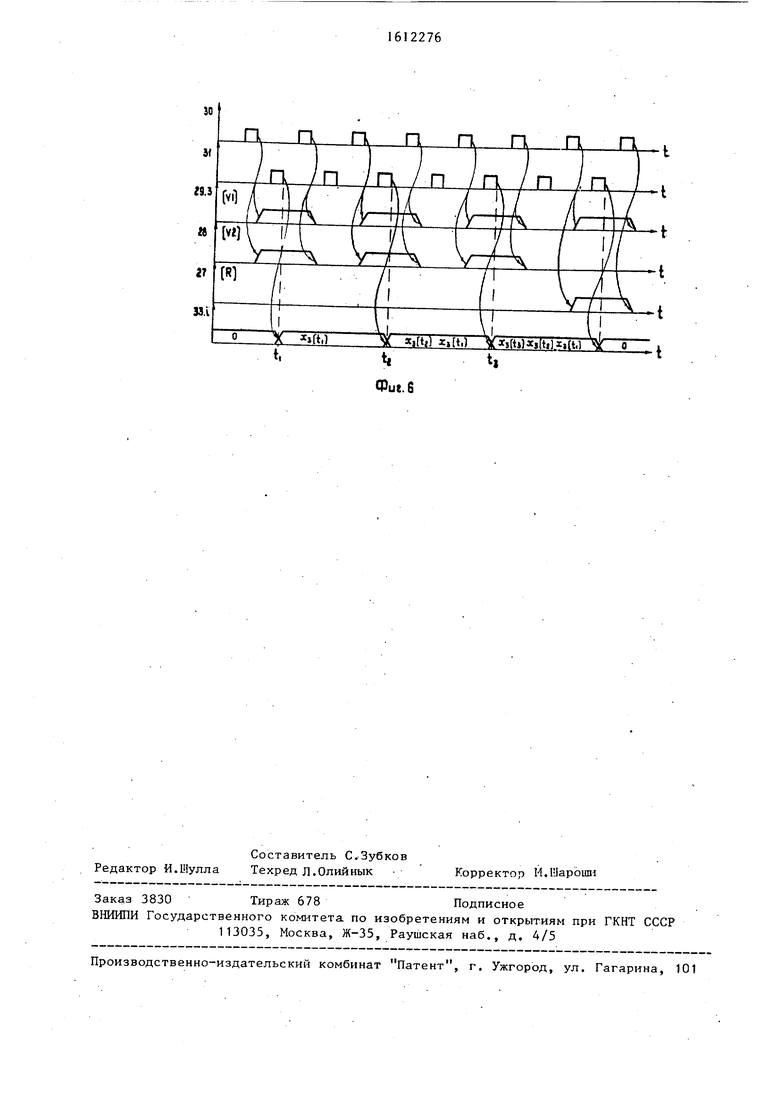

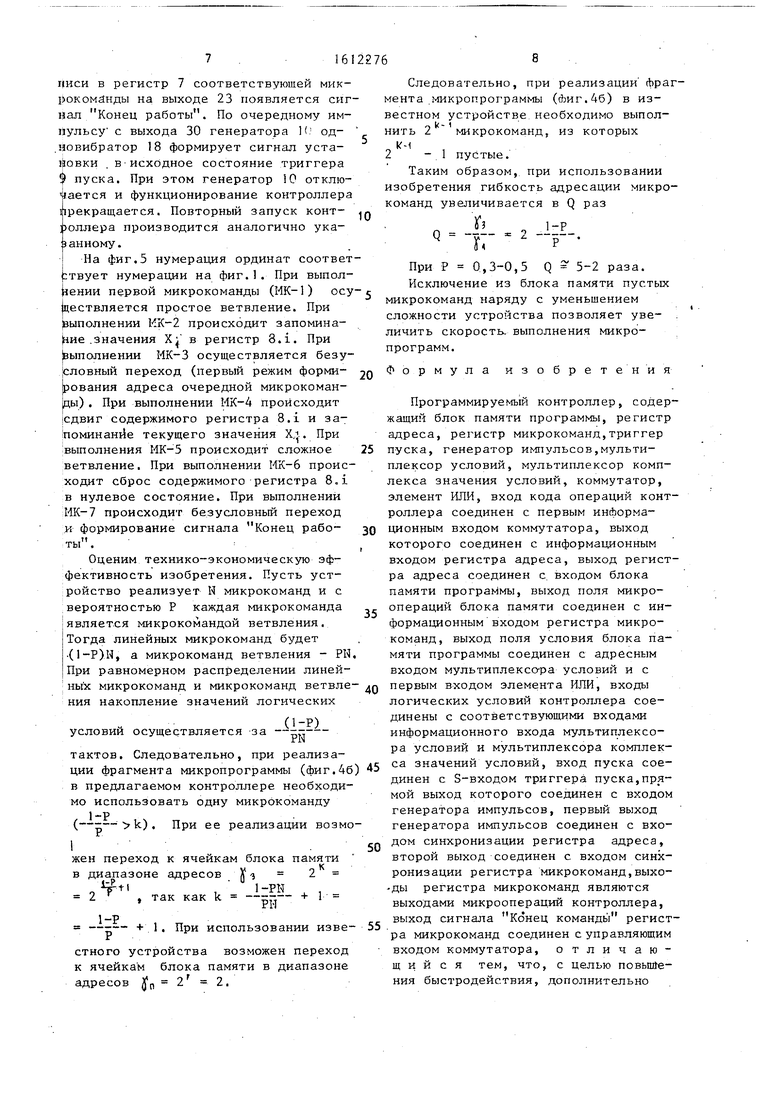

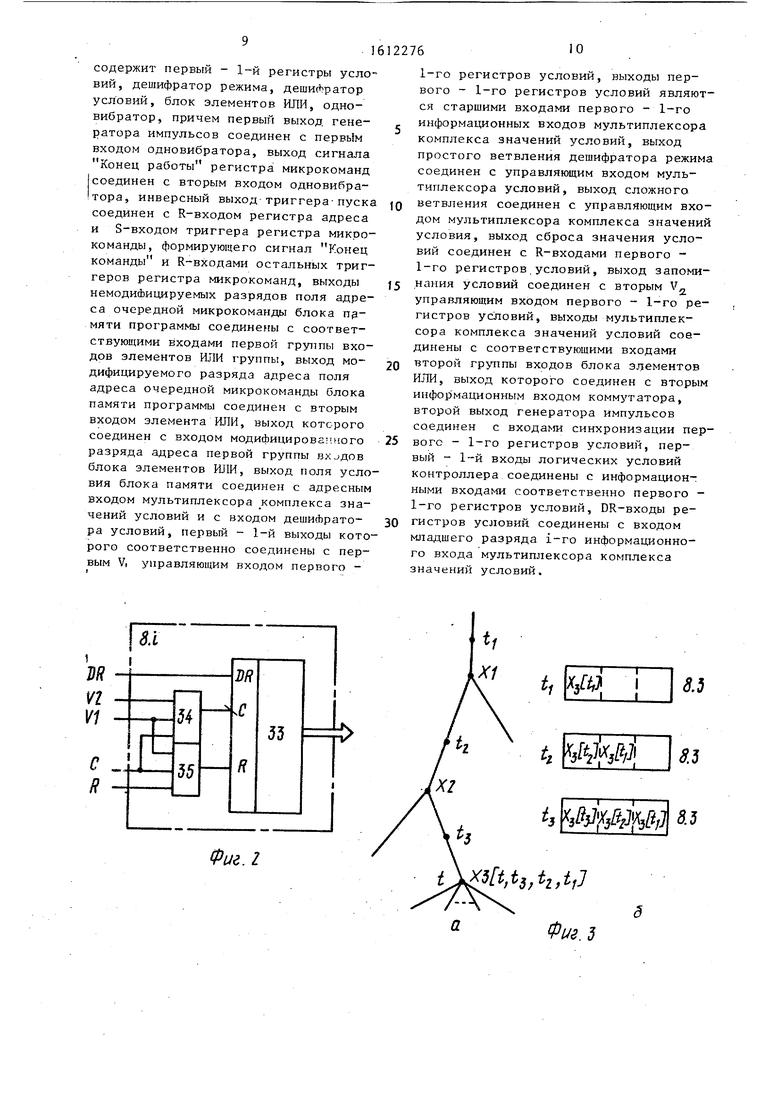

сложных ветвлений. На (Ьиг. приведена Лункциоиальная схема программируемого контроллера; на фиг.2 - организация цепей управле- 5 НИН 8.i-ro регистра условий; на . . фиг. 3 - фрагмент микропрограммы и содержимое i-ro регистра условий (i 3) в процессе выполнения этого Фрагмента; на фиг.4 - фрагменты мик- 0 ропрограмм с реализацией простого ветвления и сложного ветвления; на фиг. 5 - временная диаграмма работы контроллера; на фиг.6 - временная диаграмма работы регистра логических 5 условий.

Программируемый контроллер (Фиг.1) содержит блок 1 памяти с выходами поля микроопераций 2, поля адреса очередной микрокоманды 3, поля условия 0 4, поля ветвления 5, регистр 6 адреса, регистр 7 микрокоманд, регистры 8.1-8.1 условий, триггер 9 пуска,генератор 10, мультиплексор 11 условий, мультиплексор 12 комплекса значений 45 условий, дешифратор 13 режима, дешифратор 14 условий, коммутатор 15,группу 16, элементов ИЛИ, элемент ИЛИ 17, . одновибратор 18, вход 19 кода операции, вход 20 пуска, входы 21 логичес- 50 ких условий (выходы датчиков состояния объектов управления), выход 22 сигнала Конец команды, выход 23 сигнала Конец работы, выходы 24 сигналов микроопераций контроллера, ГС выход 25 простого ветвления дешифратора 13, выход 26 сложного ветвления дешифратора 13, выход 27 сбро- iса значения условий дешифратора 13, выход 28 запоминания условия дешиф

ратора 13, выходы 29.)-29.1 дешифратора 14 условий, первый выход 30 и второй выход 31 генератора 10.

Программируемый контроллер работает следующим образом.

В исходном состоянии регистры 6,7, -8.1-8.1 обнулены, за исключением триггера сигнала Конец команды в регистре 7 (цепи установки не покзаны) . Код операции (адрес первой микрокоманды соответствующей микропрограммы) с входа 19 через коммутатор 15 поступает на регистр 6.Конроллер включается при поступлении на вход 20 сигнала пуска. При этом триггер 9 устанавливается в единичн состояние и включает генератор 10. По импульсу с выхода 30 генератора 10 в регистр 6 записывается адрес микрокоманды. По этому адресу из блока 1 памяти выбирается микрокоманда и коды ее полей поступают на регистр 7, группу 16 элементов ИЛИ, мультиплексоры II и 12, дешифраторы 13 и 1

По импульсу с выхода 31 генератора 10 в регистр -7 записывается операционная часть микрокоманды. Сигнал Конец команды на выходе 22 исчезает. После этого сигналы микроопераций поступают на выход 24 контроллера и управляют объектом управления. После выполнения текущей микрокоман-г ды происходит формирование адреса и выборка очередной микрокоманды. В зависимости от содержимого поля вет- вления текущей микрокоманды возможны пять режимов формирования адреса очередной микрокоманды: первый - безусловный переход (сигналы на выходах дешифратора 13 отсутствуют); второй - простое ветвление (имеет мето сигнал на выходе 25 дешифратора 13); третий - сложное ветвление (имеет место сигнал на выходе 26 дешифратора 13); четвертый - запоминание значений условий (имеет место сигнал на выходе 28 дешифратора 13); пятый - сброс значений условий (имеет место сигнал на выходе 27 дешифратора 13).

В первом, четвертом и пятом режимах мультиплексоры 11 и 12 отключены и адресом очередной микрокоманды является содержимое поля адреса теку- щей микрокоманды. НемодиЛииируемая часть адреса с выхода 3 блока I памяти непосредственно, а разряд модифицируемой части адреса через элемент

1612276

10

20

25

5

ИЛИ 17 поступают на первые входы элементов ИЛИ группы 16 элементов ИЛИ.С выхода группы 16 элементов ИЛИ код адреса очередной микрокоманды через коммутатор 15 поступает на регистр 6. 3 четвертом режиме, кроме того, параллельно с записью операционной части микрокоманды в регистр 7 в регистре 8.1 осуществляется сдвиг комплекса значений условий на один разряд вправо и запись в освободившийся разряд значения условия Х; с входа 21 контроллера (i - номер прове- 15 ряемого условия, задаваемый кодом с выхода 4 блока 1 памяти и Нормируемый на .выходе 29.1 дешифратора 14). В пятом режиме, кроме того, регистр 8.J устанавливается в исходное (нулевое) состояние (j - номер, задаваемый кодом с выхода 4 блока 1 памяти и формируемый на выходе 29.1 дешифратора 14) по сигналу с выхода 31 генератора 10.

Во втором режиме на выходе 25 дешифратора 13 имеет место сигнал.При этом мультиплексор 11 открывается по управляющему входу. Код проверяемого логического условия с выхода Д блока 1 памяти поступает на адресный вход |Мультиплексора 11. При этом значение проверяемого условия с входа 21 поступает через мультиплексор 11 на элемент ИЛИ 17 и осуществляет модиАи- J5 кацию адреса очередной микрокоманды

30

IB соответствии с выражением (1).

В третьем режиме сигнал имеет место на выходе 26 дешифрато за 13. При этом мультиплексор 12 открывается по 40 управляющему входу. Код проверяемого условия Х| с выхода 4 блока I памяти поступает на адресный вход мультиплексора 12 и коммутирует его 1-й информационный вход на выход. При этом 45 комплекс значений проверяемого условия Xj (содержимое регистра 8.1 и текущее значение с входа 21 устройства) через мультиплексор 12 поступает на группу 16 элементов ИЛИ и моди-Ьициру- ет код адреса очередной микрокоманды в соответствии с выражением (2). Код адреса с выхода группы 16 элементов ИЛИ через коммутатор поступает в ре- гистр 6 адреса.

По очередному импульсу с выхода 30 генератора Ш сформированные адрес записывается в регистр 6. Далее контроллер функционирует аргалогично до момента окончания работы. При за0

1(иси в регистр 7 соответствуюшей микрокоманды на выходе 23 появляется сигнал Конец работы. По очередному импульсу с выхода 30 генератора К/ од- новибратор 18 формирует сигнал уста- iSOBKH . в-исходное состояние триггера пуска. При этом генератор iO отклю- iJaeTCH и функционирование контроллера прекращается. Повторный запуск конт- )оллера производится аналогично указанному.

I На фиг.5 нумерация ординат соответ Ьтвует нумерации на фиг.1. При выпол- |1ении первой микрокоманды (МК-1) осу |цествляется простое ветвление. При выполнении МК-2 происходит запоминание .значения Х| в регистр 8.1. При выполнении МК-3 осуществляется безу- ловный переход (первый режим форми- ования адреса очередной микрокоманды) . При выполнении МК-4 происходит |сдвиг содержимого регистра 8.1 и запоминание текущего значения Х,|. При выполнения МК-5 происходит сложное ветвление. При выполнении МК-6 происходит сброс содержимого регистра 8.1 в нулевое состояние. При выполнений МК-7 происходит безусловный переход и формирование сигнала Конец рабо- ты.

Оценим технико-экономическую эффективность изобретения. Пусть устройство реализует N микрокоманд и с вероятностью Р каждая микрокоманда является микрокомандой ветвления. Тогда линейных микрокоманд будет (1-Р)М, а микрокоманд ветвления - РН При равномерном распределении линей- ; ны х микрокоманд и микрокоманд ветвле ния накопление значений логических

условий осуществляется -за

iliE).PN

тактов. Следовательно, при реализации фрагмента микропрограммы (фиг.46) 45 в предлагаемом контроллере необходимо использовать одну микрокоманду

(

1-р

k). При ее реализации возможен переход к ячейкам блока памяти

в диапазоне адресов V ч

и

как k

1-PN РН

2 + 1.-

1-Р

+ 1. При использовании изве- 55

стного устройства возможен переход к ячейкам блока памяти в диапазоне адресов 2 2.

Следовательно, при реализации фрагмента микропрограммы (6иг.4б) в известном устройстве необходимо выполнить 2 микрокоманд, из которых

k-i

2 - 1 пустые.

Таким образом, при использовании изобретения гибкость адресации микрокоманд увеличивается в Q раз

, Р

О - Ь

Q

5

5

0

5

При Р 0,3-0,5 Q 5-2 раза.

Исключение из блока памяти пустых микрокоманд наряду с уменьшением сложности устройства позволяет увеличить скорость, выполнения микропрограмм.

Формула изобретения

Программируемый контроллер, содержащий блок памяти программы, регистр адреса, регистр микрокоманд,триггер пуска, генератор импульсов,мультиплексор условий, мультиплексор комплекса значения условий, коммутатор, элемент ИЛИ, вход кода операций контроллера соединен с первым информационным входом коммутатора, выход которого соединен с информационным входом регистра адреса, выход регистра адреса соединен с. входом блока памяти программы, выход поля микроопераций блока памяти соединен с ин- форма1дионным входом регистра микрокоманд, выход поля условия блока памяти программы соединен с адресным входом мультиплексо-ра условий и с первым входом элемента ИЛИ, входы логических условий контроллера соединены с соответствующими входами информационного входа мультиплексора условий и мультиплексора комплекса значений условий, вход пуска соединен с S-входом триггера пуска,прямой выход которого соединен с входом генератора импульсов, первый выход генератора импульсов соединен с входом синхронизации регистра адреса, второй выход соединен с входом синхронизации регистра микрокоманд,выхо- -ды регистра микрокоманд являются выходами микроопераций контроллера, выход сигнала Конец команды регист- ра микрокоманд соединен с управляющим входом коммутатора, отличающийся тем, что, с целью повышения быстродействия, дополнительно

содержит первый - 1-й регистры условий, дешифратор режима, дешифратор условий, блок элементов ИЛИ, одно- вибратор, причем первый выход генератора импульсов соединен с первЫм входом одновибратора, выход сигнала Конец работы регистра микрокоманд соединен с вторым входом одновибратора, инверсный выход триггера-пуск соединен с R-входом регистра адреса и S-входом триггера регистра микрокоманды, формирующего сигнал Конец команды и R-входами остальных триггеров регистра микрокоманд, выходы немодифицируемых разрядов поля адреса очередной микрокоманды блока пэ- мяти программы соединены с соответствующими входами первой группы входов элементов ИЛИ группы, выход модифицируемого разряда адреса поля адреса очередной микрокоманды блока памяти программы соединен с вторым входом элемента ИЛИ, выход которого соединен с входом модифицировг- ного разряда адреса первой группы входов блока элементов ИЛИ, выход поля условия блока памяти соединен с адресным входом мультиплексора комплекса значений условий и с входом дешифратора условий, первый - 1-й выходы которого соответственно соединены с первым Vi управляющим входом первого 1-го регистров условий, выходы первого - 1-го регистров условий являются старшими входами первого - 1-го J информационных входов мультиплексора комплекса значений условий, выход простого ветвления дешифратора режима соединен с управляющим входом мультиплексора условий, выход сложного O ветвления соединен с управляющим входом мультиплексора комплекса значений условия, выход сброса значения условий соединен с R-входами первого - 1-го регистров.условий, выход запоми- 5 нания условий соединен с вторым V, управляющим входом первого - 1-го регистров условий, выходы мультиплексора комплекса значений условий соединены с соответствующими входами второй группы входов блока элементов ИЛИ, выход которого соединен с вторым информационным входом коммутатора, второй выход генератора импульсов соединен с входами синхронизации первого - 1-го регистров условий, первый - 1-й входы логических условий контроллера соединены с информационными входами соответственно первого - 1-го регистров условий, DR-входы ре- 0 гистров условий соединены с входом младшего разряда i-ro информационного входа мультиплексора комплекса значений условий.

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый контроллер | 1988 |

|

SU1624404A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Программируемый контроллер | 1988 |

|

SU1642446A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в АСУ ТП для управления динамическими процессами. Цель изобретения - повышение быстродействия устройства. Она достигается введением первого - L-го регистров 8.1-8.L условий, дешифратора 13 режима, дешифратора 14 условий, группы 16 элементов ИЛИ, одновибратора. Сущность изобретения состоит в обеспечении высокой гибкости адресации микрокоманд путем обеспечения ветвлений как по значениям логических условий, проверяемых после текущей микрокоманды, так и по наборам значений булевых производных в заданных точках выполняемой микропрограммы. Это обеспечивает исключения из блока памяти пустых микрокоманд, что наряду с уменьшением сложности устройства позволяет увеличить скорость выполнения микропрограмм. 6 ил.

М

П V1

Фиг. 2

КМ

d.s

1-ГТ

t, Ш /г/71

S.5

5

Wm j

i., Фиг. 5

Ш-t

Нет

К AI .jjA2i

i .tff.tf.r),... Фиг.В

МК-1 fiK-2 МК-3 MK-h МК-5 МК-6

|.

1

MK-i

Фиг.5

| Микропрограммное устройство управления | 1981 |

|

SU1007106A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-12-07—Публикация

1988-09-20—Подача