Изобретение относится к радиотехнике и может быть использовано в приемопередающей и измерительной технике.

Цель изобретения - повьпиение верхней границы диапазона рабочих частот.

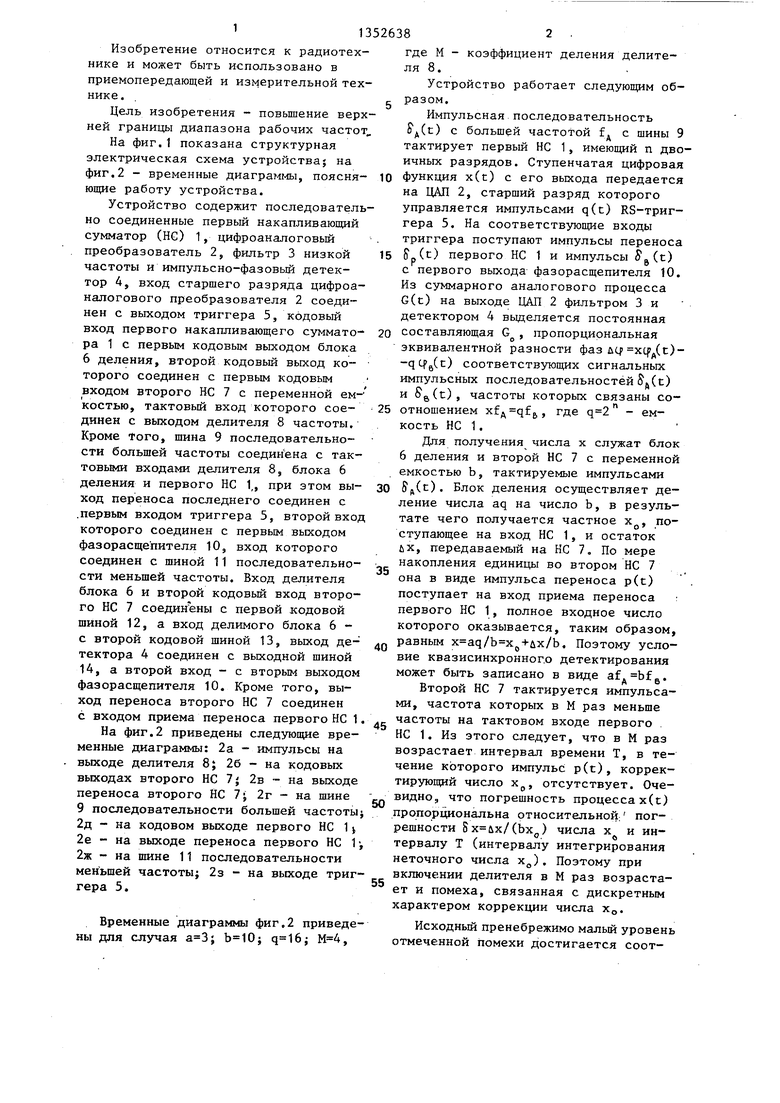

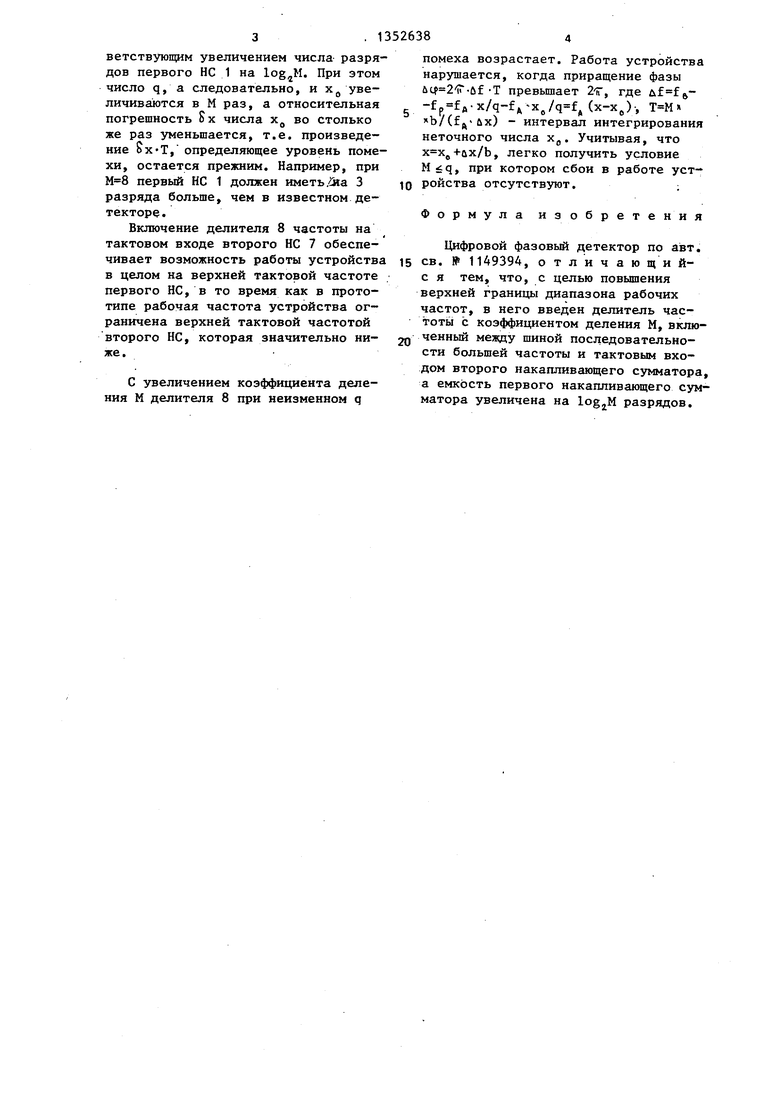

На фиг,1 показана структурная электрическая схема устройства; на фиг.2 - временные диаграммы, поясняющие работу устройства.

Устройство содержит последовательно соединенные первый накапливающий сумматор (HG) 1, цифроаналоговый преобразователь 2, фильтр 3 низкой частоты и импульсно-фазовый детектор 4j вход старшего разряда цифроа- налогового преобразователя 2 соединен с выходом триггера 5, кодовый вход первого накапливающего сумматора 1 с первым кодовым выходом блока 6 деления, второй кодовый вькод которого соединен с первым кодовым входом второго НС 7 с переменной ем- костью, тактовый вход которого соединен с выходом делителя 8 частоты. Кроме Того, шина 9 последовательности большей частоты соединена с тактовыми входами делителя 8, блока 6 деления и первого НС 1,, при этом выход переноса последнего соединен с .первым входом триггера 5, второй вход которого соединен с первым выходом фазорасщепителя Ю, вход которого соединен с шиной 11 последовательности меньшей частоты. Вход делителя блока 6 и второй кодовьш вход второго НС 7 соединены с первой кодовой шиной 12, а вход делимого блока 6 - с второй кодовой шиной 13, выход де- тектора 4 соединен с выходной шиной 14, а второй вход - с вторым выходом фазорасщепителя 10. Кроме того, выход переноса второго НС 7 соединен с входом приема переноса первого НС 1.

На фиг.2 приведены следующие временные диаграммы: 2а - импульсы на выходе делителя 8j 26 - на кодовых выходах второго НС 7j 2в - на выходе переноса второго НС 7j 2г - на шине 9 последовательности большей частоты; 2д - на кодовом выходе первого НС 1j 2е - на выходе переноса первого НС 1 2ж - на шине 11 последовательности меньшей частоты; 2з - на выходе триггера 5.

Временные диаграммы фиг.2 приведены для случая ,

где М - коэффициент деления делителя 8.

Устройство работает следующим об- разом.

Импульсная последовательность Е дСг) с большей частотой д с шины 9 тактирует первый НС 1, имеющий п двоичных разрядов. Ступенчатая цифровая функция x(t) с его выхода передается на ЦАП 2, старший разряд которого управляется импульсами q(c) КЗ-триггера 5. На соответствующие входы триггера поступают импульсы переноса первого НС 1 и импульсы

5

0

5

0

5

0

5

0

5

y,(t)

fp(c)

с первого выхода фазорасщепителя 10. Из суммарного аналогового процесса G(t) на выходе ЦАП 2 фильтром 3 и детектором 4 вьщеляется постоянная составляющая G, пропорциональная эквивалентной разности фаз UQI xcf(t)- -qcpg(c) соответствующих сигнальных импульсных последовательностей ) и S(t ) , частоты которых связаны соотношением ,, где - емкость НС 1.

Для получения числа х служат блок 6 деления и второй НС 7 с переменной емкостью Ь, тактируемые импульсами ). Блок деления осуществляет деление числа aq на число Ь, в результате чего получается частное х, поступающее на вход НС 1, и остаток UX, передаваемый на НС 7. По мере накопления единицы во втором НС 7 она в виде импульса переноса p(t) поступает на вход приема переноса : первого НС 1, полное входное число которого оказывается, таким образом, равным x aq/b Xp+ux/b. Поэтому условие квазисинхронног.о детектирования может быть записано в виде .

Второй НС 7 тактируется импульсами, частота которых в М раз меньше частоты на тактовом входе первого НС 1. Из этого следует, что в М раз возрастает интервал времени Т, в течение которого импульс; p(t), корректирующий число Xj,, отсутствует. Очевидно,, что погрешность процессаx(t) пропорциональна относительной; погрешности (bXg) числа X и интервалу Т (интервалу интегрирования неточного числа х). Поэтому при включении делителя в М раз возрастает и помеха, связанная с дискретным характером коррекции числа XQ.

Исходный пренебрежимо малый уровень отмеченной помехи достигается соответствующим увеличением числа разрядов первого НС 1 на . При этом число q, а следовательно, и х увеличиваются в М раз, а относительная погрешность Sx числа х во столько же раз уменьшается, т.е. произведение Sx T, определяющее уровень помехи, остается прежним. Например, при первый НС 1 должен иметь . 3 разряда больше, чем в известном детекторе.

Включение делителя 8 частоты на тактовом входе второго НС 7 обеспечивает возможность работы устройств в целом на верхней тактовой частоте первого НС, в то время как в прототипе рабочая частота устройства ограничена верхней тактовой частотой второго НС, которая значительно ниже.

С увеличением коэффициента деления М делителя 8 при неизменном q

помеха возрастает. Работа устройства нарушается, когда приращение фазы йч 2 и -й -Т превьш1ает 2т, где л -fp fдx/q-fд x„/q f (х-х)-, () - интервал интегрирования неточного числа х. Учитывая, что x Xg+ux/b, легко получить условие М iq, при котором сбои в работе устройства отсутствуют.;

Формула изобретения

Цифровой фазовый детектор по авт.

св. № 1149394, отличающий- с я тем, что, с целью повышения верхней границы диапазона рабочих частот, в него введен делитель частоты с коэффициентом деления М, включенный между шиной последовательности большей частоты и тактовым входом второго накапливающего сумматора, а емкость первого накапливающего сумматора увеличена на logj,M разрядов.

Редактор И.Рыбченко

Составитель С.Будович Техред Л. Сердюкова

-Заказ 5576/56Тираж 900Подписное

ВНИИШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул,Проектная,4

Корректор В.Гирияк

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовый детектор | 1982 |

|

SU1149394A1 |

| Синтезатор частот | 1985 |

|

SU1254576A1 |

| Синтезатор частот | 1987 |

|

SU1478327A1 |

| Синтезатор частот | 1985 |

|

SU1256133A1 |

| МНОГОЧАСТОТНЫЙ ФАЗОЦИФРОВОЙ ДЕТЕКТОР | 1988 |

|

RU2040851C1 |

| Синтезатор частот | 1986 |

|

SU1337990A1 |

| Синтезатор частот | 1987 |

|

SU1431034A1 |

| Делитель-синтезатор частот | 1982 |

|

SU1149395A1 |

| Цифровой фазовый детектор для синтезаторов частот | 1988 |

|

SU1539677A1 |

| Дробно-пропорциональный преобразователь частот | 1987 |

|

SU1626383A1 |

Изобретение относится к радиотехнике и может быть использовано в приемопередающей-; и измерительной аппаратуре. Целью изобретения является повьппение верхней границы диапазона рабочих частот. Дня достиже - ния поставленной цепи в цифровой фазовый детектор дополнительно введен делитель частоты 8, а емкость первого накапливающего сумматора 1 увеличена на logjM разрядов, где М - коэффициент деления. Устройство содержит накапливающие сумматоры 1 и 7, цифроаналоговый преобразователь 2, фильтр 3 низкой частоты, имиульсно- фазовый детектор 4, триггер 5, блок 6 деления, пшну 9 последовательности большей частоты,фазорасщепитель 10, шину 11 последовательности меньшей частоты, кодовые шины 12 и 13, выходную шину 14. Включение делителя частоты 8 на тактовом входе второго накапливающего сумматора 7 обеспечи- § вает возможность работы устройства на верхней частоте первого накапливающего сумматора. 2 ил. (О

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1149394A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-11-15—Публикация

1985-12-02—Подача