Изобретение относится к вычислительной технике и может быть использовано в ЭВМ.

Цель изобретения - упрощение комбинационного сумматора

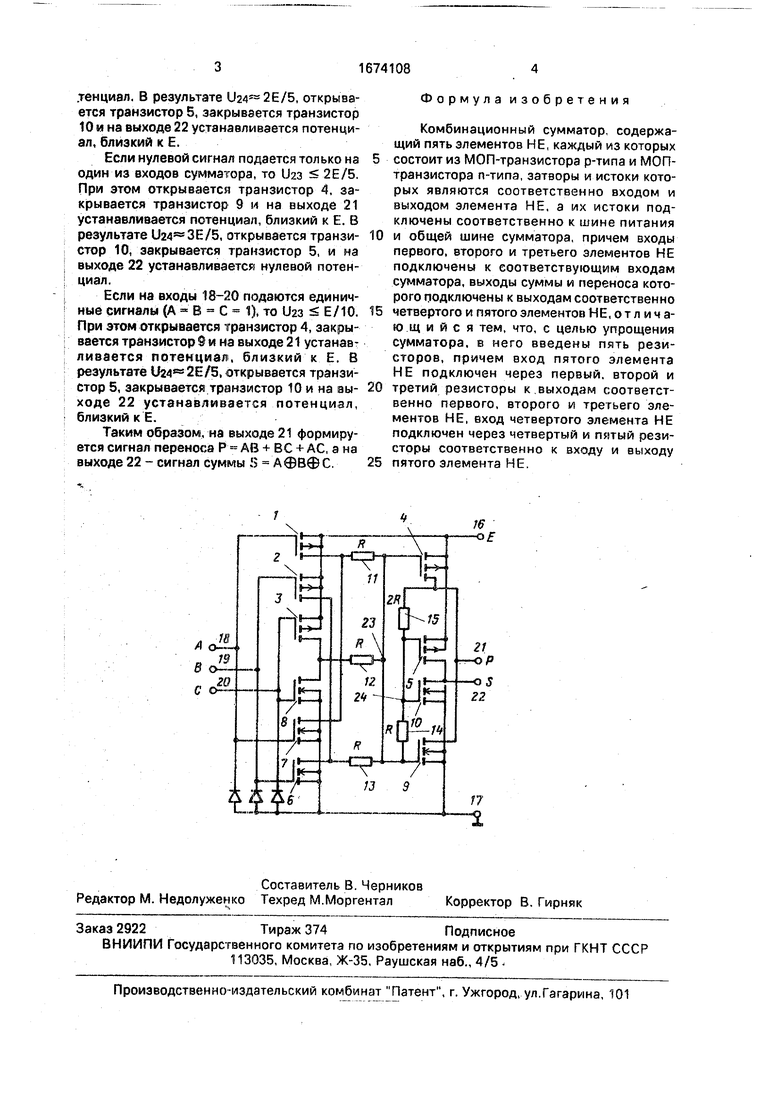

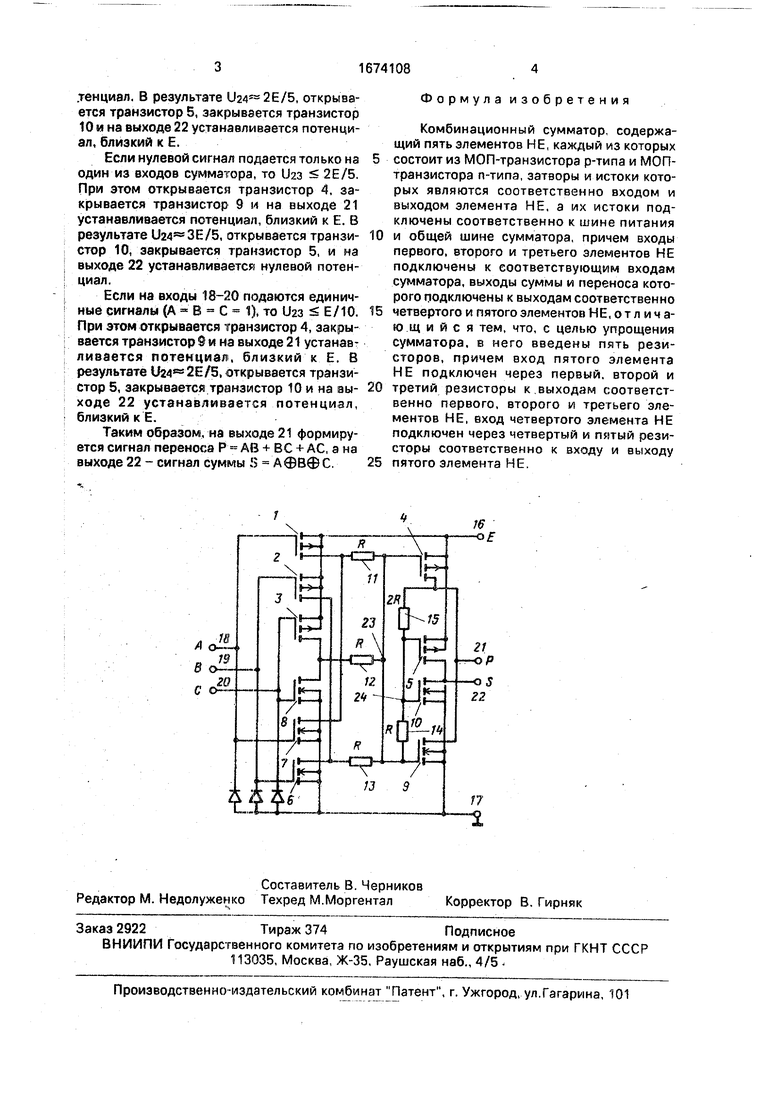

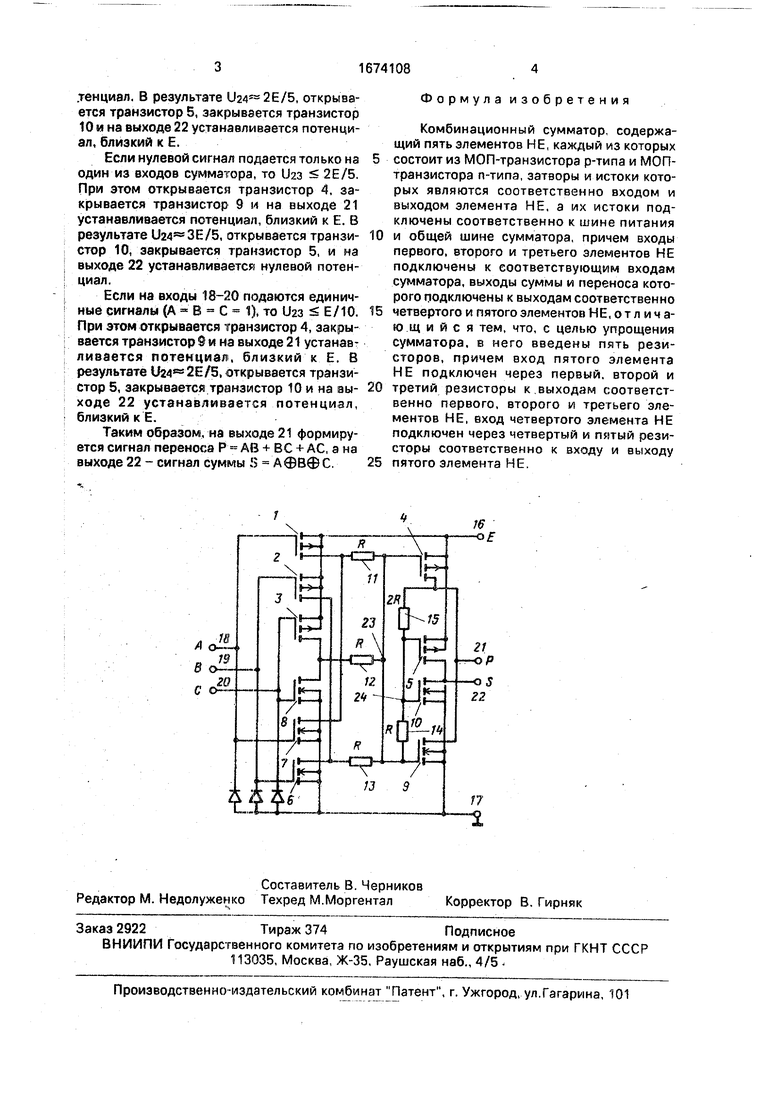

На чертеже представлена схема комбинационного сумматора.

Сумматор содержит МОП транзисторы р-типа 1-5 и п-типа 6-10, образующие пять элементов НЕ, резисторы 11-15, подключен к шине питания 16 и общей шине 17, имеет входы слагаемых 18-20, выходы переноса 21 и суммы 22.

Сумматор работает следующим образом.

Входные слагаемые А, В, С поступают с входов 18-20 сумматора на входы соответствующих элементов НЕ, образованных транзисторами 1-3 и 6-8. Номиналы резисторов 11-15 соотносятся как R.R:R:R:2R и значительно превышают сопротивления каналов открытых транзисторов п-типа и р-типа. Поэтому на стоках транзисторов, являющихся выходами элементов НЕ, устанавливаются потенциалы,близкие к напряжению питания Е, если на входы элементов НЕ подаются потенциалы меньшие Е/2, или к нулю, если на входах элементов НЕ потенциалы большие Е/2.

Если на входы 18-20 подаются нулевые сигналы (А В С 0), то с помощью делителя напряжения, реализованного на резисторах 11-15, в узле 23 сумматора устанавливается потенциал U23 9Е/10. В результате транзистор 4 закрывается, транзистор 9 открывается, и на выходе 21 устанавливается нулевой потенциал, а в узле 24 - потенциал U24 ЗЕ/5, При этом транзистор 5 закрывается, транзистор 10 открывается и на выходе 22 устанавливается нулевой потенциал.

Если нулевой сигнал подается на два входа сумматора (например, А В О, С 1), то U23 ЗЕ/5. При этом открывается транзистор 9, закрывается транзистор 4 и на выходе 21 устанавливается нулевой поЁ

О х|

N

О 00

тенциал, В результате U24-2E/5, открывается транзистор 5, закрывается транзистор 10 и на выходе 22 устанавливается потенциал, близкий к Е.

Если нулевой сигнал подается только на один из входов сумматора, то U23 2Е/5. При этом открывается транзистор 4, закрывается транзистор 9 и на выходе 21 устанавливается потенциал, близкий к Е. В результате U24sas3E/5. открывается транзистор 10, закрывается транзистор 5, и на выходе 22 устанавливается нулевой потенциал.

Если на входы 18-20 подаются единичные сигналы (А В С 1), то Угз Е/10. При этом открывается транзистор 4, закрывается транзистор 9 и на выходе 21 устанав- ливается потенциал, близкий к Е. В результате , открывается транзистор 5, закрывается транзистор 10 и на выходе 22 устанавливается потенциал, близкий к Е.

Таким образом, на выходе 21 формируется сигнал переноса Р АВ + В С + АС, а на выходе 22 - сигнал суммы S АфВфС.

Формула изобретения

Комбинационный сумматор, содержащий пять элементов НЕ, каждый из которых

состоит из МОП-транзистора р-типа и МОП- транзистора n-типа, затворы и истоки которых являются соответственно входом и выходом элемента НЕ, а их истоки подключены соответственно к шине питания

и общей шине сумматора, причем входы первого, второго и третьего элементов НЕ подключены к соответствующим входам сумматора, выходы суммы и переноса которого подключены к выходам соответственно

четвертого и пятого элементов НЕ.отлича- ю щ и и с я тем, что, с целью упрощения сумматора, в него введены пять резисторов, причем вход пятого элемента НЕ подключен через первый, второй и

третий резисторы к выходам соответственно первого, второго и третьего элементов НЕ, вход четвертого элемента НЕ подключен через четвертый и пятый резисторы соответственно к входу и выходу

пятого элемента НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный сумматор | 1988 |

|

SU1596321A1 |

| Комбинационный сумматор | 1987 |

|

SU1543399A1 |

| Комбинационный сумматор | 1988 |

|

SU1527630A1 |

| Одноразрядный сумматор | 1986 |

|

SU1325465A1 |

| Одноразрядный сумматор | 1987 |

|

SU1509874A1 |

| Одноразрядный сумматор | 1986 |

|

SU1432504A1 |

| Устройство для умножения по модулю 2 @ -1 @ | 1985 |

|

SU1304018A1 |

| Устройство для геоэлектроразведки | 1985 |

|

SU1343378A1 |

| Цифровой генератор функций | 1986 |

|

SU1324092A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1363248A1 |

Изобретение относится к области вычислительной техники и может быть использовано в ЭВМ. Целью изобретения является упрощение комбинационного сумматора. Сумматор содержит МОП-транзисторы P-типа 1 - 5 и N-типа 6 - 10, резисторы 11 - 15, подключен к шине питания 16 и общей шине 17, имеет входы слагаемых 18 - 20, выходы переноса 21 и суммы 22. Поставленная цель достигается введением в сумматор пяти резисторов, выполняющих функции делителя напряжения. 1 ил.

| Патент США № 3609329 | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| COS/MOS Digital Integrated Circuits | |||

| RCA Solid State Databooks, Somervllle, N.Y., USA, 1974, p | |||

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

Авторы

Даты

1991-08-30—Публикация

1988-08-11—Подача