рой регистр 10, мультиплексор 11, дешифратор 12, блок 13 формирования признаков, генератор 14 импульсов. Цель изобретения достигается введением дешифратора, блока синхронизации, блока установки, формирователей им1

Изобретение относится к автоматике и вычислительной технике и может быть исйользовано в иерархических многоканальных системах контроля в качестве устройства управления и конт роля многоканальных объектов.

Цель изобретения - расширение функциональных возможностей устройства и повьшение достоверности контроля.

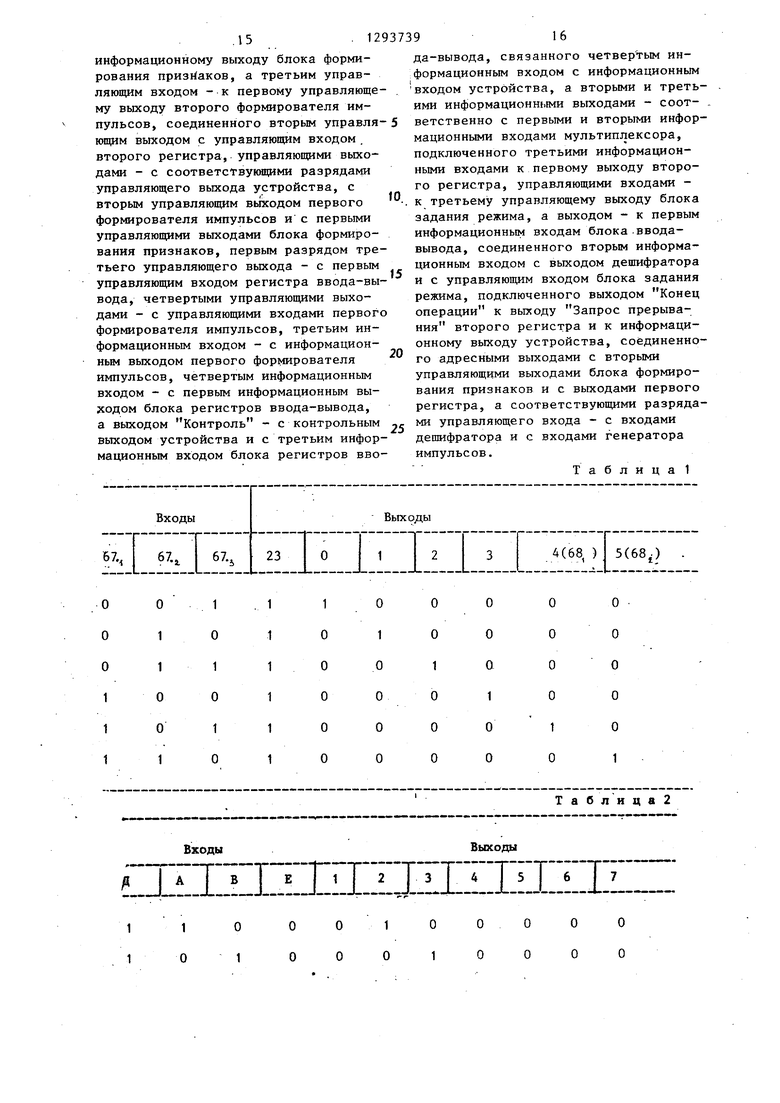

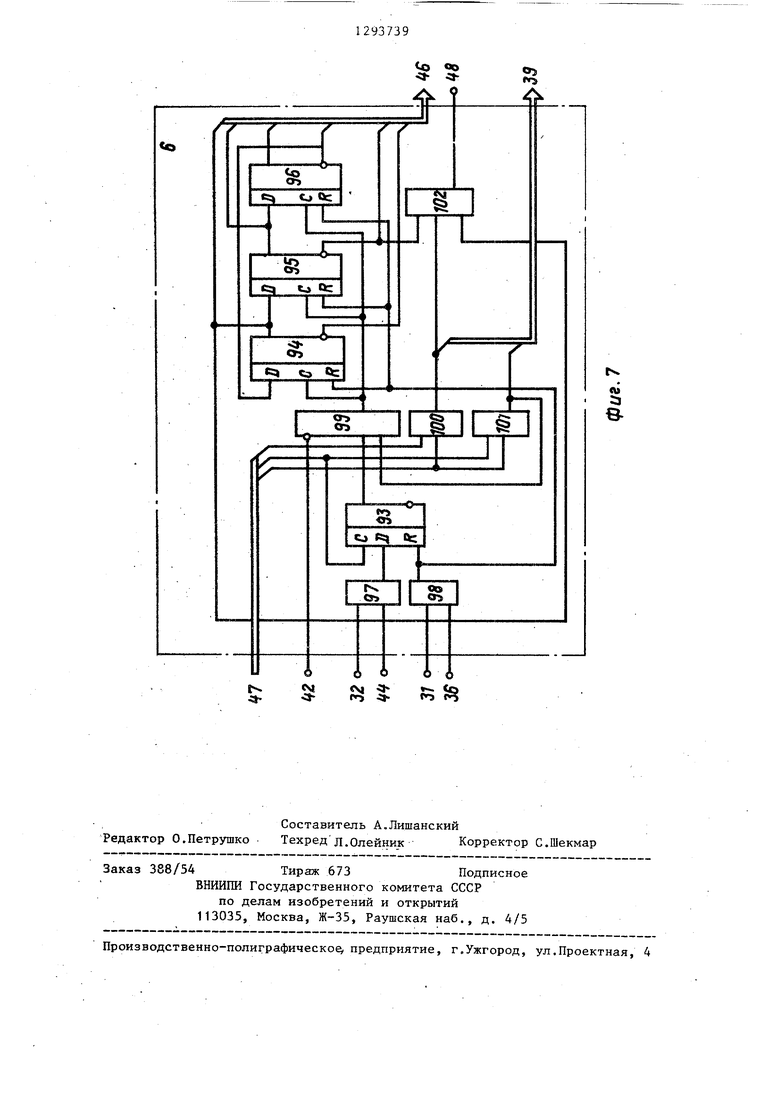

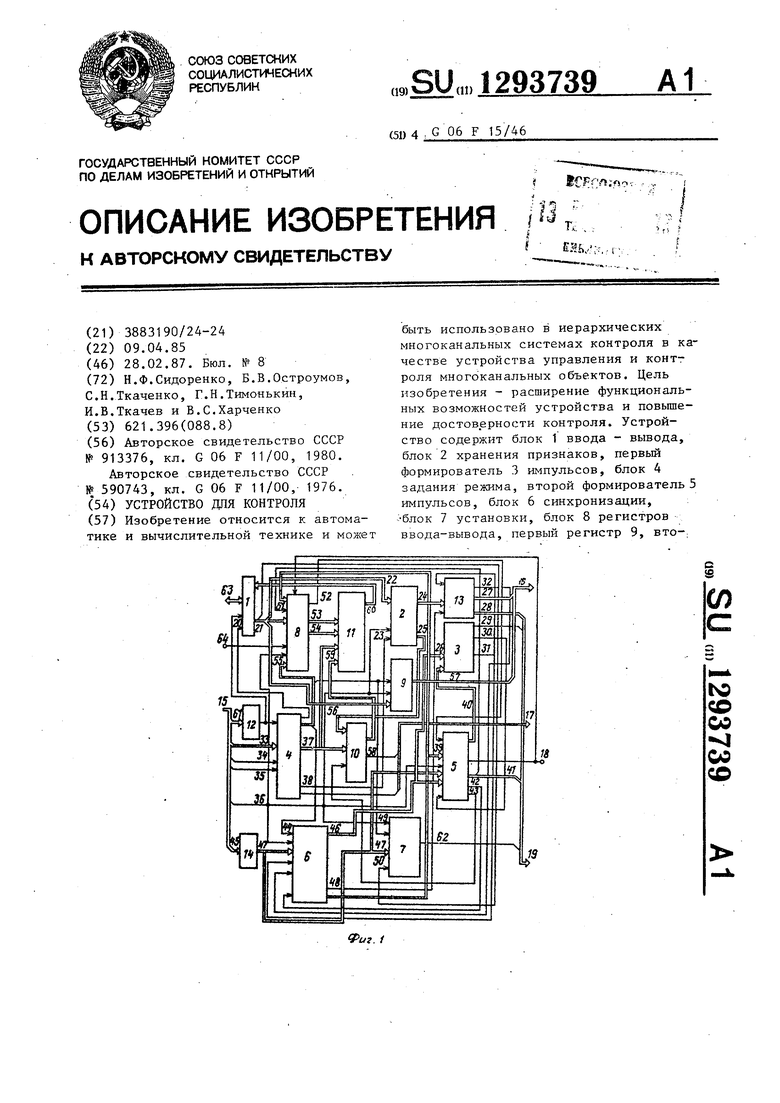

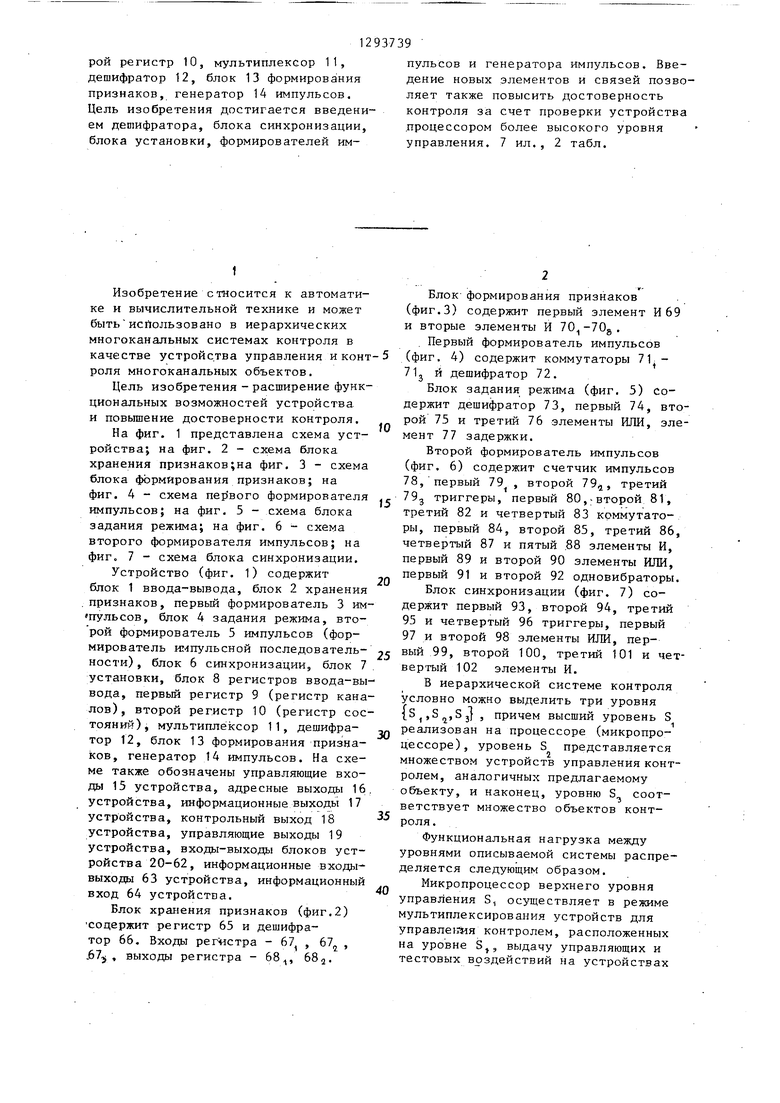

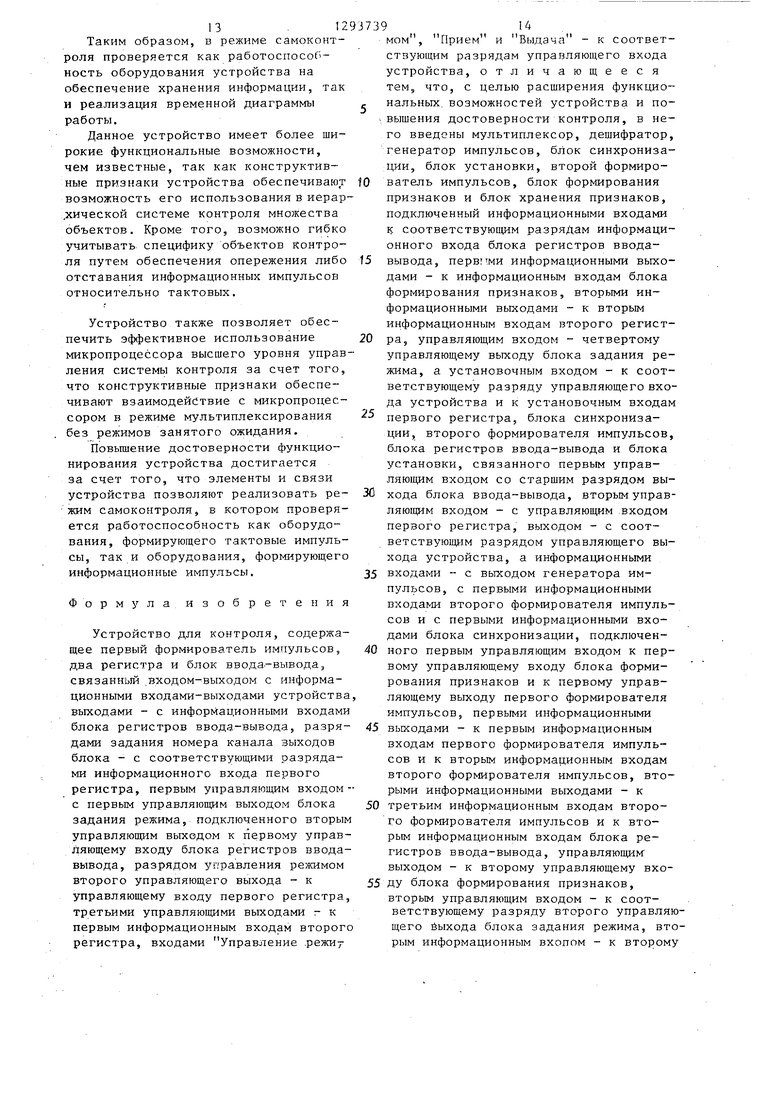

На фиг. 1 представлена схема устройства; на фиг. 2 - схема блока хранения признаков;на фиг. 3 - схема блока формирования признаков; на фиг, 4 - схема пер вого формирователя импульсов; на фиг. 5 - схема блока задания режима; на фиг. 6 - схема второго формирователя импульсов; на фиг. 7 - схема блока синхронизации.

Устройство (фиг. 1) содержит блок 1 ввода-вывода, блок 2 хранения .признаков, первый формирователь 3 им пульсов, блок 4 задания режима, вто- рой формирователь 5 импульсов (формирователь и:-1пульсной последовательности) , блок 6 синхронизации, блок 7 установки, блок 8 регистров ввода-вывода, первый регистр 9 (регистр каналов), второй регистр 10 (регистр состояний), мультиплексор 11, дешифратор 12, блок 13 формирования признаков, генератор 14 импульсов. На схеме также обозначены управляющие входы 15 устройства, адресные выходы 16 устройства, информационные выходы 17 устройства, контрольный выход 18 устройства, управляющие выходы 19 устройства, входы-выходы блоков устройства 20-62, информационные входы- выходы 63 устройства, информационный вход 64 устройства.

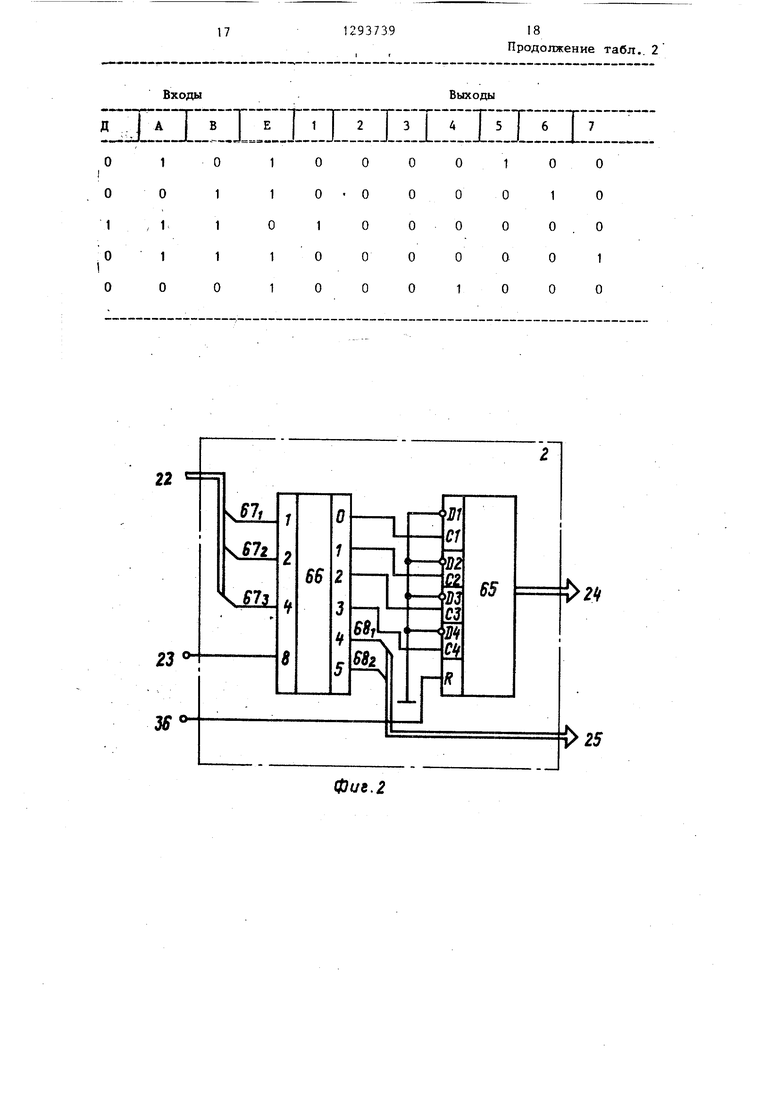

Блок хранения признаков (фиг.2) Содержит регистр 65 и дешифратор 66. Входы регистра - 67 , 67 , Ы- , выходы регистра - 68.,, 68.

пульсов и генератора импульсов. Введение новых элементов и связей позволяет также повысить достоверность контроля за счет проверки устройства .процессором более высокого уровня управления. 7 ил., 2 табл.

5

fO

15

20

25

30

35

40

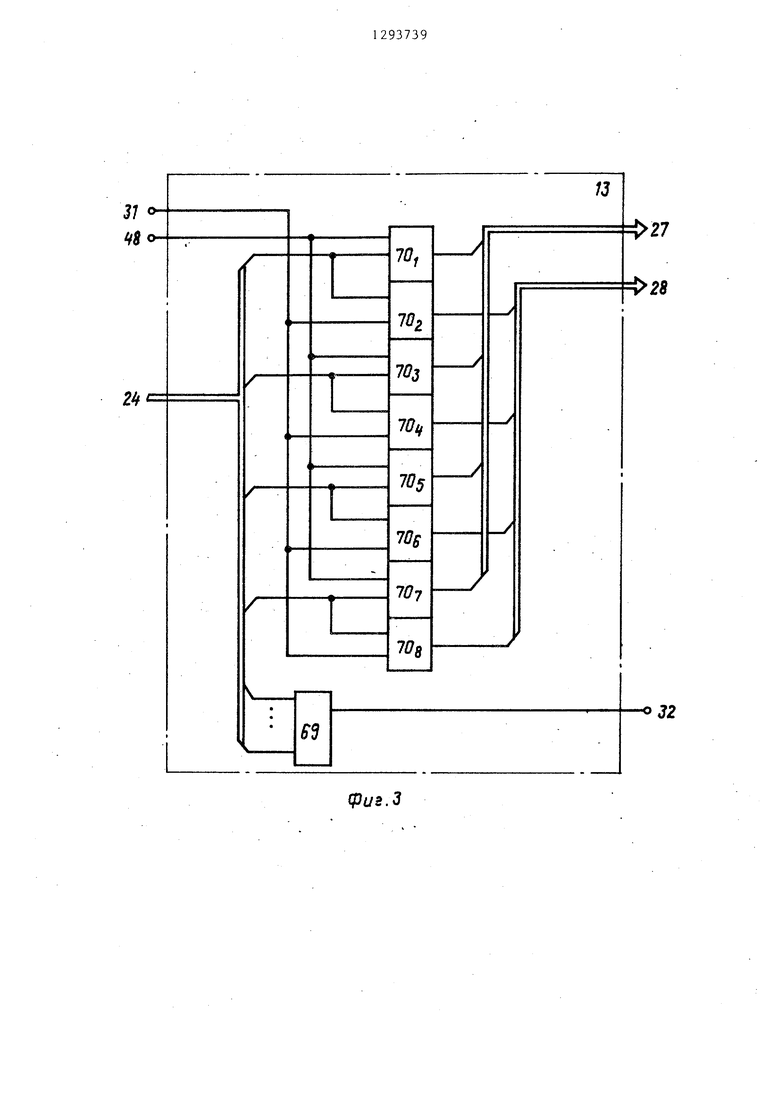

Блок формирования признаков (фиг.З) содержит первый элемент И 69 и вторые элементы И 70 70g.

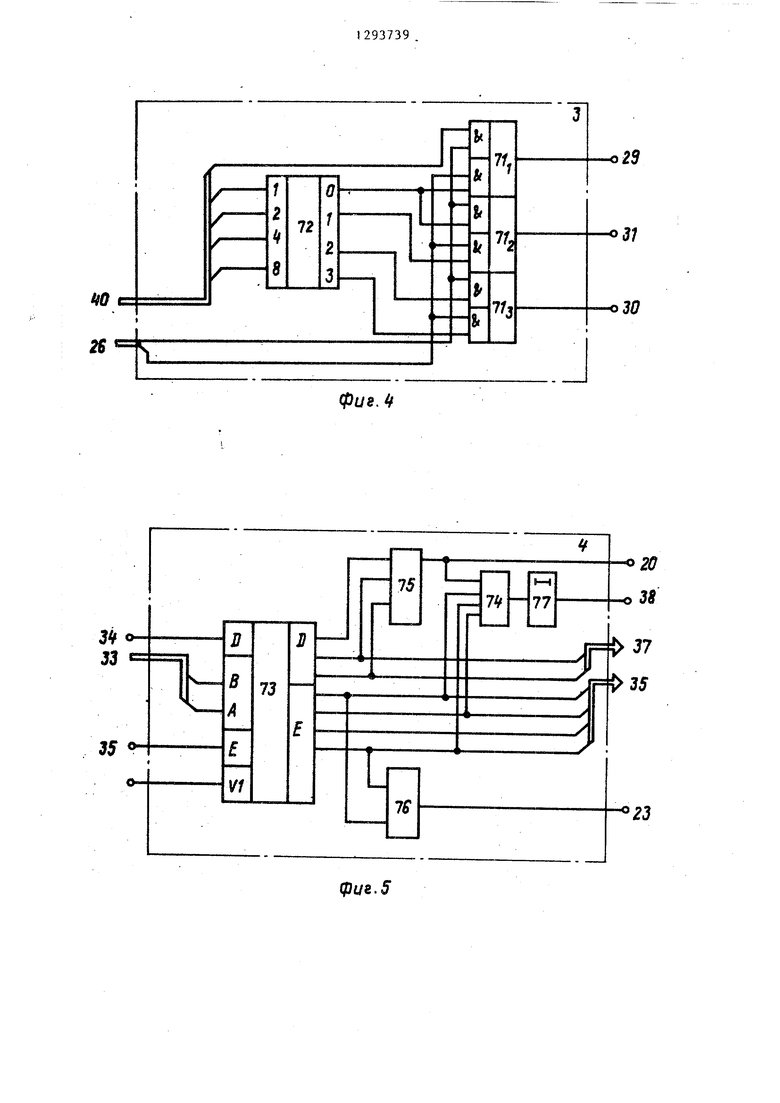

Первый формирователь импульсов (фиг. 4) содержит коммутаторы 71j и дешифратор 72.

Блок задания режима (фиг. 5) содержит дешифратор 73, первый 74, второй 75 и третий 76 элементы ИЛИ, элемент 77 задержки.

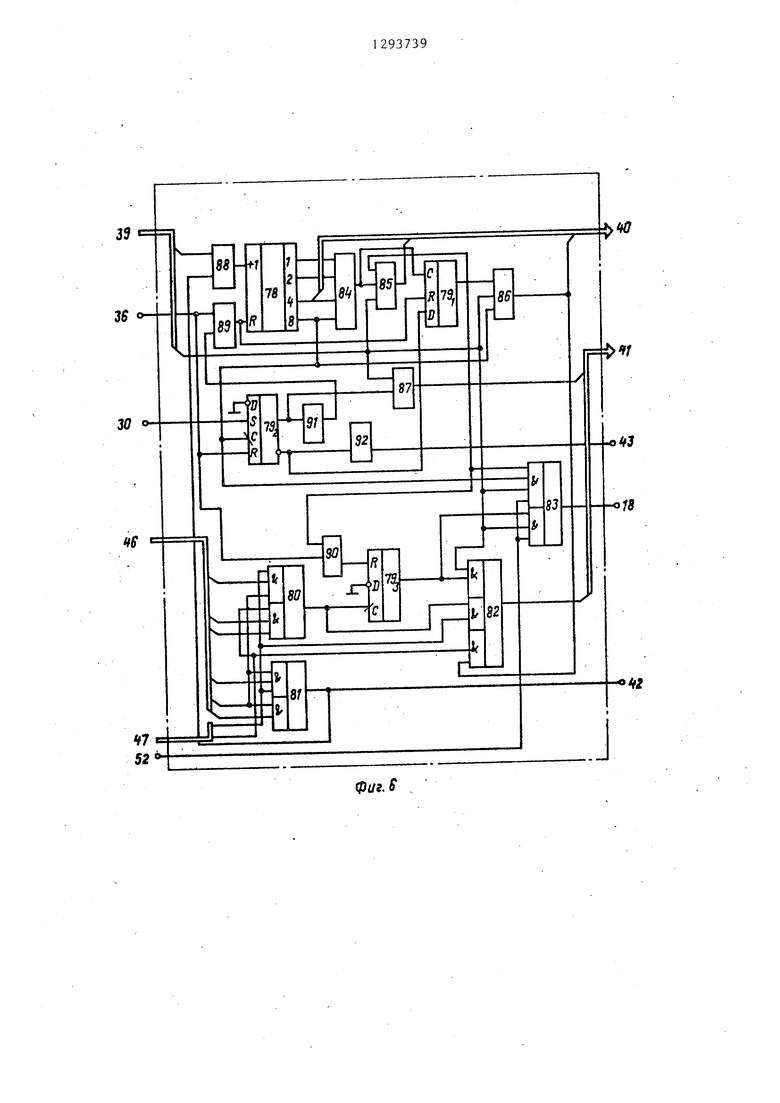

Второй формирователь импульсов (фиг. 6) содержит счетчик импульсов 78, первый 79 , второй 79,, третий 79 триггеры, первый 80,-второй 81, третий 82 и четвертый 83 крммутато- ры, первый 84, второй 85, третий 86, четвертый 87 и пятый .88 элементы И, первый 89 и второй 90 элементы ИЛИ, первый 91 и второй 92 одновибраторы.

Блок синхронизации (фиг. 7) содержит первый 93, второй 94, третий 95 и четвертый 96 триггеры, первый 97 и второй 98 элементы ИЛИ, первый 99, второй 100, третий 101 и четвертый 102 элементы И.

В иерархической системе контроля условно можно выделить три уровня {S,S,Sj , причем высший уровень S реализован на процессоре (микропроцессоре), уровень S представляется множеством устройств управления контролем, аналогичных предлагаемому объекту, и наконец, уровню S соответствует множество объектов контроля .

Функциональная нагрузка между уровнями описываемой системы распределяется следующим образом.

Микропроцессор верхнего уровня управления S, осуществляет в режиме мультиплексирования устройств для управле}йия контролем, расположенных на уровне Б,, выдачу управляющих и тестовых воздействий на устройствах

уровня Sj. Кроме того, микропроцессор уровня S принимает также в режиме мультиплексирования информацию от устройств уровня S о состоянии (сигналы реакций), объектов контроля уров- 5 ня SA и о собственном состоянии устройств уровня S в режиме их проверки

ts

и осуществляет ее обработку.

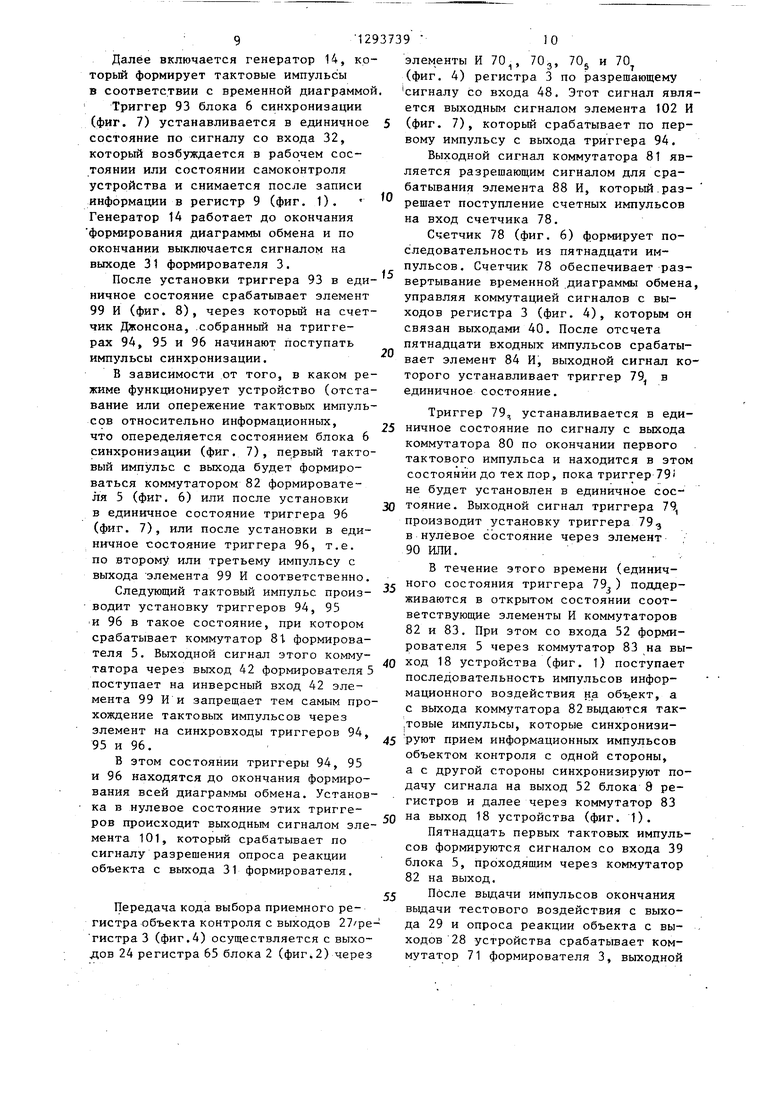

Работа дешифратора 66 блока 2 хранения признаков характеризуется табл. истинности.

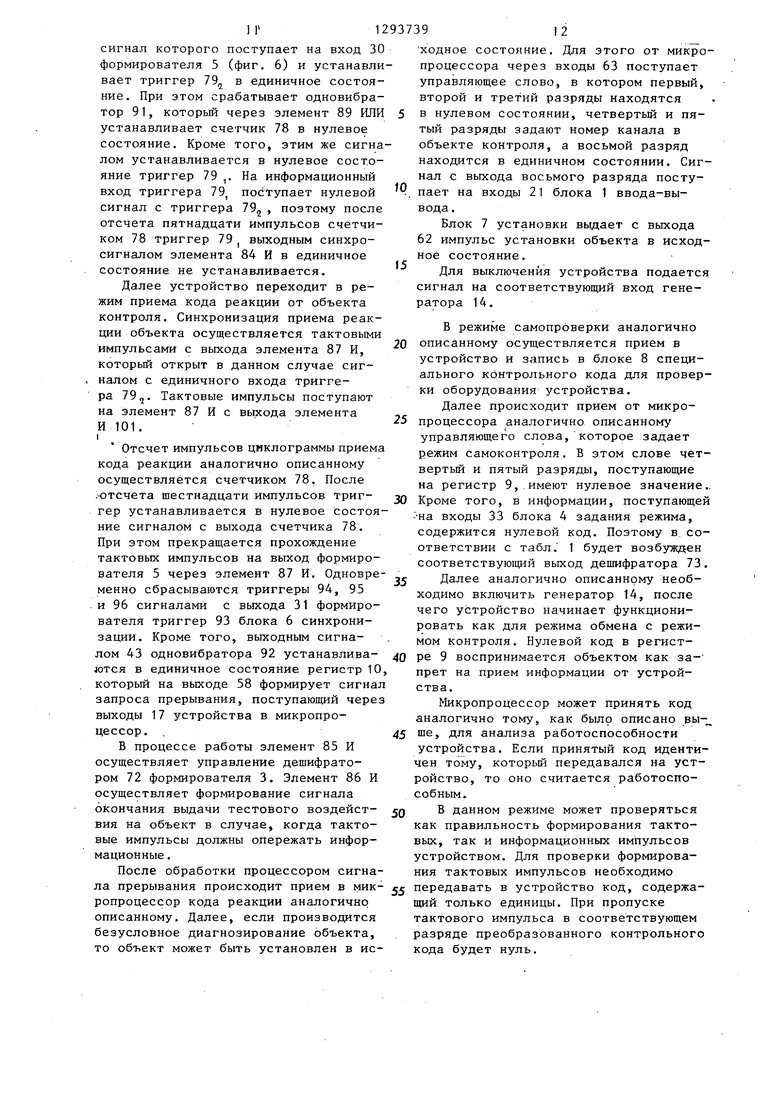

Алгоритм работы дешифратора 73 задается следующей табл. 2.

Устройство работает следующим образом.

Рассмотрим принцип функционирования устройства, которое работает в следующих режимах: обмен информацией с внешним управляющим устройством (например, микропроцессором); обмен информацией с объектом контроля; самопроверка.

В первом режиме происходит обмен информацией между данным устройством и микропроцессором через группу вхо- дор-выходов 63 устройства (фиг. 1).

При этом после опознавания адреса устройства дешифратором 12 его выходной сигнал инициирует блок 4 задания

to

ляющий микропроцессор (К580ИК80) является байтовым, то обмен шестнадцатиричными кодами происходит побайтно, т.е. шестнадцатиричный код принимает7 ся в два приема.

Поэтому только после приема младшего -И старшего байтов снимается сигнал запроса прерывания с выхода 58 регистра 10.

При выдаче информации из регистра 10 с выходов 59 осуществляется выдача кода состояния устройства через мультиплексор 11 и далее через блок 1 ввода-вывода на выходы 63 устройства.

Во втором режиме осуществляется обмен информацией между устройством и объектом контроля, а также программная установка и сброс блока 10.

В данном режиме работа устройства определяется управляющим словом, поступающим через группу входов 63 от микропроцессора. Управляющее слово поступает с выходов 22 блока 1 (фиг. 1) на блок 2 хранения признаков и с выходов 56 на входы регистра 9 каналов.

20

25

В формате управляющего слова сорежима, на выходе 38 которого -под воз-30 держится 8 разрядов. В трех младших действием сигналов Прием и Выдача Разрядах (ДО, Д1 , Д2) , содержится соответственно на входах 34 и 35 с за- информация о номере, приемного регист- держкой на время реакции на заданную Ра объекта контроля или.о состоянии

микропроцессором операцию формируется сигнал конца операции. Этот сигна поступает через соответствующий разряд выходов 17 на микропроцессор и воспринимается им как признак сигнала Ответ.

Кроме того, по указанным сигналам осуществляется формирование сигналов управляющих блоком 8 регистров, регистром 10 состояний и мультиплексором 11 (фиг. 4).

При приеме информации от микропроцессора данные через входы 63, блок 1 ввода записываются в регистры блока 8.

При передаче данных в микропроцессор для анализа происходит выборка их с выходов 53 и 54 регистров блока 8 через мультиплексор 11, его вы- ходы 60 и блок ввода-вывода на выходы 63 устройства.

Обмен, информацией между данным . устройством и микропроцессором осуществляется шестнадцатиричными кодами. При этом ввиду того, что управ5

ts

to

293739 4

ляющий микропроцессор (К580ИК80) является байтовым, то обмен шестнадцатиричными кодами происходит побайтно, т.е. шестнадцатиричный код принимает7 ся в два приема.

Поэтому только после приема младшего -И старшего байтов снимается сигнал запроса прерывания с выхода 58 регистра 10.

При выдаче информации из регистра 10 с выходов 59 осуществляется выдача кода состояния устройства через мультиплексор 11 и далее через блок 1 ввода-вывода на выходы 63 устройства.

Во втором режиме осуществляется обмен информацией между устройством и объектом контроля, а также программная установка и сброс блока 10.

В данном режиме работа устройства определяется управляющим словом, поступающим через группу входов 63 от микропроцессора. Управляющее слово поступает с выходов 22 блока 1 (фиг. 1) на блок 2 хранения признаков и с выходов 56 на входы регистра 9 каналов.

20

25

В формате управляющего слова со

триггера маски прерывания. Эти разряды подключены к выходам 22 блока ввода-вывода.

Разряды ДЗ и Д4 управляющего слова определяют номер проверяемого канала объекта контроля. Эта информация с выходов 56 блока 1 записывается

в регистр 9.

Разряды Д5 и Д6 управляющего слова в данном режиме не используется и является резервными.

Старший разряд Д7 управляет формированием сигнала установки объекта контроля с выхода 62 блока 7 установки. Значение сигнала разряда Д7 снимается с выхода 50 блока 1 ввода-вывода.

Информация поступает в объект контроля и принимается от него в последовательном коде.

В третьем режиме осуществляется

самопроверка устройства без вьщачи информации в объект контроля. В этом случае блоком 4 задания режима вырабатываются сигналы, определяюЕцие режим самоконтроля,

51

Сигналом с выхода 44 блока 4 задания режима в блоке 6 инициируется отработка .режима самопроверки. При этом происходит передача информации с выхода блока 8 регистров на его вход. В данном случае после окончания указанной перезаписи информации формируется сигнал запроса прерывания на выходе 58 регистра 10,

.Цля предотвращения передачи информации самоконтроля в объект в регистр 9 каналов (фиг,, t) с помощью управляющего слова записываются ну

ли, вследствие чего входы объекта блокируются.

Работоспособность устройства устанавливается по наличию неискаженной информации в регистрах блока 8 и формированию сигнала запроса прерыЕ:ания на выходе 58 регистра 10.

Особенностью устройства является то, что перечисленные режимы могут выполняться устройством в определенном порядке.

Рассмотрим примеры функционирования устройства в каждом из указанных режимов.

Прием информадии устройством от ьшкропроцессора осуществляется следующим образом.

В исходном состоянии в.се элементы памяти блоков устройства устанавливаются в исходное состояние сигналом со входа 36 устройства.

Далее устройст во осуществ.чяет прием информадии в блок 8 регистров, При этом на входы 15 устройства (фиг о 1) пос тупгтю г следугаядие сигналь на входы разрядов 61 - собстненньп адрес устройства, на входы 33 разрядов код задания режима работы, на вход 35 поступает сипол Выдача от микропроцессора.

Поэтому в устройс1 ве и случае опознания собственного адреса срабатывает дешифратор 2, выходной сигнал которого поступает на соответствующи вход блока 1 ввода-вывода и готовит данные для передачи их с входов 63 на входы 21 блока 1 ввода-выхода.

На входы дешифратора 73 блока 4 задания режима (фяг, 5) в данном случае поступает набор сигналов,. соответствующий третьему набору в табл.2 Поэтомз дешифратор 73 выдает сигнал на соответствующем разряде выхода, (который поступае - через выходы 55 на ЮДИН из входов блока 8. . обеспечивг я

0

5

тем самым запись младшего байта информации со входов 21 в блок 8 регистров ввода-вывода о

После осуществления записи в регистр с выхода 38 элемента 77 задержки блока 4 (фиг. 5) выдается на микропроцессор сигнал окончания выполнения операции (или сигнал Ответ по терминологии, принятой при описании микропроцессора типа К580ИК80). После получения указанного сигнала микропроцессор может в случае необходи- мости отключиться от данного устройства для взаимодействия с другим устройством.

Снимается сигнал со входа 35 блока 4 задания режима (фиг. 1,5), вследствие чего сигнал на выходе 38 также принимает нулевое значение.

После приема в устройство младшего байта информации осуществляется прием старшего байта.

Прием старшего байта осуществляется так же, как и младшего байта через входц 63 устройства. Отличие заключается в том, что в рассматриваемом случае на входы дешифратора 73 блока 4 задания режима (фиг. 5) поступает набор сигналов, соответствую- пщй четвертому набору табл. 2.

Поэтому зозбужденньгм оказывается шестой разряд выхода дешифратора 73 и соответствую1дий ему вход блока 8 регистров и соответствующий регистр. 35 Далее процесс приема информации полностью аналогичен описанному выше для мл адш е г о байта.

После завершения приема информации в устройство От микропроцессора может производиться самопроверка устройства, передача информации в объект контроля, либо передача информации в микропроцессор для анализа. Порядок работы устройства определяется управ0

25

30

40

45

ляЕощими сиг налами, которые поступают

на входы устройства.

I

Передача информации в микропроцессор из устройства через выходы 63

осуществляется следующ гм образом.

На входы 61 дешифратора 12 (фиг.1) поступает соответствующий адрес устройства. Выходной сигнал дешифратора 1 2 разрешает срабатывание дешифра- 7-ора 73 блока 4 задания режима

(фиг.5), на входы 33 и 34 которого поступает набор сигналов, соответствующий первому набору в табл.2. Возбуждается второй разряд выхода деши

712

фратора 73, сигнал с которого через входы-выходы 37 поступает на соответствующий вход регистра 10, который устанавливается в нуль и снимает сигнал с выхода 58 устройства (фиг. 1).

Кроме того этот же сигнал с второго разряда дешифратора 73 Е (фиг. 5) через выходы 37 блока 4 задания режима поступает на соответствующий вход дешифратора 12 и формирует тем самым следующий тракт передачи информации: выходы 54 блока 8 регистров, мультиплексор 11, выходы 60 мультиплексора 11 (фиг. 1), блок 1 ввода-вывода, открытый сигнал с выхода 20 элемента 75 ИЛИ (фиг. 5) блока 4 задания режима, выходы 63 устройства.

В процессе выполнения описанной операции также формируется сигнал окончания выполнения операции на выходе 38 устройства.

Аналогично выполняется передача в микропроцессор старшего байта. Для этого на входы 34 и 33 блока 4 задания режима поступают управляющие сигналы, которые соответствуют второму набору в табл. 1. При этом возбуждается третий разряд выхода дешифратора 73 (фиг. 5), который настраивает мультиплексор 11 на передачу данных с выходов 53 блока 8 регистров ввода-вывода.

Последовательная комбинация двух описанных режимов обмена устройства с микропроцессором может быть использована для проверки работоспособности блоков 1.4,8,11 и 12 устройства путем передачи в устройство контрольного кода и последующего возвра- та его в микропроцессор для анализа искажений.

Особенностью конструкции устройства, определяющей область его применения, является возможность взаимодействия с микропроцессором двумя способами: по обращениям .и по прерываниям.

Рассмотрим работу устройства в режиме проверки объекта контроля.

Данный режим условно может быть подразделен на два подрежима: передача информации на объект контроля и прием кода реакции от объекта.

В режиме передачи информации на объект контроля аналогично описанном осуществляется прием кода тестового воздействия от микропроцессора, и

8

0

5

0

5

запись его в блок 8 регистров ввода- вывода.

Далее устройство осуществляет прием управляющего слова от микропроцес-. сора, которое определяет порядок дальнейшей работы устройства: взаимодействие с объектом либо переход в режим самопроверки.

Управляющее слово принимается ;следующим образом.

На входы 61 поступает соответственный адрес данного устройства, на входы 33 - код 11, а на вход 35 - сигнал выдачи информации микропроцессором, что соответствует шестому набору в табл. 2.

В соответствии с этим возбуждается седьмой разряд выхода дешифратора 73 блока 4 задания режима (фиг.5). Сигналом с выхода дешифратора 12 (фиг. 1) разрешается передача информации со входов 63 устройства на выходы 21 блока 1 ввода-вывода. Информация с выходов 21 блока ввода-вывода распределяется следующим образом: сигналы с выходов трех младших разрядов 17оступают с выходов 21 блока 1 ввода- вывода на соответствующие разряды входов 22 блока 2 хранения признака (фиг. 2), а сигналы с выходов третьего и четвертого разрядов управляющего слова поступают с выходов 21 блока 1 ввода-вывода на -соответств ую- щие разряды входов 56 регистра 9.

1

При этом сигналом, поступающим на вход 49 регистра 9, осуществляется запись в регистр кода выбора канала объекта контроля.

Дешифратор 66 блока 2 (фиг. 2) срабатывает в соответствии с табл. 1 таким образом, что его выходным сигналом осуществляется запись единицы в один из разрядов регистра 65, со5 держимое которого опеределяет номер приемного регистра объекта контроля. С выходов 24 регистра 65 этот код поступает на соответствующие входы формирователя 3 (фиг. 4).

Q Одновременно с этим аналогично

описанному блоком 4 задания режима на выходе 38 формируется сигнал окончания операции, который приводит к соответствующей реакции микропроцес сора.

Далее по сигналу с двух первых разрядов входа 45 задается отставание или опережение тактовых импульсов относительно информационных.

0

5

0

9 129

Далее включается генератор 14, который формирует тактовые импульсы в соответствии с временной диаграммой

Триггер 93 блока 6 синхронизации (фиг. 7) устанавливается в единичное состояние по сигналу со входа 32, который возбуждается в рабочем состоянии или состоянии самоконтроля устройства и снимается после записи информации в регистр 9 (фиг, 1). Генератор 14 работает до окончания формирования диаграммы обмена и по окончании выключается сигналом на выходе 31 формирователя 3.

После установки триггера 93 в единичное состояние срабатывает элемент 99 И (фиг. 8), через который на счетчик Джонсона, .собранный на триггерах 94, 95 и 96 начинают поступать импульсы синхронизации.

В зависимости от того, в каком режиме функционирует устройство (отставание или опережение тактовых импульсов относительно информационных,

что опеределяется состоянием блока 6 синхронизации (фиг. 7), первый тактовый импульс с выхода будет формироваться коммутатором 82 формирователя 5 (фиг. 6) или после установки в единичное состояние триггера 96 (фиг. 7), или после установки в единичное состояние триггера 96, т.е. по второму или третьему импульсу с выхода элемента 99 И соответственно.

Следующий тактовый импульс произ- водит установку триггеров 94, 95 и 96 в такое состояние, при котором срабатывает коммутатор 81. формирователя 5. Выходной сигнал этого коммутатора через выход 42 формирователя 5 поступает на инверсный вход 42 элемента 99 И и запрещает тем самым прохождение тактовых импульсов через элемент на синхровходы триггеров 94, 95 и 96.

В этом состоянии триггеры 94, 95 и 96 находятся до окончания формирования всей диаграммы обмена. Установка в нулевое состояние этих триггеров происходит выходным сигналом элемента 101, который срабатывает по сигналу разрешения опроса реакции объекта с выхода 31 формирователя.

Передача кода выбора приемного регистра объекта контроля с выходов 27/ре гистра 3 (фиг.4) осуществляется с выходов 24 регистра 65 блока 2 (фиг.2) через

o

739

5

0

10

элементы И 70, 7Q, 70 и 70 (фиг. 4) регистра 3 по разрешающему сигналу со входа 48. Этот сигнал является выходным сигналом элемента 102 И (фиг. 7), который срабатывает пхэ первому импульсу с выхода триггера 94.

Выходной сигнал коммутатора 81 является разрешающим сигналом для срабатывания элемента 88 И, которьй.разрешает поступление счетных импульсов на вход счетчика 78.

Счетчик 78 (фиг. 6) формирует последовательность из пятнадцати импульсов. Счетчик 78 обеспечивает развертывание временной диаграммы обмена, управляя коммутацией сигналов с выходов регистра 3 (фиг. 4), которым он связан выходами 40. После отсчета пятнадцати входных импульсов срабатывает элемент 84 И, выходной сигнал которого устанавливает триггер единичное состояние.

79. в

Триггер 79, устанавливается в единичное состояние по сигналу с выхода коммутатора 80 по окончании первого тактового импульса и находится в этом состоянии до тех пор, пока триггер 79 не будет установлен в единичное соетояние. Выходной сигнал триггера 79, производит установку триггера 79 в нулевое состояние через элемент 90 РШИ. .

В течение этого времени (единичного состояния триггера 79) поддерживаются в открытом состоянии соответствующие элементы И коммутаторов 82 и 83. При этом со входа 52 формирователя 5 через коммутатор 83 на выход 18 устройства (фиг. 1) поступает последовательность импульсов информационного воздействия на объ,ект, а с выхода коммутатора 82 выдаются так- .товые импульсы, которые синхронизиРуют прием информационных импульсов объектом контроля с одной стороны, а с другой стороны синхронизируют подачу сигнала на выход 52 блока 8 регистров и далее через коммутатор 83

на выход 18 устройства (фиг. 1).

Пятнадцать первых тактовых импульсов формируются сигналом со входа 39 блока 5, проходящим через коммутатор 82 на выход.

После выдачи импульсов окончания выдачи тестового воздействия с выхода 29 и опроса реакции объекта с выходов 28 устройства срабатывает коммутатор 71 формирователя 3, выходной

сигнал которого поступает на вход 30 формирователя 5 (фиг. 6) и устанавливает триггер 79 в единичное состояние. При этом срабатывает одновибра- тор 91, которьй через элемент 89 ИЛИ устанавливает счетчик 78 в нулевое состояние. Кроме того, этим же сигналом устанавливается в нулевое состояние триггер 79 ,. На информационный вход триггера 79, поступает нулевой сигнал с триггера 79,., , поэтому после отсчета пятнадцати импульсов счетчиком 78 триггер 79, выходным синхросигналом элемента 84 И в единичное состояние не устанавливается.

Далее устройство переходит в режим приема кода реакции от объекта контроля. Синхронизация приема реакции объекта осуществляется тактовыми импульсами с выхода элемента 87 И, который открыт в данном случае сигналом с единичного входа триггера 79,. Тактовые импульсы поступают на элемент 87 И с вьгхода элемента

И 101. I

Отсчет импульсов циклограммы приема

кода реакции аналогично описанному осуществляется счетчиком 78. После /отсчета шестнадцати импульсов триггер устанавливается в нулевое состояние сигналом с выхода счетчика 78. При этом прекращается прохождение тактовых импульсов на выход формирователя 5 через элемент 87 И. Одновременно сбрасываются триггеры 94, 95 . и 96 сигналами с выхода 31 формирователя триггер 93 блока 6 синхронизации. Кроме того, выходным сигналом 43 одновибратора 92 устанавливаются в единичное состояние регистр 10 который на выходе 58 формирует сигнал запроса прерывания, поступающий через выходы 17 устройства в микропроцессор.

В процессе работы элемент 85 И осуществляет управление дешифратором 72 формирователя 3. Элемент 86 И осуществляет формирование сигнала окончания выдачи тестового воздействия на объект в случае, когда тактовые импульсы должны опережать информационные .

После обработки процессором сигнала прерывания происходит прием в микропроцессор кода реакции аналогично описанному. Далее, если производится безусловное диагнозирование объекта, то объект может быть установлен в ис

5

0

5

0

5

0

5

0

5

ходное состояние. Для этого от микропроцессора через входы 63 поступает управляющее слово, в котором первый, второй и третий разряды находятся в нулевом состоянии, четвертьй и пятый разряды задают номер канала в объекте контроля, а восьмой разряд находится в единичном состоянии. Сигнал с выхода восьмого разряда поступает на входы 21 блока 1 ввода-вывода .

Блок 7 установки выдает с вьгхода 62 импульс установки объекта в исходное состояние.

Для выключения устройства подается сигнал на соответствующий вход генератора 14.

В режиме самопроверки аналогично описанному осуществляется прием в устройство и запись в блоке 8 специального контрольного кода для проверки оборудования устройства.

Далее происходит прием от микропроцессора аналогично описанному управляющего слова, которое задает режим самоконтроля. В этом слове четвертьй и пятый разряды, поступающие на регистр 9,. имеют нулевое значение.. Кроме того, в информации, поступающей -на входы 33 блока 4 задания режима, содержится нулевой код. Поэтому в. соответствии с табл. 1 будет возбужден соответствующий выход дешифратора 73. Далее аналогично описанному необходимо включить генератор 14, после чего устройство начинает функционировать как для режима обмена с режимом контроля. Нулевой код в регистре 9 воспринимается объектом как за- прет на прием информации от устройства.

Микропроцессор может принять код аналогично тому, как было описано ры- ше, для анализа работоспособности устройства. Если принятый код идентичен тому, который передавался на устройство, то оно считается работоспособным.

В данном режиме может проверяться как правильность формирования тактовых, так и информационных импульсов устройством. Для проверки формирования тактовых импульсов необходимо передавать в устройство код, содержащий только единицы. При пропуске тактового импульса в соответствующем разряде преобразованного контрольного кода будет нуль.

Таким образом, в режиме самоконтроля проверяется как работоспосоП- ность оборудования устройства на обеспечение хранения информации, так и реализация временной диаграммы работы.

Данное устройство имеет более широкие функциональные возможности, чем известные, так как конструктивные признаки устройства обеспечивают возможность его использования в иерар .хической системе контроля множества объектов. Кроме того, возможно гибко учитывать специфику объектов контроля путем обеспечения опережения либо отставания информационных импульсов относительно тактовых.

Устройство также позволяет обеспечить эффективное использование микропроцессора высшего уровня управления системы контроля за счет того, что конструктивные признаки обеспечивают взаимодействие с микропроцессором в режиме мультиплексирования без режимов занятого ожидания.

Повышение достоверности функционирования устройства достигается за счет того, что элементы и связи устройства позволяют реализовать ре- жим самоконтроля, в котором проверяется работоспособность как оборудования, формирующего тактовые импульсы, так и оборудования, формирующего информационные импульсы.

Формулаизобретения

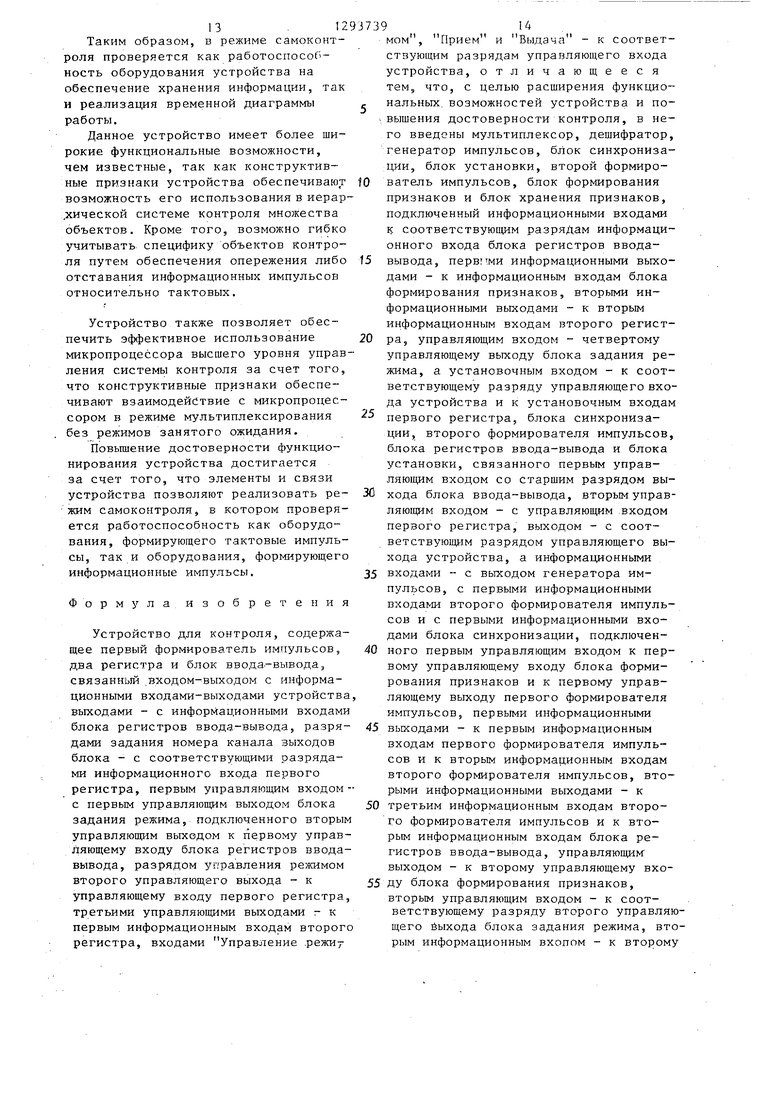

Устройство для контроля, содержащее первый формирователь импульсов, два регистра и блок ввода-вывода, связанный входом-выходом с информационными входами-выходами устройства выходами - с инфорь ационными входами блока регистров ввода-вывода, разрядами задания номера канала выходов блока - с соответствующими разрядами информационного входа первого регистра, первым управляющим входом с первым управляющим выходом блока задания режима, подключенного вторым управляющим выходом к первому управляющему входу блока регистров ввода- вывода, разрядом управления режимом второго управляющего выхода - к управляющему входу первого регистра, третьими управляющими выходами - к первым информационным входам второг регистра, входами Управление .режи7

5

мом, Прием и Выдача - к соответствующим разрядам управляющего входа устройства, отличающееся тем, что, с целью расширения функциональных, возможностей устройства и по- ., вышения достоверности контроля, в него введены мультиплексор, дешифратор, генератор импульсов, блок синхронизации, блок установки, второй формиро- ватель импульсов, блок формирования признаков и блок хранения признаков, подключенный информационными входами К соответствующим разрядам информационного входа блока регистров ввода- 5 вывода, первгтми информационными выходами - к информационным входам блока формирования признаков, вторыми информационными выходами - к вторым информационным входам второго регист- 0 ра, управляющим входом - четвертому управляющему выходу блока задания режима, а установочным входом - к соответствующему разряду управляющего входа устройства и к установочным входам первого регистра, блока синхронизации, второго формирователя импульсов, блока регистров ввода-вывода и блока установки, связанного первым управляющим входом со старшим разрядом выС хода блока ввода-вывода, вторым управ- ляюгцим входом - с управляющим .входом первого регистра, выходом - с соответствующим разрядом управляющего выхода устройства, а информационными

5 входами - с выходом генератора импульсов, с первыми информационными входами второго формирователя импульсов и с первыми информационными входами блока синхронизации, подключен0 ного первым управляющим входом к первому управляюш;ему входу блока формирования признаков и к первому управляющему выходу первого формирователя импульсов, первыми информационными

45 выходами - к первым информационным входам первого формирователя импульсов и к вторым: информационным входам второго формирователя импульсов, вторыми информационными выходами - к

50 третьим информационным входам второго формирователя импульсов и к вторым информационным входам блока регистров ввода-вывода, управляющим выходом - к второму управляющему вхо55 ДУ блока формирования признаков, вторым управляющим входом - к соответствующему разряду второго управляющего йыхода блока задания режима, вторым информационным вхопом - к второму

информационному выходу блока формирования признаков, а третьим управляющим входом - к первому управляюще- му выходу второго формирователя импульсов, соединенного вторым управляющим выходом с управляющим входом . второго регистра, управляющими выходами - с соответствуювщми разрядами управляющего выхода устройства, с вторым управляющим вьЬсодом первого формирователя импульсов и с первыми управляющими выходами блока формирования признаков, первым разрядом третьего управляющего выхода - с первым управляющим входом регистра ввода-вывода, четвертыми управляющими выходами - с управляющими входами первого формирователя импульсов, третьим информационным входом - с информацион- ньм выходом первого формирователя импульсов, четвертым информационным входом - с первым информационным выходом блока регистров ввода-вывода, а выходом Контроль - с контрольным выходом устройства и с третьим информационным входом блока регистров вво

o

.

5

0

да-вывода, связанного четвертым информационным входом с информационным входом устройства, а вторыми к третьими информационньми выходами - соот- . ветственно с первыми и вторыми информационными входами мультиплексора, подключенного третьими информационными входами к первому выходу второго регистра, управляющими входами - . к третьему управляющему выходу блока задания режима, а выходом - к первым информационным входам блока ввода- вывода, соединенного вторым информационным входом с выходом депшфратора и с управляющим входом блока задания режима, подключенного выходом Конец операции к выходу Запрос прерывания второго регистра и к информационному выходу устройства, соединенного адресными выходами с вторыми управляющими выходами блока формирования признаков и с выходами первого регистра, а соответствующими разряда

ми управляющего дешифратора и с импульсов.

входа - с входами входами генератора

Таблица 1

Фие.2

(риг.З

(pt/e.J

фаг,5

r

(StCM Co

«S 45- c

Редактор 0.Петрушке

Составитель А.Лишанский

Техред л.Олейник Корректор С.Шекмар

Заказ 388/54 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

b

5J

Q.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1608672A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в иерархических многоканальных системах контроля в качестве устройства управления и контт роля многоканальных объектов. Цель изобретения - расширение функциональных возможностей устройства и повышение достоверности контроля. Устройство содержит блок 1 ввода - вывода, блок 2 хранения признаков, первый формирователь 3 импульсов, блок 4 задания режима, второй формирователь 5 импульсов, блок 6 синхронизации, -блок 7 установки, блок 8 регистров ввода-вывода, первый регистр 9, вто-; (Л С N9 ;о ее 00 ;о

| Авторское свидетельство СССР № 913376, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических схем | 1976 |

|

SU590743A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-02-28—Публикация

1985-04-09—Подача