S

(Л

памяти 9 и 10. Устр-во обеспечивает реализацию следующих стр5гктур: два звена первого порядка, каждое из которых реализовано по прямой форме; звено второго порядка, реализованное по прямой форме; параллельный адаптер; последовательный адаптер, двухпортовый адаптер, цифровой эквивалент кой- вектора обобщенной реактивной проводимости с преобразованием тока; цифровой фильтр с комплексными коэффициентами, цифровой эквивалент частотно-зависимого отрицательного сопротивления; звено с нормированной ортогональной полиноминальной структурой Грея и Маркела; дискретный интегратор без потерь и адаптер с правильной лестничной конфигурацией. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| СПОСОБ ЦИФРОВОЙ РЕКУРСИВНОЙ ПОЛОСОВОЙ ФИЛЬТРАЦИИ И ЦИФРОВОЙ ФИЛЬТР ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 2011 |

|

RU2460130C1 |

| Программно-управляемый цифровой фильтр | 1979 |

|

SU877787A1 |

| СПОСОБ ЦИФРОВОЙ РЕКУРСИВНОЙ ПОЛОСОВОЙ ФИЛЬТРАЦИИ И ЦИФРОВОЙ ФИЛЬТР ДЛЯ РЕАЛИЗАЦИИ СПОСОБА | 2014 |

|

RU2579982C2 |

| Программируемый цифровой фильтр | 1986 |

|

SU1374244A1 |

| Устройство для фильтрации симметричных составляющих | 1985 |

|

SU1343362A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| Адресное устройство для цифрового фильтра | 1985 |

|

SU1298859A1 |

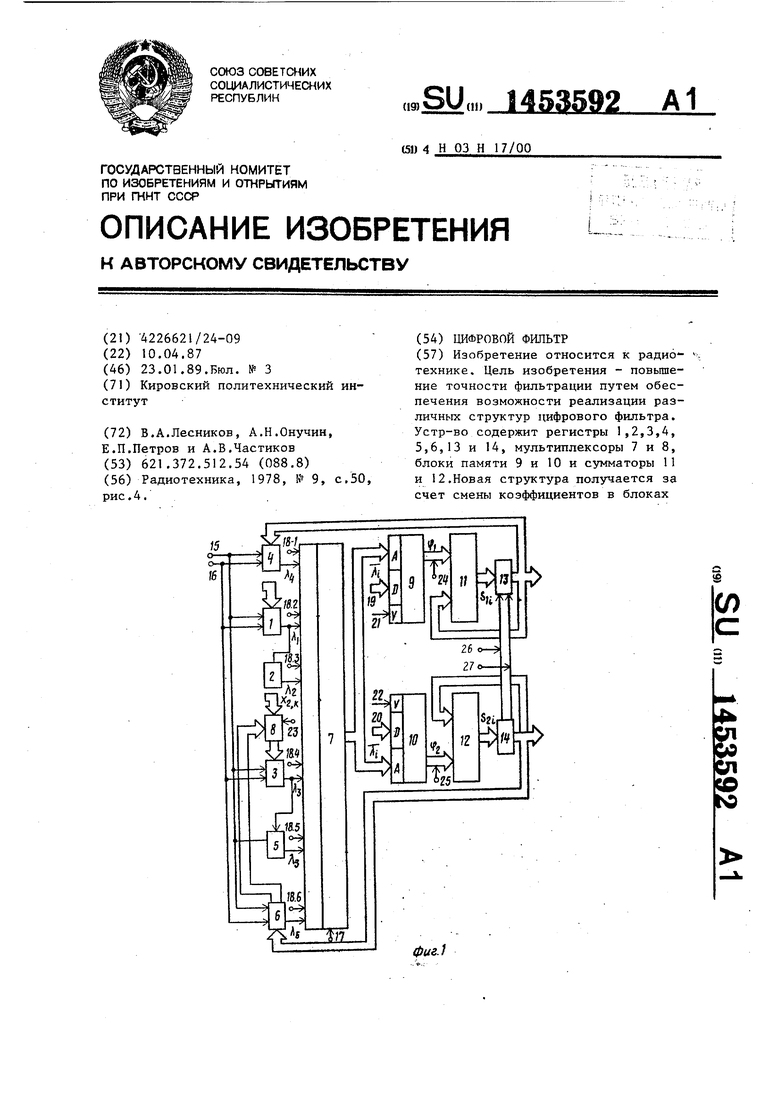

Изобретение относится к радиотехнике. Цель изобретения - повышение точности фильтрации путем обеспечения возможности реализации различных структур цифрового фильтра, Устр-во содержит регистры 1,2,3,4, 5,6,13 и 14, мультиплексоры 7 и 8, блоки памяти 9 и 10 и сумматоры 11 и 12.Новая структура получается за счет смены коэффициентов в блоках

1

Изобретение относится к радиотехнике и может быть использовано для фильтрации сигналов, заданных цифровым кодом.

Цель изобретения - повышение точности фильтрации путем обеспечения возможности реализации различных структур цифрового фильтра.

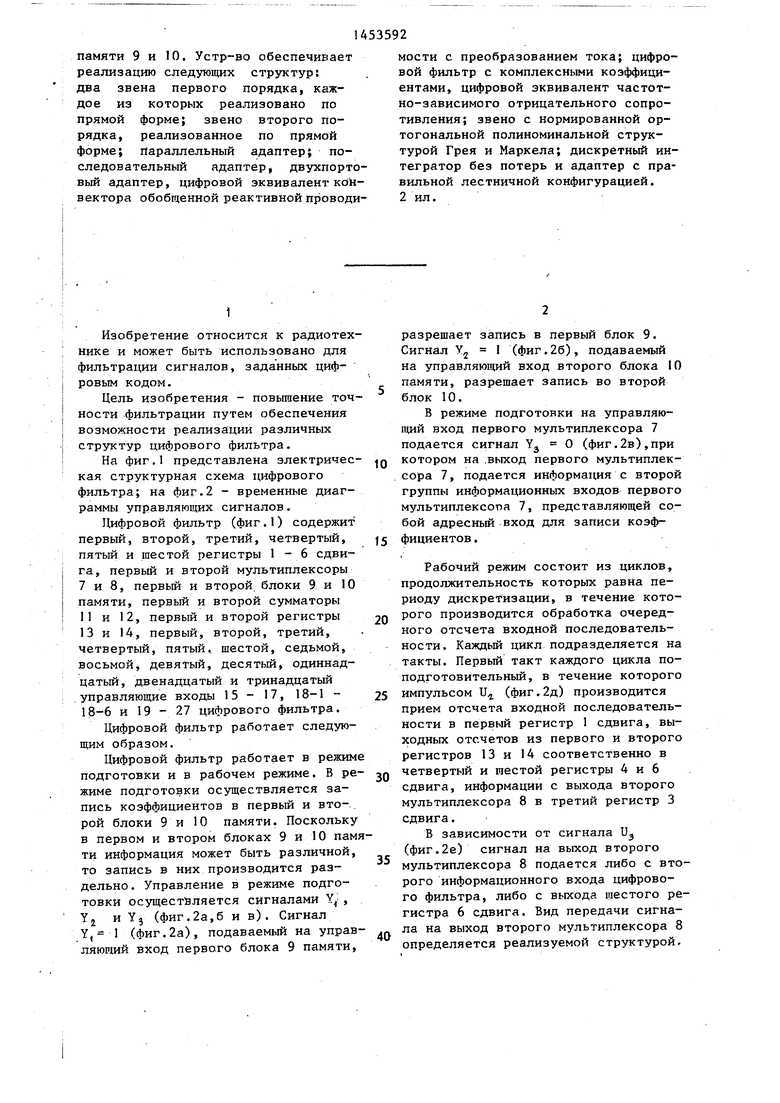

На фиг,1 представлена электричес- кая структурная схема цифрового фильтра; на фиг.2 - временные диаграммы управляющих сигналов.

Цифровой фильтр (фиг.1) содержит первый, второй, третий, четвертый, пятый и шестой регистры 1 - 6 сдвига, первый и второй мультиплексоры 7 и 8, первый и второй блоки 9 и 10 памяти, первый и второй сумматоры 11 и 12, первый и второй регистры 13 и 14, первый, второй, третий, четвертый, пятый., шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый и тринадцатый управляющие входы 15 - 17, 18-1 - 18-6 и 19 - 27 цифрового фильтра.

Цифровой фильтр работает следующим образом.

Цифровой фильтр работает в режим подготовки и в рабочем режиме. В ре жиме подготовки осуществляется запись коэффициентов в первый и вто-. рой блоки 9 и 10 памяти. Поскольку в первом и втором блоках 9 и 10 памти информация может быть различной, то запись в них производится раздельно. Управление в режиме подготовки осуществляется сигналами Y, Y и Y, (фиг.2а,б и в). Сигнал Y, 1 (фиг.2а), подаваемый на управ ляющий вход первого блока 9 памяти.

5 0 5

Q Q

5

разрешает запись в первый блок 9. Сигнал Yj 1 (фиг.26), подаваемый на управляющий вход второго блока 10 памяти, разрешает запись во второй блок 10.

В режиме подготовки на управляющий вход первого мультиплексора 7 подается сигнал Y О (фиг.2в),при котором на .выход первого мультиплексора 7, подается информация с второй группы информационных входов первого мультиплексора 7, представляющей собой адресный вход для записи коэффициентов .

Рабочий режим состоит из циклов, продолжительность которых равна периоду дискретизации, в течение которого производится обработка очередного отсчета входной последовательности. Каждый цикл подразделяется на такты. Первый такт каждого цикла по- подготовительный, в течение которого импульсом U.1 (фиг.2д) производится прием отсчета входной последовательности в первый регистр 1 сдвига, выходных отсчетов из первого и второго регистров 13 и 14 соответственно в четвертый и шестой регистры 4 и 6 сдвига, информации с выхода второго мультиплексора 8 в третий регистр 3 сдвига.

В зависимости от сигнала U (фиг.2е) сигнал на выход второго мультиплексора 8 подается либо с второго информационного входа цифрового фильтра, либо с выхода щестого регистра 6 сдвига. Вид передачи сигнала на выход второго мультиплексора 8 определяется реализуемой структурой.

По сигналу IJj (фиг.2з) в подготовительном осуществляется начальная установка первого и второго регистров 13 и 14.

По окончании прдготовит ельного такта в первом, втором, третьем, четвертом, пятом и шестом регистрах 1 - 6 сдвига соответственно хранятся числа х,, х,,., , х,, у,,, , x.k-.y.k.,, X и х, - отсчеты входных последовательностей, поступающих в К-м цикле соответственно на первый и второй информационные входы звена цифрового фильтра; х , и х.., отсчеты, поступившие на информацион- ные входы цифрового фильтра в предыдущем цикле; у,,.., и выходные отсчеты цифрового фильтра, вычис ленньгё и сформированные на первом и втором выходах цифрового фильтра в предыдущем цикле; К - номер цикла. .

I

В рабочем режиме на управляющий вкод первого мультиплексора 7 подается сигнал YJ 1 (фиг.2а), при этом на адресные входы первого и второго блоков 9 и IО памяти информация подается от первых выходов, первого, второго, третьего, четвертого, пятого и шестого регистров 1 - 6 сдвига. Их первые выходы представляют собой выходы из старших разрядов (возможна и реализация, при которой к первому мультиплексору подключаются младшие разряды), на кото2ых формируются сигналы ; (i 1,6 - номер регистра сдвига), принимающие значения О или 1 .

Комбинация сигналов

Aj ( A, ,...,),

(j 0,m-l - номер цикла, m - чис- ло разрядов регистра сдвига) на входе первого мультиплексора 7 представляет собой адрес, по которому из первого и второго блоков 9 и 10 памяти считываются соответственно значения функций

Ч,(л) -А, + а + а,, +

.0, Ьоо1 + ;

+ 5 3

tfiC/) ,0,0 + , ,,„ +

-Лдв,,, + ,bo,, + Agb,,, ,

3592

где а. и Ьц - коэ4)фициенты,

определяющие вид структуры

gцифрового фильтра.

Дсе возможные значения функций Ч, (Л) и Cfj (Л) (поскольку Я; может принять только два значения О или I,

10 то каждая из этих функций принимает 2 64 значений) вычисляются заранее.

Числа, считанные из первого и второго блоков 9 и 10 памяти, поступа15 ют на первые входы первого и второго сумматоров 11 и 12, на вторые входы которых подается содержимое первого и второго регистров 13 и 14 со сдвигом на один разряд в сторону младших

0 разрядов. Импульсами Щ (фиг.2ж), подаваемыми на управляющие входы первого и второго регистров 13 и 14, полученные на выходах первого и второго сзгмматоров 11 и 12 числа S,;

25 и 3,2; записываются в первьй и второй регистры 13 и 14. Импульсами U, (фиг.2г), подаваемыми на управляющие входы первого, второго, третьего, четвертого, пятого и шестого регист0 ров 1 - 6 сдвига, производится сдвиг в сторону младших разрядов. При этом старшие разряды первого и третьего регистров 1 и 3 сдвига поступают в освободившиеся младшие разряды вто35 рого и пятого регистров 2 и 5 сдвига соответственно. После этого из первого и второго блоков 9 и 10 памяти считываются следующие числа, соответствующие новым комбинациям Л:.

0 Число таких тактов равно т.

В конце К-го цикла отсчеты х, и поступают соответственно во второй и пятый регистры 2 и 5 сдвига, а первый, третий, четвертый и шестой регистры 1,3,4 и 6 сдвига готовы к приему очередных отсчетов в начале следующего цикла. При обработке их старших разрядов в первом основном такте каждого цикла числа первого и второго блоков 9 и 10 на первые входы первого и второго сумматоров 11 и 12 передаются с противоположным знаком (например, все разряды инвертируются, а на входы переноса в младшие разряды первого и второго сумматоров 11 и 12 подается .единица). Это осуществляется импульсом U (фиг.2и).

45

50

55

514535926

В конце i-го цикла в первом и торых реализовано по прямой форме, - , втором регистрах 13 и 14 формируются) описываемых разностными уравнениями: числа

Пк- S,.m., -tf/ЛР +

m-1

-J .

.CAj) 2

m-i

-J

+ С| ,(Л;)2-

о

Учитывая, что

х J (,к i.K i

J

IC-i У 2. K( )

где X ,j ,K-i 2,K iiK- ,k ( iV.K- J разряды чисел x,, , ., .y.k., ) 2,.-. y.k-i соответственно, градетавленных в дополни- тельном коде:

hi-r

J l W-(

J 0-J

e 2 ; ,-J

Z: y/e 2 .

порядка суммирох преобразований,

000 НХ + 00, 4Л-. 00 Xak +

;+ X i,K-i+ Учли , У2л-(

;Уак 010 14 оц (л-.) «0 :- а„, , + Ьо„ у,,, + Ь,„ у2,,.

Изменяя коэффициенты и b.jg , можно менять вид разностных уравнений и, соответственно, менять структурную схему цифрового фильтра

Так при

0( о и

10, а

fOI

О;

000

001 001 01

001 0(

w 10

411

а,, 5 Ь, Ц,

и при Uj О (фиг.2е) получают два звена первого порядка, каждое из ко- (к 00 01 ,к-| t oi y,v(

001

У2к a,oX,i, + а, х,,,+ Ь„ у,,., . При а,оо а,о, а, Ь, , 0;

001 010 о 011 1 а„, bj ; bo,i а,; b, b

и при подаче в подготовительном такте сигнала Ug-1 (фиг.2е) получают звено, описываемое системой разност- ных уравнений

УП о к а х, + .- + ЗаУ,1см ;

25

У к .K-i

4К y.k-l .

ИЗ которой после очевидных преобразований получают разностное уравнение, 30 описывающее работу звена второго порядка, реализованного по прямой форме:

Угк о х,к + «1 х,,+ а2Х,. +

35

Ь, У2,,.,+ Ь2У,,

г.

При а.-- ot, -1 ; а,,,,,. 1-cij,;

0«5

,;

40

014

1 а ЮО 2 101 2

; а,„ 1-ei,;

45

OOI

o(j-l;

bo,, о; b,o, 0; b,,, - 1 и при и, о

получают разностное уравнение, опи- 50 сываюп1ее работу звена стандартного волнового цифрового фильтра Фейт- твайса на основе параллельного адаптера, в котором oi, , и odj - ко- эффициенты параллельного адаптера. 55 При ао„, /3, -1; а„, р.-1 ;

040

(,;

1Ьо 1 01 /z

М(0

(57-1; а,„ f3, -1;

000

1-сЬ

001 10 i

он

0; 3.., 0; а

101

С

1

0(1

0; а.

Ч,, 0; ь,о, 0; b

1И

О

Ьво,

Ч ; a Ь,„ 1-,. и при и, О (фиг.2е) получают разностное уравнение, описывающее работу звена стандартного волнового цифрового фильтра Фейттвайса на осно- и при Uj О (фиг.2е) получают разве последовательного адаптера, в ко- ностное уравнение звена с нормирован- тором |2i, , (3i и 5 - коэффициенты последовательного адаптера.

При 000 00, 05 010

ной ортогональной полиноминальной структурой Грея и Маркела, где Cj - коэффициент звена. Т

00

0; а,о, od; ; -t.o 5 w 9 t ooi О.

оц- О; b,o 0; Ь„,

о

и при Uj О (фиг.2е) получают разностное уравнение, описывающее работу звена волнового цифрового фильтра на двухпортовых адаптерах, где о{; - коэффициент адаптера.

При 000 ; 001 ; 010 0;

он

- о 101

1; а,. -1; Ъ

OJ 05 b,

00)

ш

0;

0.

и при Uj о (фиг.2е) получают разностное уравнение, описывающее работу цифрового эквивалента конвектора обобщенной реактивной проводимости с преобразованием тока.

При 000 1; 00, 0; („0 0;.

0; 0; а,-. 0;

МО 1 - ooi -

in,Zp;

(Л( lOI

м«

- Re Zp

и при Uj о (фиг.2е) получают раз- ностеное уравнение, описьшающее работу звена цифрового фильтра с комплексными коэффициентами, где Z -. полюс звена фильтра.

При 0; а„, 0; +1;

Зо„ 0; а,(,р 0; а, 0;

но

0;

И1

-15 оог О;

011 О; t loi 2; Ь„,

О

и при (фиг.2е) получают разност- ное уравнение, описывающее работу цифрового эквивалента частотно-зависимого отрицательного сопротивления.

При

000

1-сЬ

001 10 i

он

0; 3.., 0; а

101

С

1

О (фиг.2е) получают раз уравнение звена с нормиро

0(1

0; а.

О (фиг. уравнение

Ч,, 0; ь,о, 0; b

1И

О

j О (фиг.2е) получают ра уравнение звена с нормир

и при Uj О (фиг.2е) получают разностное уравнение звена с нормирован

ной ортогональной полиноминальной структурой Грея и Маркела, где Cj - коэффициент звена. Т

При а

000

Кх

001

О; а

010

О;

з,о„

О; а

,о 0;

«0

0; а... . О; , 1;

20

Ьон 1; ь

101

О; Ъ... О

и при Uj о (фиг.2е) получают разностное уравнение дискретного интегратора без потерь, где T,R,x, - пара- 25 метры интегратора.

При а

000

00

0;

OtO

оС; +1;

0(1

юс

О 100 - 101 - оЛ 3 „, bQ.0;

О; Ь

101

1; ь,

, .

и при Uj О (фиг.2е) получают раз- костные уравнения, описывающие адаптер волнового цифрового фильтра с правильной лестничной конфигурацией, где oi; - коэффициент адаптера.

Формула изобретения

Цифровой фильтр, содержащий последовательно соединенные первый- регистр сдвига, информационный вход которого является первым информационным входом цифрового фильтра, и второй регистр сдвига последовательно соединенные первый блок памяти и первый сумматор, а также третий, четвертый и пятый регистры сдвига, о т- личающийся тем, что, с целью повьшения точности фильтрации путем обеспечения возможности реализации различных структур цифрового

фильтра, введены шестой регистр

сдвига, первый и второй управляющие входы которого объединены соответст- венно с первыми и вторыми управляющими входами первого, второго, треть-

его, четвертого и пятого регистров

сдвига и являются первым и вторым управляющими входами цифрового фильтра, первый регистр, вход которого соединен с выходом первого сумматора, а выход соединен с информационным входом четвертого регистра сдвига, с вторым входом первого с мматора и является первым выходом цифрового фильтра, последовательно соединенные второй блок памяти, второй сумматор и второй регистр, выход которого соединен с информационным входом шестого регистра сдвига, с вторым входом второго сумматора и является вторым выходом цифрового фильтра, первый мультиплексор, первая группа сигнальных входов которого соединена с выходами первого, второго, третьего, четвертого, пятого и шестого регистров сдвига, вторая группа сигнальных входов является третьими управляющими входами цифрового фильтра, управляющий вход является четвер- 25входы первого и второго регистров тым управляющим входом цифровогосоответственно объединены и являют- фильтра, а выход соединен с адресны-ся двенадцатым и тринадцатым управ- ми входами первого и второго блоковляющими входами цифрового фильтра.

, 45359210

памяти, информационные входы которых являются соответственно пятым и шестым управляющими входами цифрового фильтра, а входы разрешения записи - соответственно седьмым и восьмым управляющими входами цифрового фильтра, а также второй мультиплексор, первый сигнальный вход которого явJQ ляется вторым информационным входом цифрового фильтра, второй сигнальный вход соединен с вторым выходом шестого регистра сдвига, управляющий вход является девятым управляю15 щим входом цифрового фильтра, а выход соедиенн с информационным входом третьего регистра сдвига, выход которого соединен с информационным входом пятого регистра сдвига, при

2Q этом, управляющие входы первого и второго сумматоров являются соответ- ств.енно десятым и одиннадцатым уп- равляющими входами цифрового фильтра, а первые и вторые управляющие

| Радиотехника, 1978, № 9, с.50, рис.4. |

Авторы

Даты

1989-01-23—Публикация

1987-04-10—Подача