тактов. Операции выполняются над до- полнительпыми кодами чисел. Б каждом рабочем такте выполняются следующие операции. Компараторами Ю сравнива- ются коды, преобразованные ВПК 9, с кодом числа, записанным в счетчике 11 Полученный результат сравнения поступает в БУ 15 и.БИ 19. В БУ 15 умножается это число на число, находящееся на выходе БП 13. а в БИ 19 число с выхода. БП 13 инвертируется в зависимости от значения сигнала на выходе первого компаратора 10.. Полученные числа на выходах БУ 15 и БИ 19 и регистра 18 суммируются в сумматорах 17 и 16, а полученная сумма чисел записывается в регистр 18. Затем

Изобретение относится к цифровой обработке сигналов и может быть использовано в системах цифровой фильтрации в радиосвязи, радиолокации и радионавигации.

Цель изобретения - повьшение быстродействия цифрового фильтра.

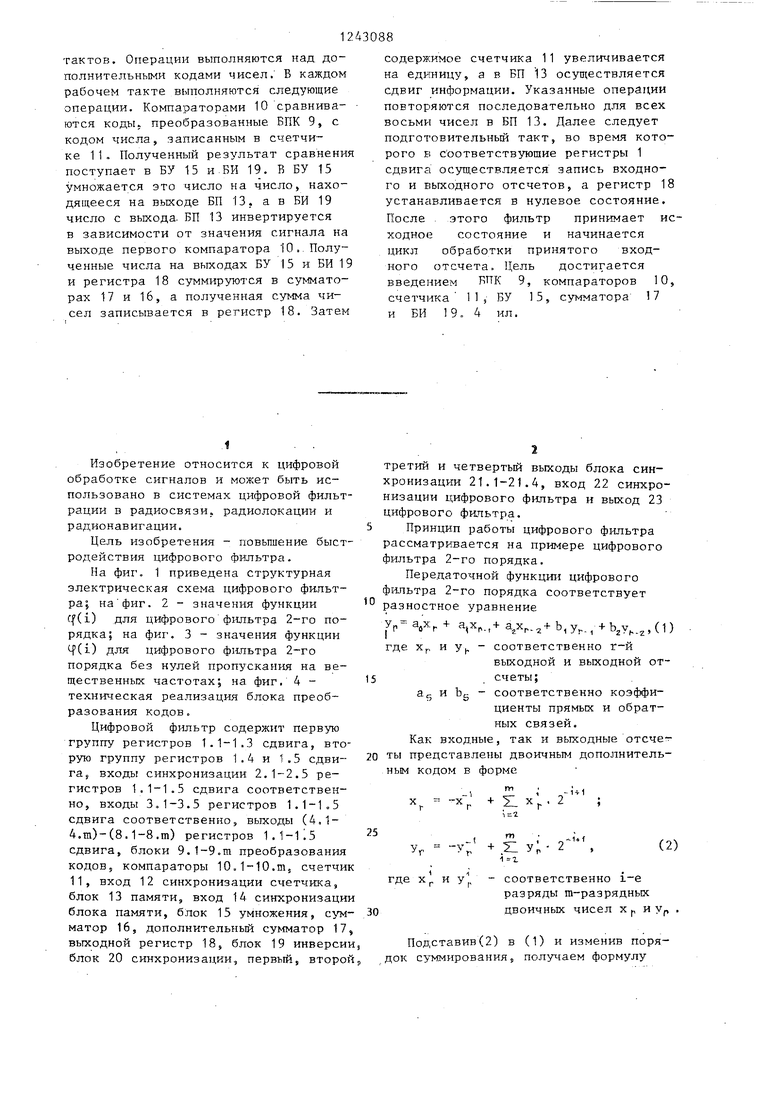

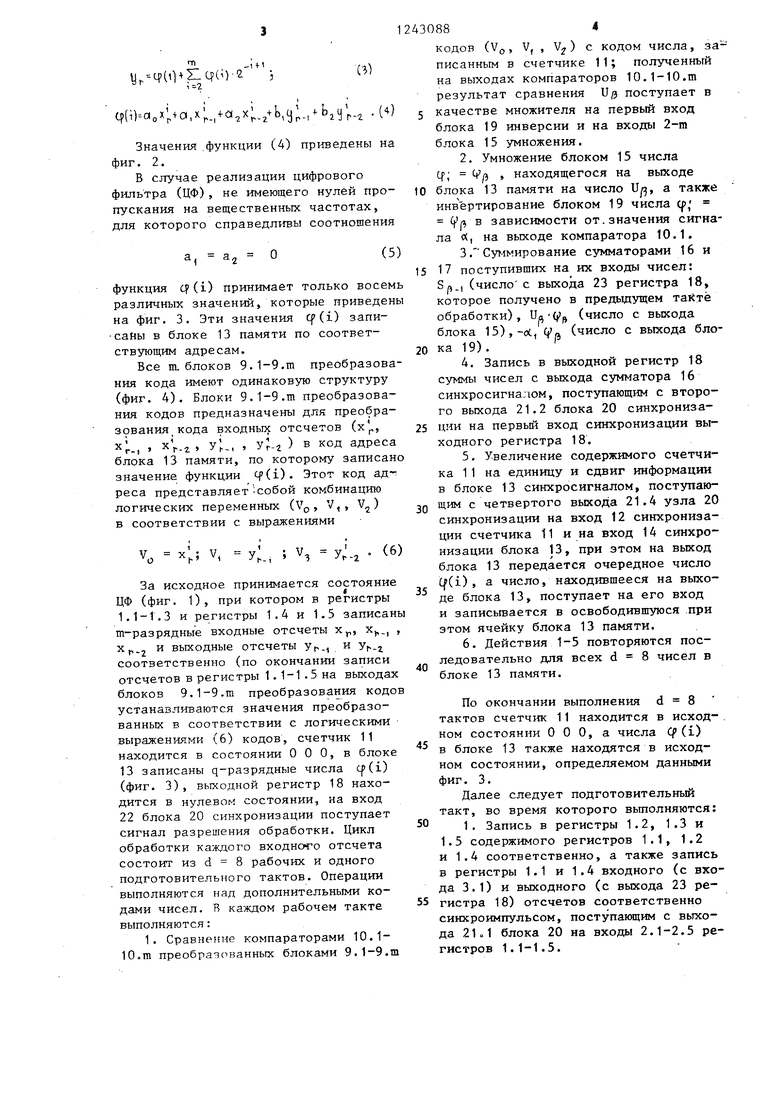

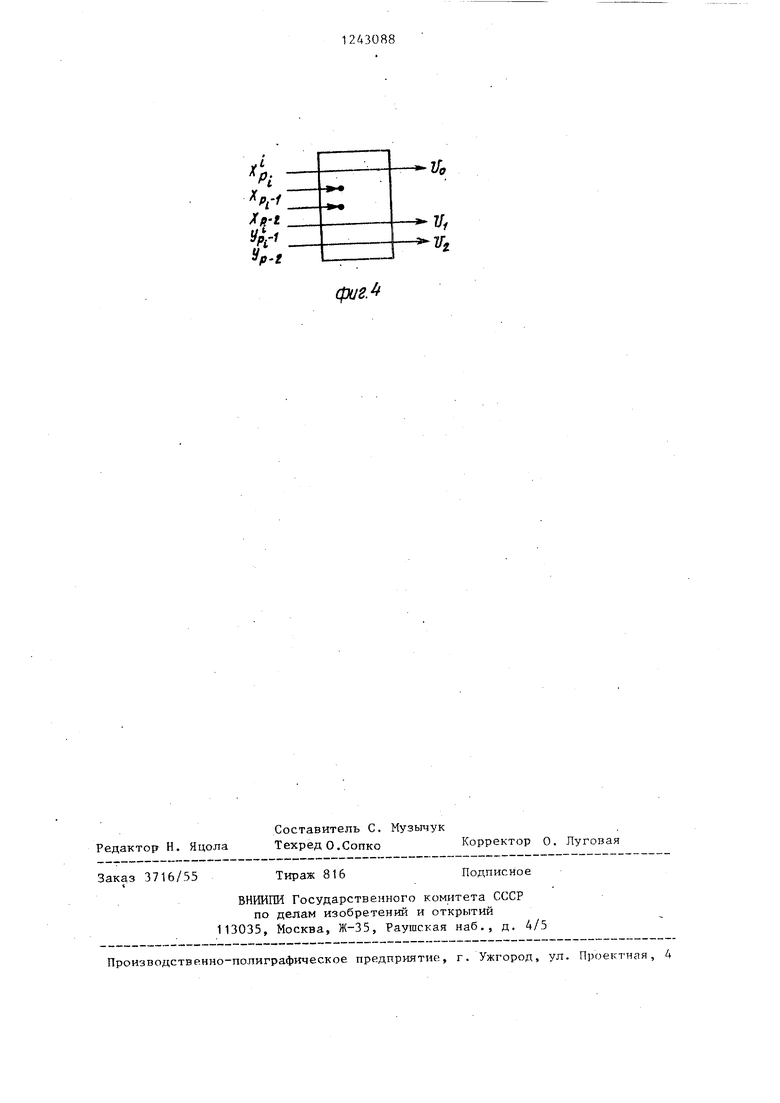

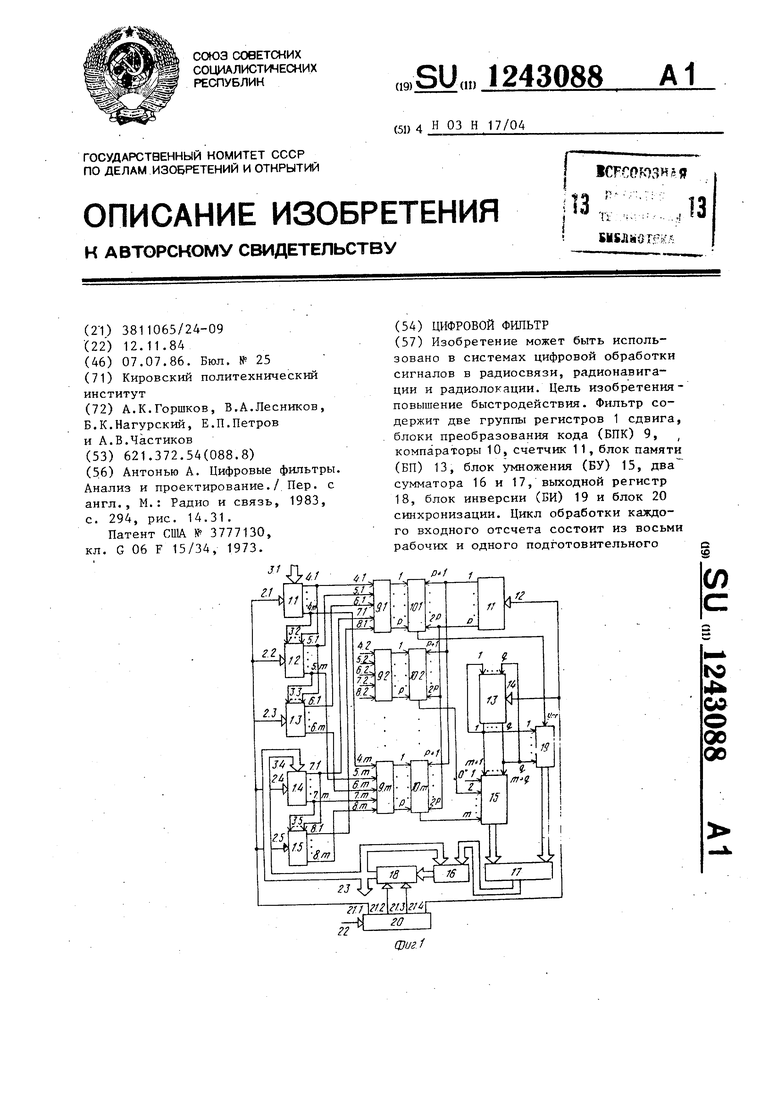

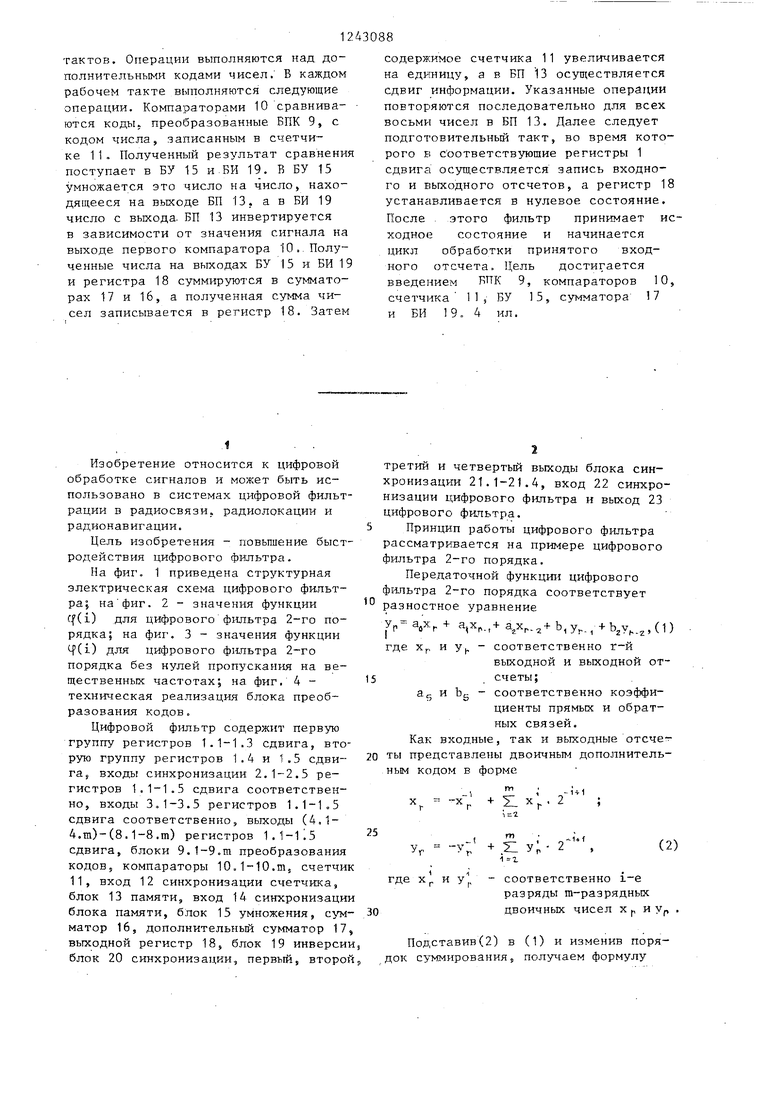

На фиг. 1 приведена структурная электрическая схема цифрового фипьт- ра; на фиг. 2 - значения функции f.f(i) для цифрового фильтра 2-го порядка; на фиг. 3 - значения функции Ч (1) для цифрового ф1.шьтра 2-го порядка без нулей пропускания на вещественных частотах; на. фиг, 4 - техническая реализация блока преобразования кодов.

Цифровой фильтр содержит первую группу регистров 1.1-1.3 сдвига, вторую группу регистров 1.4 и 1.5 сдви- га, входы синхронизации 2.1-2.5 регистров 1.1-1.5 сдвига соответственно, входы 3.1-3.5 регистров 1.1-1,5 сдвига соответственно, выходы (4.1- 4.m)-(8.1-8.m) регистров 1. сдвига, блоки 9.1-9.т преобразования кодов, компараторы 10.1-10.т, счетчик 11, вход 12 синхронизации счетчика, блок 13 памяти, вход 14 синхронизации блока памяти, блок 15 умножения, сум- матор 16, дополнительный сумматор 17, выходной регистр 18, блок 19 инверсии блок 20 синхронизации, первый, второй

содержимое счетчика 11 увеличивается на единицу, а в БП 13 осуществляется сдвиг информации. Указанные операции повторяются последовательно для всех восьми чисел в БП 13. Далее следует подготовительньш такт, во время которого в соответствующие регистры 1 сдвига осуществляется запись входного и выходного отсчетов, а регистр 18 устанавливается в нулевое состояние. После . этого фильтр принимает исходное состояние и начинается цикл обработки принятого входного отсчета. Цель достигается введением БПК 9, компараторов 10, счетчика П , БУ 15, сумматора 17 и БИ 19. 4 ил.

2

третий и четвертый выходы блока синхронизации 21.1-21.4, вход 22 синхронизации цифрового фильтра и выход 23 цифрового фильтра.

Принцип работы цифрового фильтра рассматрр|вается на примере цифрового фильтра 2-го порядка.

Передаточной функции цифрового фильтра 2-го порядка соответствует разностное уравнение ,х,+ a,x,.,+ ,.+b,y,.,+b,y,.,(1

где Хр и У(, - соответственно г-й

выходной и выходной отсчеты;а,- и Ъс- - соответственно коэффи.3 Э

циенты прямых и обратных связей.

Как входные, так и выходные отсчет ты представлены двоичным дополнительным кодом в форме

х,

1 , + Z. х . 2 ;

(2)

УГ -У„ + 2 Ур ,

i г

где х и у, - соответственно i-e разряды т-разрядных двоичных чисел х f, и у

Подставив(2) в (1) и изменив порядок суммирования, получаем формулу

ll-t

ij -LpdVllq C l- z i

t(i)-c(,x;-, + . 2yr-7 -(

Значения.функции (4) приведены на фиг. 2.

В случае реализации цифрового фильтра (ЦФ), не имеющего нулей пропускания на вещественных частотах, для которого справедлршы соотношения

а, aj О

функция Cf(i) принимает только восем различных значений, которые приведен на фиг. 3. Эти значения cp(i) запи- саны в блоке 13 памяти по соответствующим адресам.

Все т. блоков 9.1-9.т преобразования кода имеют одинаковую структуру (фиг. 4). Блоки 9.1-9.т преобразования кодов предназначены для преобразования кода входных отсчетов (х , г-, xV.2 , У ., , Уг-г ) в код адреса блока 13 памяти, по которому записан значение функции tp(i)« Этот код ад-г реса представляет Собой комбинацию логических переменных (.V , V,, V) в соответствии с выражениями

о 4 1 yL У1-г 6)

За исходное принимается состояние ЦФ (фиг. 1), при котором в регистры 1.1-1.3 и регистры 1.4 и 1.5 записаны т-разрядные входные отсчеты х, х., , Xj,. и выходные отсчеты Уf., и у, соответственно (по окончании записи отсчетов в регистры 1.1-1 .5 на выходах блоков 9.1-9.га преобразования кодов устанавливаются значения преобразованных в соответствии с логическими выражениями (6) кодов, счетчик 11 находится в состоянии О О О, в блоке 13 записаны q-разрядные числа c|)(i) (фиг. 3), выходной регистр 18 находится в нулевом состоянии, на вход 22 блока 20 синхронизации поступает сигнал разрешения обработки. Цикл обработки каждого входноч о отсчета состоит из d 8 рабочих и одного подготовительного тактов. Операции выполняются над дополнительными кодами чисел. В каждом рабочем такте выполняются:

1. Сравнение компараторами 10.1- 10.m преобразс ванных блоками 9.1-9.т

2430884

кодов ((,, V, , V.) с кодом числа, записанным в счетчике 11; полученный на выходах компараторов 10.1-10.т результат сравнения U/з поступает в 5 качестве множителя на первый вход блока 19 инверсии и на входы 2-т блока 15 умножения.

2. Умножение блоком 15 числа Ф/) , находящегося на выходе

10 блока 13 памяти на число Uo, а также инв ертирование блоком 19 числа if УД в зависимости от.значения сигнала Л, на выходе компаратора 10.1. 3.Суммирование сумматорами 16 и

15 17 поступивших на их входы чисел: Sj,., (число с выхода 23 регистра 18, которое получено в предыдущем таЛтё обработки), Ufl {j)p (число с выхода блока 15),-с., ((- (число с выхода бло20 ка 19).

4.Запись в выходной регистр 18 суммы чисел с выхода сумматора 16 синхросигналом, поступающим с второго выхода 21.2 блока 20 синхрониза25 ции на первый вход синхронизации выходного регистра 18.

5.Увеличение содержимого счетчика 1 1 на единицу и сдвиг информации в блоке 13 синхросигналом, поступаю3Q щим с четвертого выхода 21.4 узла 20 синхронизации на вход 12 синхронизации счетчика 11 и на вход 14 синхронизации блока 13, при этом на выход блока 13 передается очередное число C(i) , а число, находившееся на выходе блока 13, поступает на его вход и записьгеается в освободившуюся при этом ячейку блока 13 памяти.

6.Действия 1-5 повторяются последовательно для всех d 8 чисел в

35

40

блоке 13 памяти.

По окончании выполнения d 8 тактов счетчик 11 находится в исход- , ном состоянии О О О, а числа Q (i)

в блоке 13 также находятся в исходном состоянии, определяемом данными фиг. 3.

Далее следует подготовительный такт, во время которого выполняются:

1. Запись в регистры 1.2, 1.3 и 1.5 содержимого регистров 1.1, 1.2 и 1.4 соответственно, а также запись в регистры 1.1 и 1.4 входного (с входа 3.1) и выходного (с выхода 23 регистра 18) отсчетов соответственно синхроимпульсом, поступающим с вьтхо- да 21 о 1 блока 20 на входы 2.1-2.5 регистров 1.1-1.5.

2. Установка в нулевое состояние выходного регистра 18 синхроимпульсом с вьпсода 21.3 блока 20.

После выполнения подготовительного такта ЦФ принимает исходное состояние и начинает цикл обработки принятого входного отсчета.

Формула изобретения

Цифровой фильтр, содержащий первую и вторую группы последовательно соединенных регистров сдвига, сумма- тор, выходной регистр, памяти и блок синхронизации, причем вход первого регистра сдвига первой группы является входом цифрового фильтра выход выходного регистра является выходом цифрового фильтра и соединен с входом первого регистра сдвига второй

группы и с первьм входом сумматора, выход которого соединен с входом выходного регистра, а первый, второй и третий выходы блока синхронизации подключены соответственно к входу синхронизации регистров сдвига первой и второй групп, к первому и второму входам синхронизации выходного регистра, отличающийся тем, что, с целью повьшения быстродействия, в него введены m блоков

0

s 0

5 0

преобразования кода, m компараторов, счетчик5 блок умножения, дополнитель-. нь5й сумматор и блок инверсии, причем выход i-ro разряда регистров сдвига первой и второй групп соединен с j-м входом 1-го блока преобразования кода, где i 1 , т; j , п - количество регистров сдвига первой и второй групп, р выходов каждого блока преобразования кода соединены с первыми р входами соответствующего компаратора, вторые р входы которых об ъединены и соединены с выходами счетчика, а выход З-го компаратора .подключен к S-му входу блока 1гмноже- ния (S 2, т)} выход которого соединен с первым входом дополнительного сумматора, вьтход которого соединен с вторым входом сумматора, а второй вход дополнительного сумматора соединен с вьосодом блока инверсии, управ- ляклций вход которого соединен с выходом первого компаратора, $-й выход блока памяти (t 1, q) подключен к Е-му входу блока памяти, к f-му входу блока .инверсии и к (т f) -му входу блока умножения, первый вход которого является входом сигнала логического а вход синхронизации блока памяти соединен с входом синхронизации счетчика и с четвертым выходом блока синхронизации.

фиг.З

фие.

Редактор Н. Яцола

Составитель С, Музьгчук

Техред О.Сопке Корректор О. Луговая

Заказ 3716/55

Тираж 816

ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1986 |

|

SU1354393A1 |

| УСТРОЙСТВО СТАТИСТИЧЕСКОГО УПЛОТНЕНИЯ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 1997 |

|

RU2110897C1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| Устройство аналого-цифрового преобразования | 1981 |

|

SU1012435A1 |

| Цифровой фильтр | 1985 |

|

SU1327281A1 |

| Цифровой измеритель | 1988 |

|

SU1626170A1 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

Изобретение может быть использовано в системах цифровой обработки сигналов в радиосвязи, радионавигации и радиолокации. Цель изобретения- повышение быстродействия. Фильтр содержит две группы регистров 1 сдвига, блоки преобразования кода (ВПК) 9, компараторы 10, счетчик 11, блок памяти (БП) 13, блок у шожения (БУ) 15, два сумматора 16 и 17, выходной регистр 18, блок инверсии (БИ) 19 и блок 20 синхронизации. Цикл обработки каждого входного отсчета состоит из восьми рабочих и одного подготовительного с (О tc 41 оа О 00 00

| Антонью А | |||

| Цифровые фильтры | |||

| Анализ и проектирование./ Пер | |||

| с англ., М.: Радио и связь, 1983, с | |||

| ДИФФЕРЕНЦИАЛЬНАЯ ТЕРМИОННАЯ ЛАМПА | 1920 |

|

SU294A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1984-11-12—Подача