Изобретение относится к вьгчисли- тельной технике и может быть исполь зовано для построения запоминающих устройств с произвольным доступом.

Цель изобретения - расширение области применения за счет организа- 1ЩИ обращения по нескольким адресам к блокам оперативной памяти.

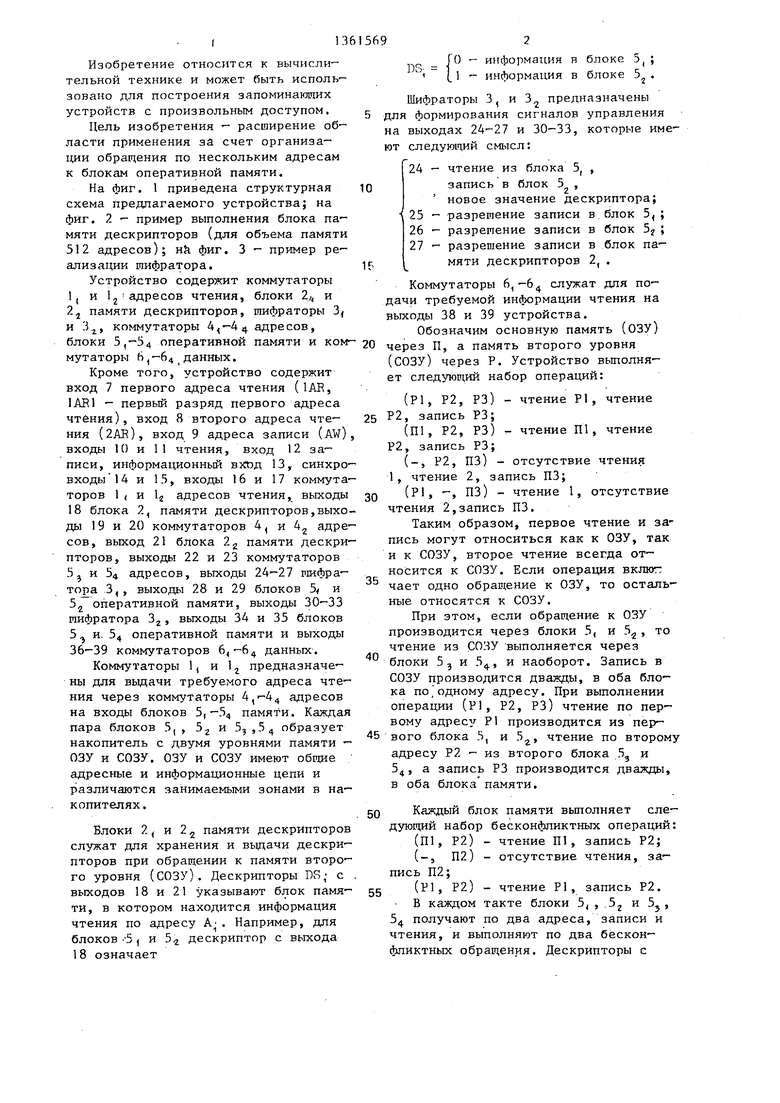

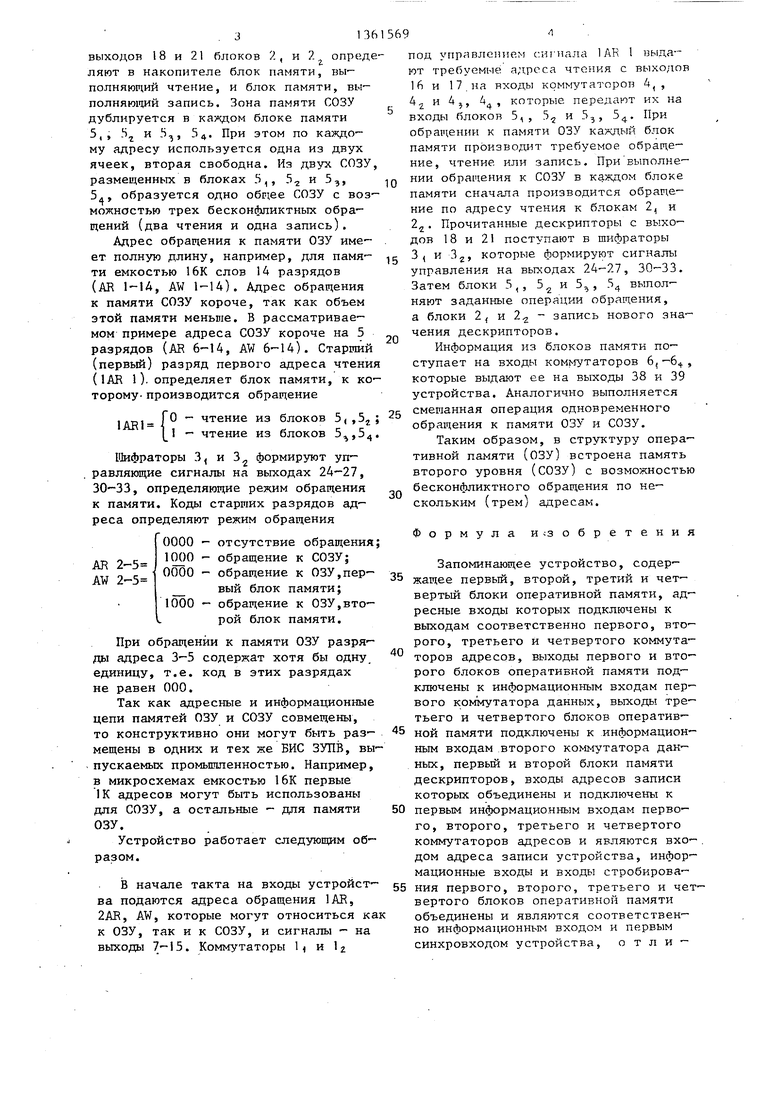

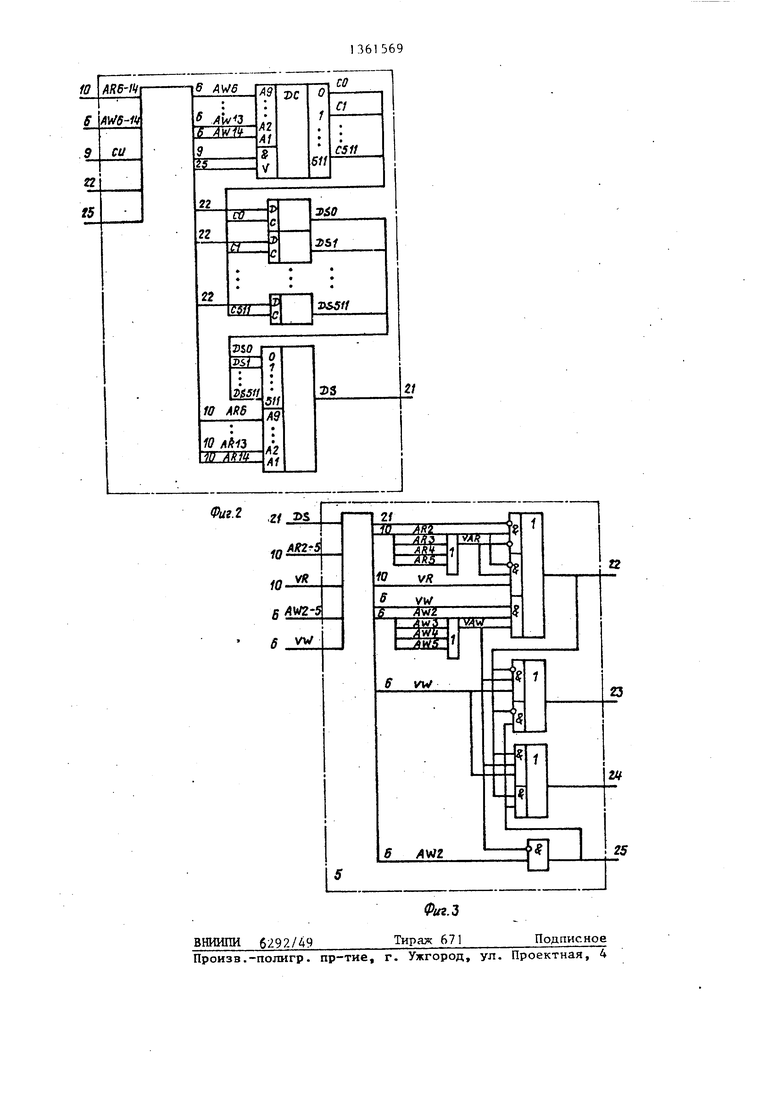

На фиг. 1 приведена структурная схема предпагаемого устройства; на фиг, 2 - пример выполнения блока памяти дескрипторов (для объема памяти 512 адресов); Hk фиг, 3 - пример реализации шифратора.

Устройство содержит коммутаторы 1, и 1 адресов чтения, блоки 2, и 22 памяти дескрипторов, шифраторы 3 и 3, коммутаторы 4,-44 адресов, блоки 5,-54 оперативной памяти и коммутаторы h,-64 данных,

Кроме того, устройство содержит вход 7 первого адреса чтения (1AR, 1АВ1 - первый разряд первого адреса чтбния), вход 8 второго адреса чтения (2АК), вход 9 адреса записи (AW) входы 10 и 11 чтения, вход 12 записи, информационный вход 13, синхро входы 14 и 15, входы 16 и 17 коммутаторов 1( и 1г адресов чтения, выходы 18 блока 2, памяти дескрипторов,выходы 19 и 20 коммутаторов 4, и 4 адресов, выход 21 блока 2 памяти дескрипторов, выходы 22 и 23 коммутаторов 5 и 54 адресов, выходы 24-27 гшфра- Toj5a 3, , выходы 28 и 29 блоков 5у и Sj оперативной памяти, выходы 30-33 шифратора 3, выходы 34 и 35 блоков 5 и. 5 оперативной памяти и выходы 36-39 коммутаторов данных.

Коммутаторы 1, и 1 предназначены для вьщачи требуемого адреса чтения через коммутаторы 4, -44 адресов на входы блоков 5,-54 памяти. Каждая пара блоков 5,, 5 и 5, ,5 образует накопитель с двумя уровнями памяти - ОЗУ и СОЗУ, ОЗУ и СОЗУ имеют общие адресные и информационные цепи к различаются занимаемыми зонами в накопителях.

Блоки 2 и 22 памяти дескрипторов служат для хранения и выдачи дескрипторов при обращении к памяти второго уровня (СОЗУ), Дескрипторы DR, с выходов 18 и 21 указывают блок пймя- ти, в котором находится информация чтения по адресу А, Например, для блоков б, и 5 дескриптор с выхода 18 означает

DS-

О - информация Б блоке 3 ; I - информация в блоке 5,

Шифраторы 3, и 3 предназначены для формирования сигналов управления на выходах 24-27 и 30-33, которые имеют следующий смысл:

24- чтение из блока 5, ,

запись в блок 5 , новое значение дескриптора;

25- разрешение записи в блок 5,;

26- разрешение записи в блок

27- разрешение записи в блок памяти дескрипторов 2,,

Коммутаторы 6,-6 служат для подачи требуемой информации чтения на выходы 38 и 39 устройства.

Обозначим основную память (ОЗУ) через П, а память второго уровня (СОЗУ) через Р, Устройство вьтолня- ет следующий набор операций:

0

5

0

5

(Р1, Р2, РЗ) - чтение Р1, чтение 5 Р2, запись РЗ;

(П1, Р2, РЗ) т- чтение П1, чтение Р2, запись РЗ;

(-, Р2, ПЗ) - отсутствие чтения 1, чтение 2, запись ПЗ;

(Р1, -, ПЗ) - чтение 1, отсутствие чтения 2,запись ПЗ,

Таким образом, первое чтение и запись могут относиться как к ОЗУ, так и к СОЗУ, второе чтение всегда относится к СОЗУ, Если операция вклюг чает одно обращение к ОЗУ, то остальные относятся к СОЗУ,

При этом, если обращение к ОЗУ производится через блоки 5, и 5, то чтение из СОЗУ выполняется через блоки 5, и 5., и наоборот. Запись в СОЗУ производится дважды, в оба блока по, одному адресу. При выполнении операции (Р, Р2, РЗ) чтение по первому адресу Р1 производится из первого блока 5, и 5, чтение по второму адресу Р2 - из второго блока 5, и 5, а запись РЗ производится дважды, в оба блока памяти.

0 Каждый блок памяти выполняет следующий набор бесконфликтньпс операций:

(П1, Р2) - чтение ПТ, запись Р2;

(-, П2) - отсутствие чтения, запись П2; 5 (Р1, Р2) - чтение Р1, запись Р2,

В каждом такте блоки 5, .5 н 5, 5 получают по два адреса, записи и чтения, и выполняют по два бесконфликтных обращения. Дескрипторы с

3 оков

136

., и - опреде- блок памяти, вы- и блок памяти, вы- Зона памяти СОЗУ

дублируется в каждом блоке памяти

-

и

5,, 54- При этом по каждому адресу используется одна из двух ячеек, вторая свободна. Из двух СОЗУ, размещенных в блоках 5,, 5 и 5,, 5д, образуется одно общее СОЗУ с возможностью трех бесконфликтных обращений (два чтения и одна запись).

Адрес обращения к памяти ОЗУ имеет полную длину, например, для памяти емкостью 16К слов 14 разрядов (AR 1-1А, AW 1-14). Адрес обращения к памяти СОЗУ короче, так как объем этой памяти MBHbDie. В рассматриваемом примере адреса СОЗУ короче на 5 разрядов (AR 6-14, AW 6-14). Старший (первьй) разряд первого адреса чтения (1АЕ 1). определяет блок памяти, к которому- производится обращение

{Г- чтение чтение

из блоков 5,,5j; из блоков .

Шифраторы 3 и 3 формируют управляющие сигналы на выходах 24-27, 30-33, определяющие режим обращения к памяти. Коды старпшх разрядов адреса определяют режим обращения

AR AW

2-5 2-5

0000 - отсутствие обращения 1000 - обращение к СОЗУ; 0000 - обращение к ОЗУ,пер-

вый блок памяти;

1000 - обращение к ОЗУ,второй блок памяти.

При обращении к памяти ОЗУ разряды адреса 3-5 содержат хотя бы одну, единицу, т.е. код в этих разрядах не равен 000.

Так как адресные и информационные цепи памятей ОЗУ и СОЗУ совмещены, то конструктивно они могут быть размещены в одних и тех же БИС ЗУПВ, выпускаемых промьшшенностью. Например, в микросхемах емкостью 16К первые 1К адресов могут быть использованы для СОЗУ, а остальные - для памяти ОЗУ.

Устройство работает следующим об разом.

В начале такта на входы устройства подаются адреса обращения 1АЕ, 2AR, AW, которые могут относиться ка к ОЗУ, так и к СОЗУ, и сигналы - на выходы 7-15. Коммутаторы t к

1361

еде- ы-

под управлением с:нгиалг1 1AR 1 выдают требуемые адреса чтения с выхо/шв 16 и 17 на входы коммутаторов 4,,

4, и 4

0

0

5

4

которые передают их на

входы блоков 5,, 5 и 5,, 5, При обращении к памяти ОЗУ каждый блок памяти производит требуемое обращение, чтение или запись. При выполне-

НИИ обращения к СОЗУ в каждом блоке памяти сначала производится обращение по адресу чтения к блокам 2 и 2. Прочитанные дескрипторы с выходов 18 и 21 поступают в шифраторы

с 3, и 3, которые формируют сигналь; управления на выходах 24-27, 30-33. Затем блоки 5,, 5 и 5,, 3 выполняют заданные операции обращения, а блоки 2 и 2 запись нового значения дескрипторов.

Информация из блоков памяти поступает на входы кoм ryтaтopoв 6,-6 , которые выдают ее на выходы 38 и 39 устройства. Аналогично выполняется

5 смешанная операция одновременного обращения к памяти ОЗУ и СОЗУ.

Таким образом, в структуру оперативной памяти (ОЗУ) встроена память второго уровня (СОЗУ) с возможностью бесконфликтного обращения по нескольким (трем) адресам.

Формула и ;з обретения

Запоминающее устройство, содер-

5 жащее первый, второй, третий и четвертый блоки оперативной памяти, адресные входы которых подключены к выходам соответственно первого, второго, третьего и четвертого коммутаторов адресов, выходы первого и второго блоков оперативной памяти подключены к информационным входам первого коммутатора данных, выходы третьего и четвертого блоков оператив-

5 ной памяти подключены к информационным входам второго ком гутатора данных, первый и второй блоки памяти дескрипторов, входы адресов записи которых объединены и подключены к

О первым информационным входам первого, второго, третьего и четвертого коммутаторов адресов и являются входом адреса записи устройства, информационные входы и входы стробирова 5 ния первого, второго, третьего и четвертого блоков оперативной памяти объединены и являются соответственно информационным входом и первым синхровходом устройства, о т л и -

чающееся тем, что, с целью расширения области применения за сче организации обращения по нескольким адресам к блокам оперативной памяти, оно содержит первый и второй блоки коммутаторов адресов чтения, первый и второй мифраторы и третий и четвертый коммутаторы данных, выходы которых являются информационными вы- ходами устройства, первые и вторые информационные входы третьего и четвертого коммутаторов данных подключены к выходам соответственно первого и второго коммутаторов данных,вы- ход первого блока памяти дескрипторов подключен к первому входу первого шифратора, первый выход которого подключен к информационному входу первого блока памяти дескрипторов, к управляющим зходам первого и второго .коммутаторов адресов и первого коммутатора данных, второй, третий и четвертый выходы первого шифратора подключены к соответствующим входам записи первого блока оперативной памяти, второго блока оперативной памяти и первого блока памяти дескрипторов , выход второго блока памяти дескрипторов подключен к первому входу второго шифратора, первый выход которого подключен к информационному входу второго блока памяти дескрипторов и к управляющим входам третьего и четвертого коммутаторов адресов и второго коммутатора данных, второй, третий и четвертый выходы второго шифратора подключены к входам записи

соответственно третьего блока оперативной памяти, четвертого блока оперативной памяти и второго блока памяти дескрипторов, выходы первого коммутатора адресов чтения подключены к адресным входам адресов считывания первого блока памяти дескрипторов, к второму входу первого шифратора и к вторым информационным входам первого и второго коммутаторов адресов, выход второго коммутатора адресов считывания подключен к входам адресов считывания второго блока па- мяти дескрипторов, к второму входу второго шифратора и к вторым информационным входам третьего и четвертого коммутаторов адресов, информационные входы первой и второй групп первого и второго коммутаторов адресов счи- тьгоания объединены и являются соот- ветственуо входами адресов считьшания первой и второй групп устройства, управляющие входы первого и второго коммутаторов адресов считывания и третьего и четвертого коммутаторов данных объединены и являются старшим входом адреса считывания первой группы, третьи входы первого и второго , шифраторов являются соответственно первым и вторым входами чтения устройства, четвертые входы первого и второго шифраторов подключены к входам адреса записи первого блока памяти дескрипторов, пятые входы первого и второго шифраторов объединены и являются входом записи устройст - ва.

ВНИИПИ 6292/49

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Тираж 671

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1317479A1 |

| Устройство управления памятью | 1980 |

|

SU947866A1 |

| Устройство для преобразования сейсморазведочной информации | 1987 |

|

SU1497599A1 |

| Оперативное запоминающее устройство с контролем по Хэммингу | 1983 |

|

SU1127011A1 |

| Запоминающее устройство | 1985 |

|

SU1285539A1 |

| Сверхоперативное запоминающее устройство | 1985 |

|

SU1310897A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1989 |

|

SU1810891A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения запоминающих устройств с произвольным доступом. Цель изобретения - расширение области применения за счет организации обращения по нескольким адресам к блокам оперативной памяти. Устройство содержит коммутаторы 1,, 1 адреса, блоки 2 и . памяти дескрипторов, шифраторы 3, , 3,, блоки 5,- 5у оперативной памяти, коммутаторы 6,-6 данных. Цель достигается тем, что в структуру памяти встроена память второго уровня с возможностью бесконфликтного обращения по нескольким (трем) адресам. 3 ил. с 3t ел 05 |Х

| Мультипроцессорные системы и параллельные вычисления./Под ред | |||

| Ф.Энслоу | |||

| - М.: Мир, 1976, с | |||

| Способ запрессовки не выдержавших гидравлической пробы отливок | 1923 |

|

SU51A1 |

| Устройство управления памятью | 1980 |

|

SU947866A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-23—Публикация

1985-12-26—Подача