Изобретение относится к вычислительной технике и, в частности, к запоминающим устройствам для вычислительных машин, обладающих высокой производительностью.

Цель изобретения -- повышение быстро- действия устройства.

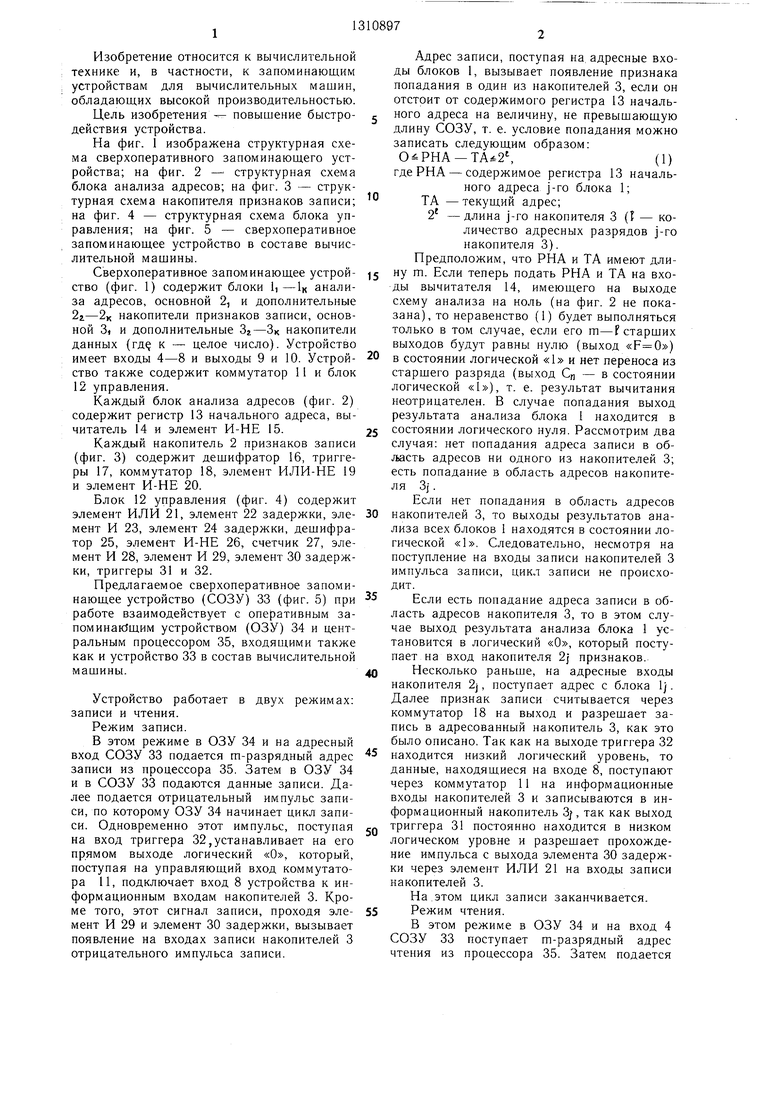

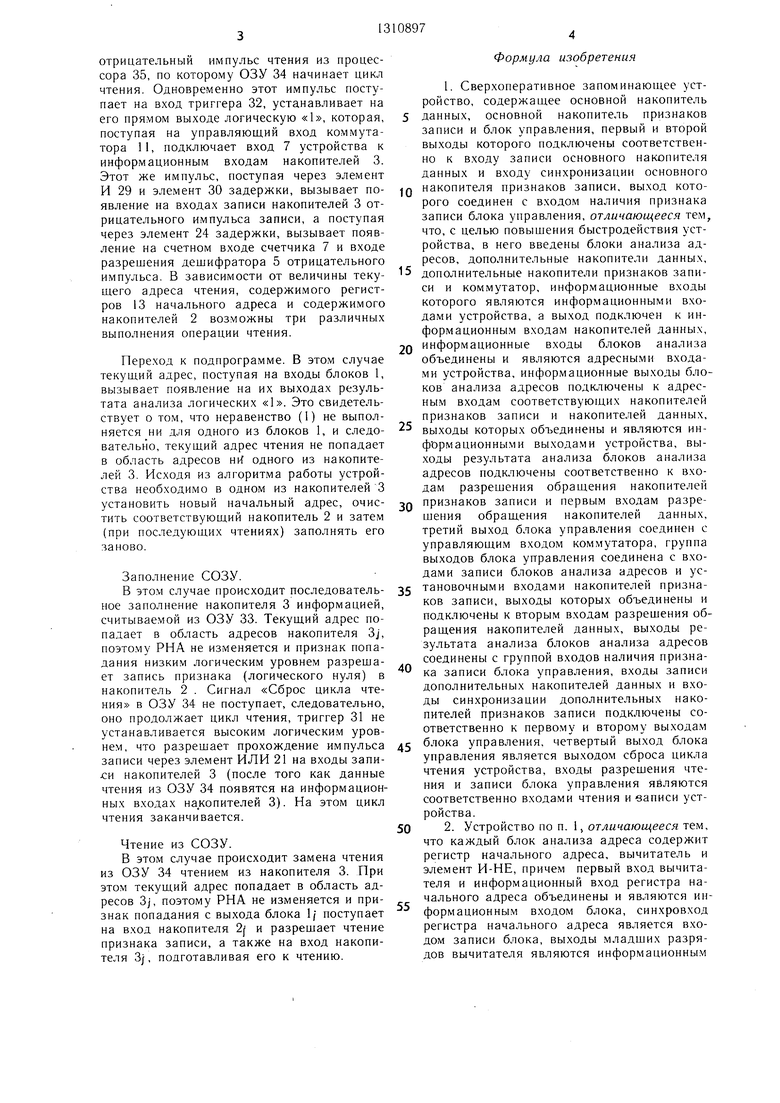

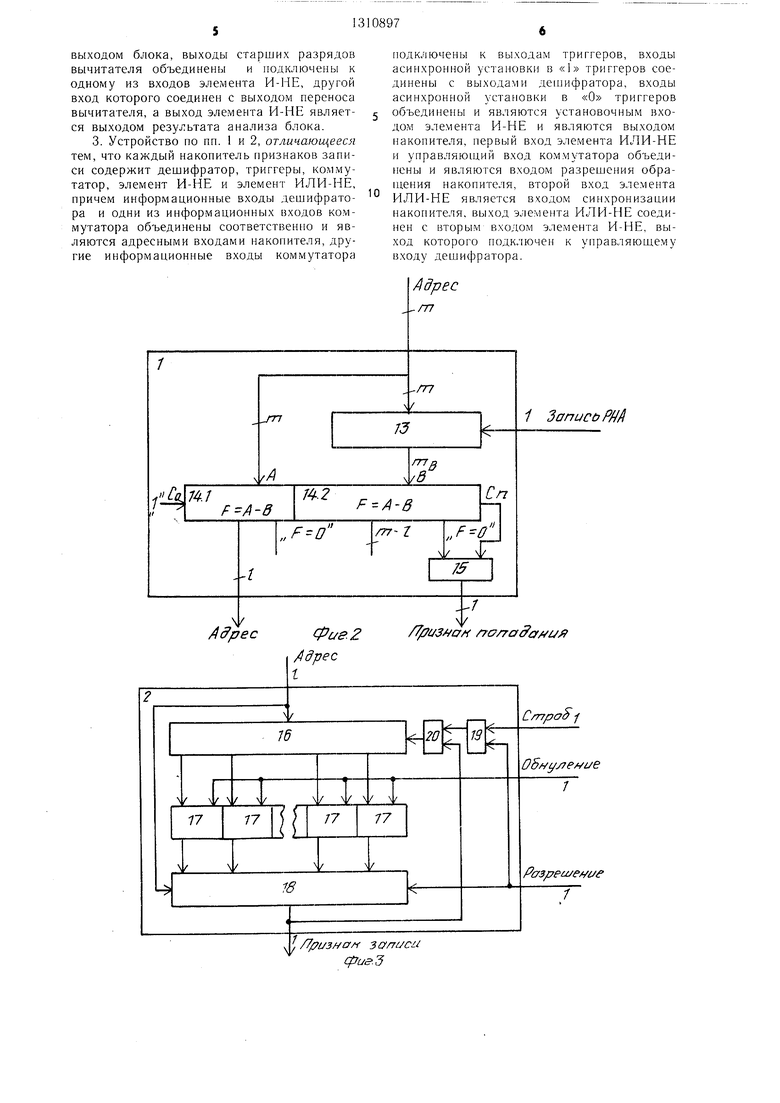

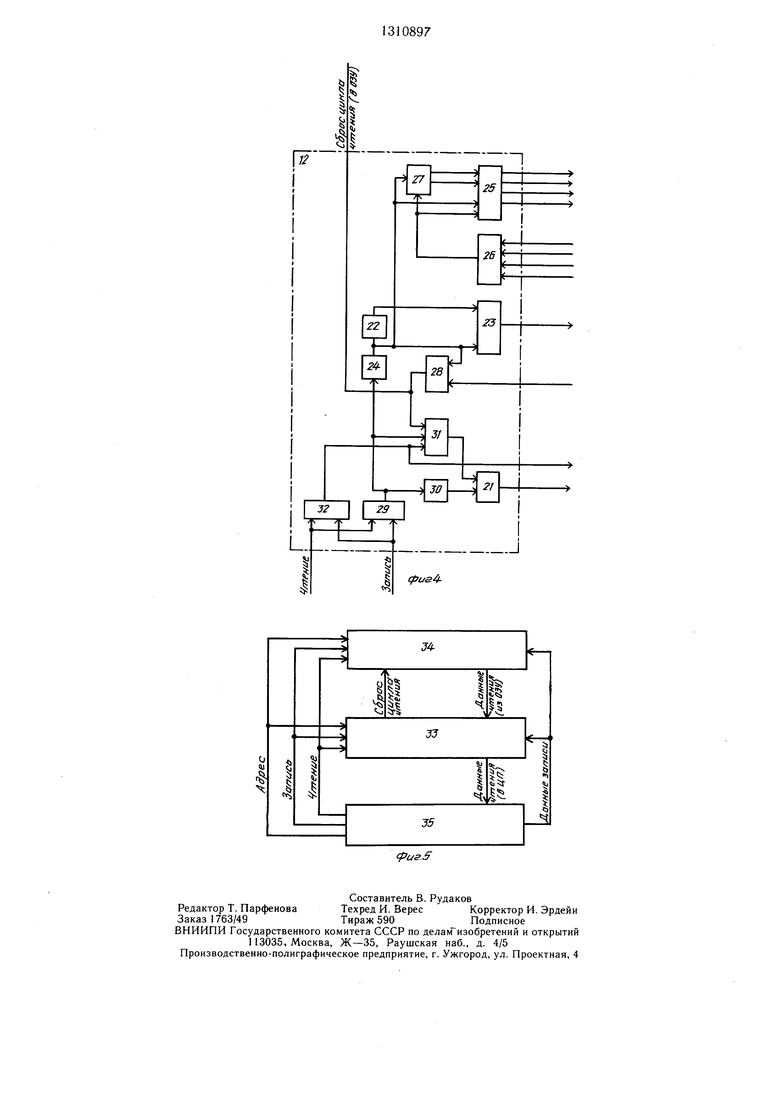

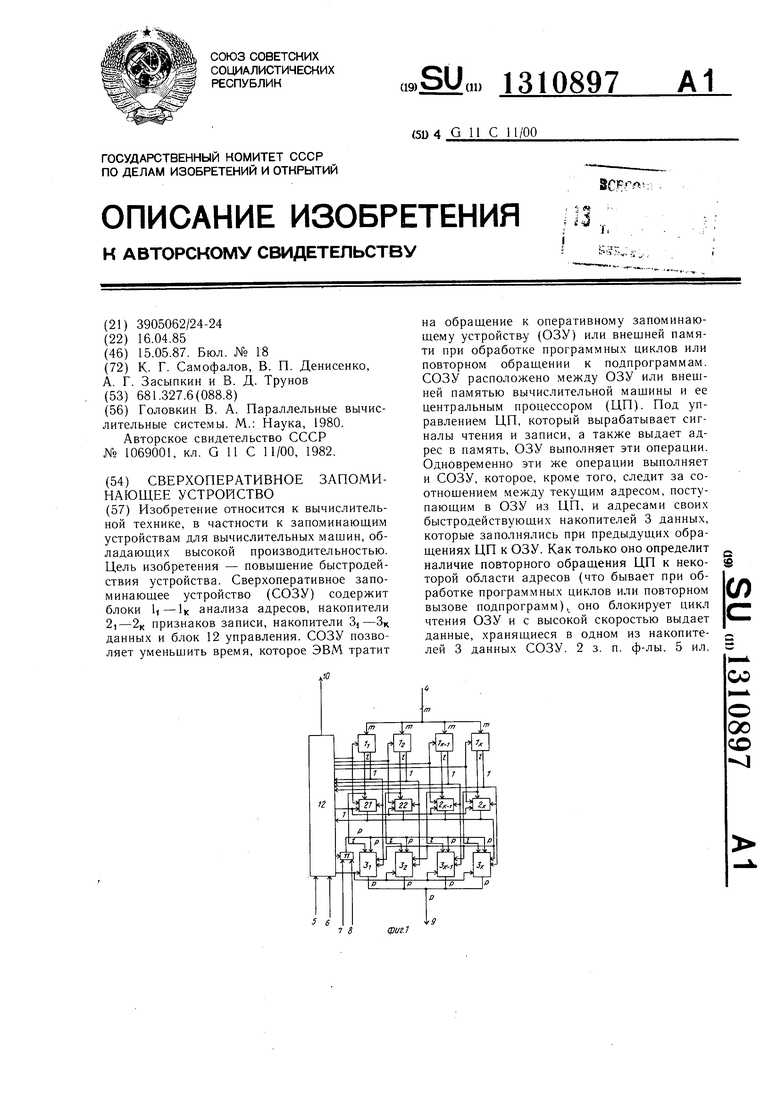

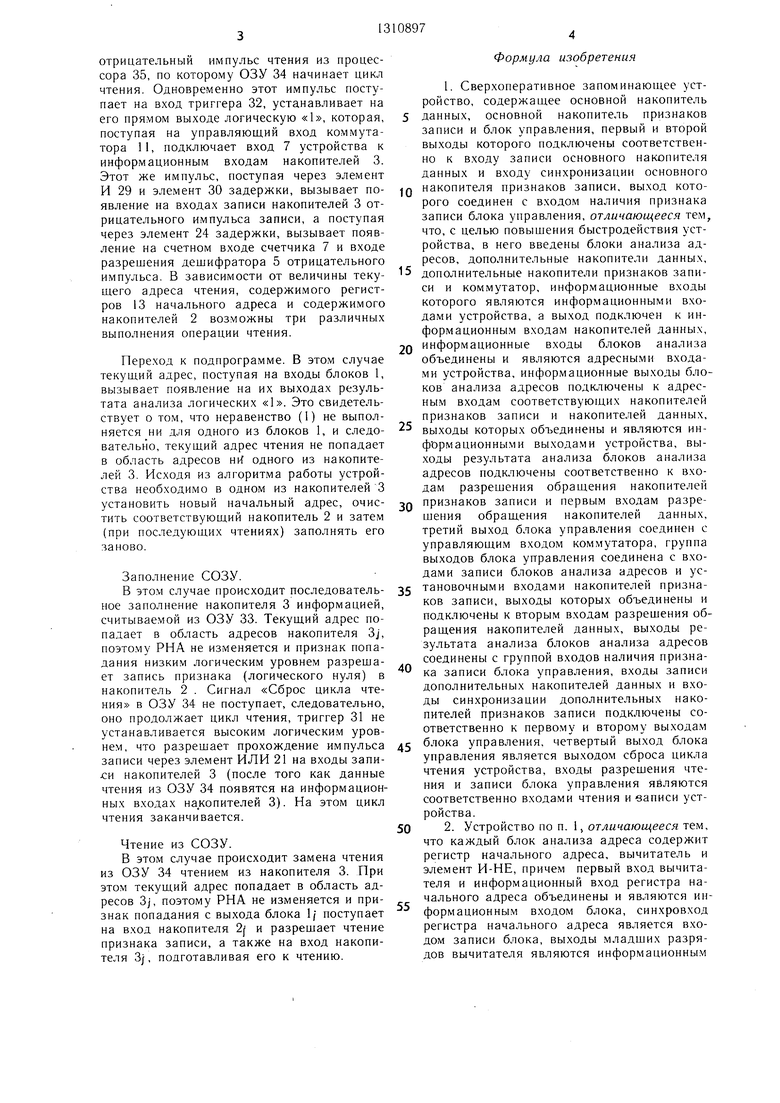

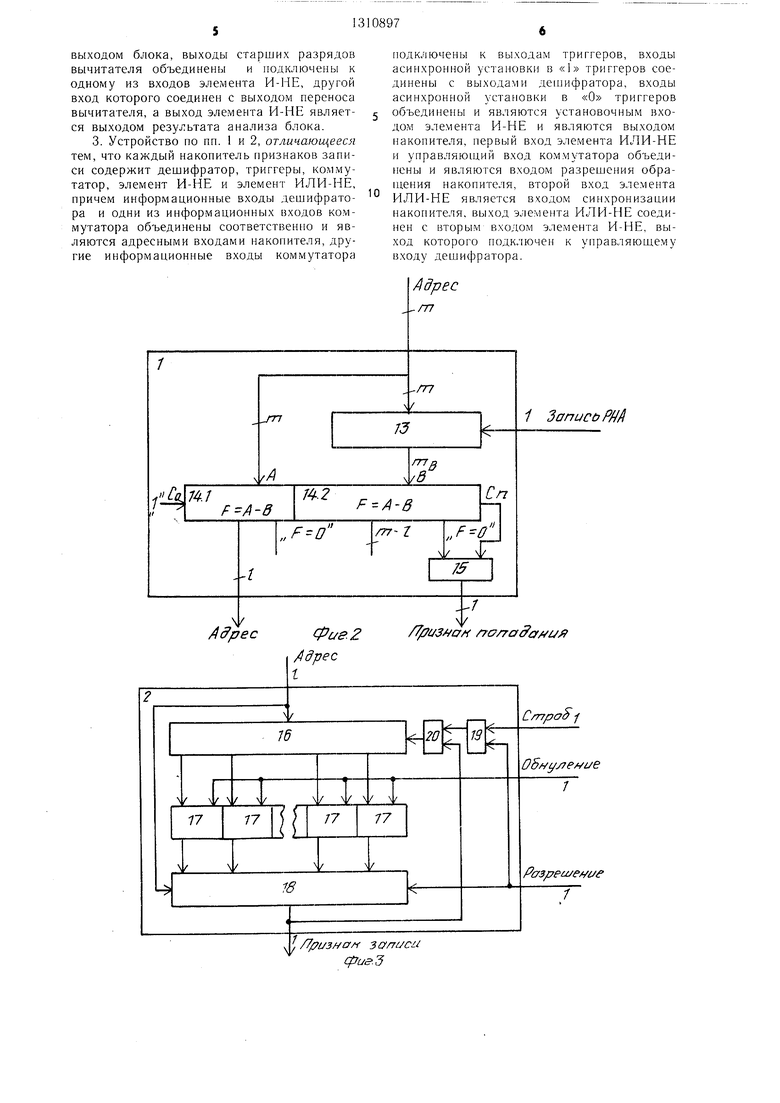

На фиг. 1 изображена структурная схема сверхоперативного запоминающего устройства; на фиг. 2 - структурная схема блока анализа адресов; на фиг. 3 - структурная схема накопителя признаков записи; на фиг. 4 - структурная схема блока управления; на фиг. 5 - сверхоперативное запоминающее устройство в составе вычислительной машины.

Сверхоперативное запоминающее устрой- ство (фиг. 1) содержит блоки 1, анализа адресов, основной 2, и дополнительные 2i-2к накопители признаков записи, основной 3 и дополнительные Зг-Зк накопители данных (гд к - целое число). Устройство имеет входы 4-8 и выходы 9 и 10. Устрой- ство также содержит коммутатор И и блок 12 управления.

Каждый блок анализа адресов (фиг. 2) содержит регистр 13 начального адреса, вы- читатель 14 и элемент И-НЕ 15.

Каждый накопитель 2 признаков записи (фиг. 3) содержит дещифратор 16, триггеры 17, коммутатор 18, элемент ИЛИ-НЕ 19 и элемент И-НЕ 20.

Блок 12 управления (фиг. 4) содержит элемент ИЛИ 21, элемент 22 задержки, эле- мент И 23, элемент 24 задержки, дешифратор 25, элемент И-НЕ 26, счетчик 27, элемент И 28, элемент И 29, элемент 30 задержки, триггеры 31 и 32.

Предлагаемое сверхоперативное запоминающее устройство (СОЗУ) 33 (фиг. 5) при работе взаимодействует с оперативным за- помина10щим устройством (ОЗУ) 34 и центральным процессором 35, входящими также как и устройство 33 в состав вычислительной машины.

Устройство работает в двух режимах: записи и чтения.

Режим записи.

В этом режиме в ОЗУ 34 и на адресный вход СОЗУ 33 подается т-разрядный адрес записи из процессора 35. Затем в ОЗУ 34 и в СОЗУ 33 подаются данные записи. Далее подается отрицательный импульс записи, по которому ОЗУ 34 начинает цикл записи. Одновременно этот импульс, поступая на вход триггера 32,устанавливает на его прямом выходе логический «О, который, поступая на управляющий вход коммутатора 11, подключает вход 8 устройства к информационным входам накопителей 3. Кроме того, этот сигнал записи, проходя эле- мент И 29 и элемент 30 задержки, вызывает появление на входах записи накопителей 3 отрицательного импульса записи.

5 0

5

0

0

Q 5

Адрес записи, поступая на адресные входы блоков 1, вызывает появление признака попадания в один из накопителей 3, если он отстоит от содержимого регистра 13 начального адреса на величину, не превышающую длину СОЗУ, т. е. условие попадания можно записать следующим образом: -TAi-2,(1)

где РНА - содержимое регистра 13 начального адреса j-ro блока 1; ТА - текущий адрес; 2 - длина j-ro накопителя 3 ( - количество адресных разрядов j-ro накопителя 3).

Предположим, что РНА и ТА имеют длину т. Если теперь подать РНА и ТА на входы вычитателя 14, имеющего на выходе схему анализа на ноль (на фиг. 2 не показана), то неравенство (1) будет выполняться только в том случае, если его ш-F старших выходов будут равны нулю (выход ) в состоянии логической «1 и нет переноса из старшего разряда (выход Сп - в состоянии логической «1), т. е. результат вычитания неотрицателен. В случае попадания выход результата анализа блока 1 находится в состоянии логического нуля. Рассмотрим два случая: нет попадания адреса записи в область адресов ни одного из накопителей 3; есть попадание в область адресов накопителя 3j.

Если нет попадания в область адресов накопителей 3, то выходы результатов анализа всех блоков 1 находятся в состоянии логической «1. Следовательно, несмотря на поступление на входы записи накопителей 3 импульса записи, цикл записи не происходит.

Если есть попадание адреса записи в область адресов накопителя 3, то в этом случае выход результата анализа блока 1 установится в логический «О, который поступает на вход накопителя 2 признаков.

Несколько раньше, на адресные входы накопителя 2j, поступает адрес с блока Ij. Далее признак записи считывается через коммутатор 18 на выход и разрешает запись в адресованный накопитель 3, как это было описано. Так как на выходе триггера 32 находится низкий логический уровень, то данные, находящиеся на входе 8, поступают через коммутатор 11 на информационные входы накопителей 3 и записываются в информационный накопитель 3/, так как выход триггера 31 постоянно находится в низком логическом уровне и разрешает прохождение импульса с выхода элемента 30 задержки через элемент ИЛИ 21 на входы записи накопителей 3.

На,этом цикл записи заканчивается.

Режим чтения.

В этом режиме в ОЗУ 34 и на вход 4 СОЗУ 33 поступает т-разрядный адрес чтения из процессора 35. Затем подается

отрицательный импульс чтения из нроцес- сора 35, по которому ОЗУ 34 начинает цикл чтения. Одновременно этот импульс поступает на вход триггера 32, устанавливает на его прямом выходе логическую «1, которая, поступая на управляющий вход коммутатора 11, подключает вход 7 устройства к информационным входам накопителей 3. Этот же импульс, поступая через элемент И 29 и элемент 30 задержки, вызывает появление на входах записи накопителей 3 отрицательного импульса записи, а поступая через элемент 24 задержки, вызывает появление на счетном входе счетчика 7 и входе разрешения дешифратора 5 отрицательного импульса. В зависимости от величины теку- ш.его адреса чтения, содержимого регистров 13 начального адреса и содержимого накопителей 2 возможны три различных выполнения операции чтения.

Переход к подпрограмме. В этом случае текущий адрес, поступая на входы блоков 1, вызывает появление на их выходах результата анализа логических «1. Это свидетельствует о том, что неравенство (1) не выполняется ни для одного из блоков 1, и следовательно, текуший адрес чтения не попадает в область адресов нр{ одного из накопителей 3. Исходя из алгоритма работы устройства необходимо в одном из накопителей 3 установить новый начальный адрес, очистить соответствующий накопитель 2 и затем (при последующих чтениях) заполнять его заново.

Заполнение СОЗУ.

В этом случае происходит последовательное заполнение накопителя 3 информацией, считываемой из ОЗУ 33. Текущий адрес попадает в область адресов накопителя 3j, поэтому РНА не изменяется и признак попадания низким логическим уровнем разреща- ет запись признака (логического нуля) в накопитель 2 . Сигнал «Сброс цикла чтения в ОЗУ 34 не поступает, следовательно, оно продолжает цикл чтения, триггер 31 не устанавливается высоким логическим уровнем, что разрешает прохождение импульса записи через элемент ИЛИ 21 на входы запи- .си накопителей 3 (после того как данные чтения из ОЗУ 34 появятся на информационных входах накопителей 3). На этом цикл чтения заканчивается.

Чтение из СОЗУ.

В этом случае происходит замена чтения из ОЗУ 34 чтением из накопителя 3. При этом текущий адрес попадает в область адресов 3j, поэтому РНА не изменяется и признак попадания с выхода блока 1/ поступает на вход накопителя 2j и разрешает чтение признака записи, а также на вход накопителя 3|, подготавливая его к чтению.

Формула изобретения

1. Сверхоперативное запоминающее устройство, содержащее основной накопитель 5 данных, основной накопитель признаков записи и блок управления, первый и второй выходы которого подключены соответственно к входу записи основного накопителя данных и входу синхронизации основного Q накопителя признаков записи, выход которого соединен с входом наличия признака записи блока управления, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блоки анализа адресов, дополнительные накопители данных, 15 дополнительные накопители признаков записи и коммутатор, информационные входы которого являются информационными входами устройства, а выход подключен к информационным входам накопителей данных,

Q информационные входы блоков анализа объединены и являются адресны.ми входами устройства, информационные выходы блоков анализа адресов подключены к адресным входам соответствующих накопителей признаков записи и накопителей данных,

выходы которых объединены и являются информационными выходами устройства, выходы pe3yvabTaTa анализа блоков анализа адресов подключены соответственно к входам разрешения обращения накопителей

Q признаков записи и первым входам разрешения обращения накопителей данных, третий выход блока управления соединен с управляющим входом коммутатора, группа выходов блока управления соединена с входами записи блоков анализа адресов и ус5 тановочными входами накопителей признаков записи, выходы которых объединены и подключены к вторым входам разрешения обращения накопителей данных, выходы результата анализа блоков анализа адресов соединены с группой входов наличия призна ка записи блока управления, входы записи дополнительных накопителей данных и входы синхронизации дополнительных накопителей признаков записи подключены соответственно к первому и второму выходам

5 блока управления, четвертый выход блока управления является выходом сброса цикла чтения устройства, входы разрещения чтения и записи блока управления являются соответственно входами чтения и ваписи устройства.

0 2. Устройство по п. 1, отличающееся тем, что каждый блок анализа адреса содержит регистр начального адреса, вычитатель и элемент И-НЕ, причем первый вход вычита- теля и информационный вход регистра начального адреса объединены и являются информационным входом блока, синхровход регистра начального адреса является входом записи блока, выходы младших разрядов вычитателя являются информационным

5

выходом блока, выходы старших разрядов вычитателя объединены и подключены к одному из входов элемента И-НЕ, другой вход которого соединен с выходом переноса вычитателя, а выход элемента И-НЕ является выходом результата анализа блока.

3. Устройство по пп. 1 и 2, отличающееся тем, что каждый накопитель признаков записи содержит дешифратор, триггеры, коммутатор, элемент И-НЕ и элемент ИЛИ-НЕ, причем информационные входы дешифратора и одни из информационных входов коммутатора объединены соответственно и являются адресными входами накопителя, другие информационные входы коммутатора

подключены к выходам триггеров, входы асинхронной установки в «1 триггеров соединены с выходами дешифратора, входы асинхронной установки в «О триггеров объединены и являются установочным входом элемента И-НЕ и являются выходом накопителя, первый вход элемента ИЛИ-НЕ и управляюпхий вход коммутатора объеди- нены и являются входом разрешения обра- пхения накопителя, второй вход элемента ИЛИ-НЕ является входом синхронизации накопителя, выход элемента ИЛИ-НЕ соединен с вторым входом элемента И-НЕ, выход которого подключен к управляющему входу дешифратора.

Адрес

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1982 |

|

SU1069001A1 |

| Оперативное запоминающее устройство с контролем по Хэммингу | 1983 |

|

SU1127011A1 |

| Программируемое устройство для контроля цифровых систем | 1986 |

|

SU1439588A1 |

| Устройство для преобразования сейсморазведочной информации | 1987 |

|

SU1497599A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Сверхоперативное запоминающее устройство | 1985 |

|

SU1312584A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам для вычислительных машин, обладающих высокой производительностью. Цель изобретения - повыщение быстродействия устройства. Сверхоперативное запоминающее устройство (СОЗУ) содержит блоки 1,-IK анализа адресов, накопители 2,-2 признаков записи, накопители 3t-3 данных и блок 12 управления. СОЗУ позволяет уменьшить время, которое ЭВМ тратит на обращение к оперативному запоминающему устройству (ОЗУ) или внещней памяти при обработке программных циклов или повторном обращении к подпрограммам. СОЗУ расположено между ОЗУ или внешней памятью вычислительной машины и ее центральным процессором (ЦП). Под управлением ЦП, который вырабатывает сигналы чтения и записи, а также выдает адрес в память, ОЗУ выполняет эти операции. Одновременно эти же операции выполняет и СОЗУ, которое, кроме того, следит за со- отнощением между текущим адресом, поступающим в ОЗУ из ЦП, и адресами своих быстродействующих накопителей 3 данных, которые заполнялись при предыдущих обращениях ЦП к ОЗУ. Как только оно определит наличие повторного обращения ЦП к некоторой области адресов (что бывает при обработке программных циклов или повторном вызове подпрограмм), оно блокирует цикл чтения ОЗУ и с высокой скоростью выдает данные, хранящиеся в одном из накопителей 3 данных СОЗУ. 2 з. п. ф-лы, 5 ил. i (Л S 6 со 00 со фигЛ

/77

1

А

П.1

,. -г 1

-I

, /77

/

1 Запись РН/1

NK / ffpec

Фс/а.2

/Idре с

16

f

f /

/ / f

17

77

77

/

18

/7jyu3Haf .и cfJue.3

/

a/raffcf i/

C/77poS {

20

19

7

Paapeu/ff ije

/

| Головкин В | |||

| А | |||

| Параллельные вычислительные системы | |||

| М.: Наука, 1980 | |||

| Оперативное запоминающее устройство | 1982 |

|

SU1069001A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-05-15—Публикация

1985-04-16—Подача