с -единичным и нулевым выходами триггера управления, счетный вход которого соединен с выходом первого элемента И, прямой вход которого соединен с третьим выходом блока синхронизации инверсный вход первого элемента И соединен с инверсным входом блока элемента И, с первым управляющим входом коммутатора адреса и с первым управляющим выходом первого регистра микрокоманд, второй управляющий выход которого соединен с входом чтекия-записи регистракодов логических условий и с инверсным входом второго элемента И, прямой вход которого соединен с выходом первого мультиплексора, группа управляющих.входов которого соединена с группой выходов кода логических условий первого регистра микрокоманд и с группой .информационных входов регистра кодов логических условий, группа выходов которого соединена с группой управляющих -входов второго мультиплексора, группа информационных входдев которого соединена с группой информационных входов первого мультиплексора k является группой входов логических условий устройства, вьЕХод второго мультиплексора соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом модифицируемого разряда адреса следующей микрокоманды второго регистра микрокоманд, выход первого элемента ИЛИ соединен с п-м информационным входом третьей груттпы коммутатора адреса, п-ый информационизш вход второй группы которого соединен с- выходом второго элемента ИЛИ, первый вход которого соединен с зькодом модифицируемого разряда адреса следующей микрокоманды первого регистра микрокоманд, второй вход второго элемента ИЛИ соединен с вь ходом второго элемента И Ьторой управляющий вход коммутатора а,дреса соединен с выходом третьего элемента ИЛИ, первьй и второй -входы которого соединены соответственно с m ми выходами кода операции первого и второго регистров микрокоманд, выходы модифицируемого и немодифицируемых разрядов адреса следующей микрокоманды Первого регистра микрокоманд соединен с прямыми входами блока элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммное управляющее устройство | 1987 |

|

SU1527634A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

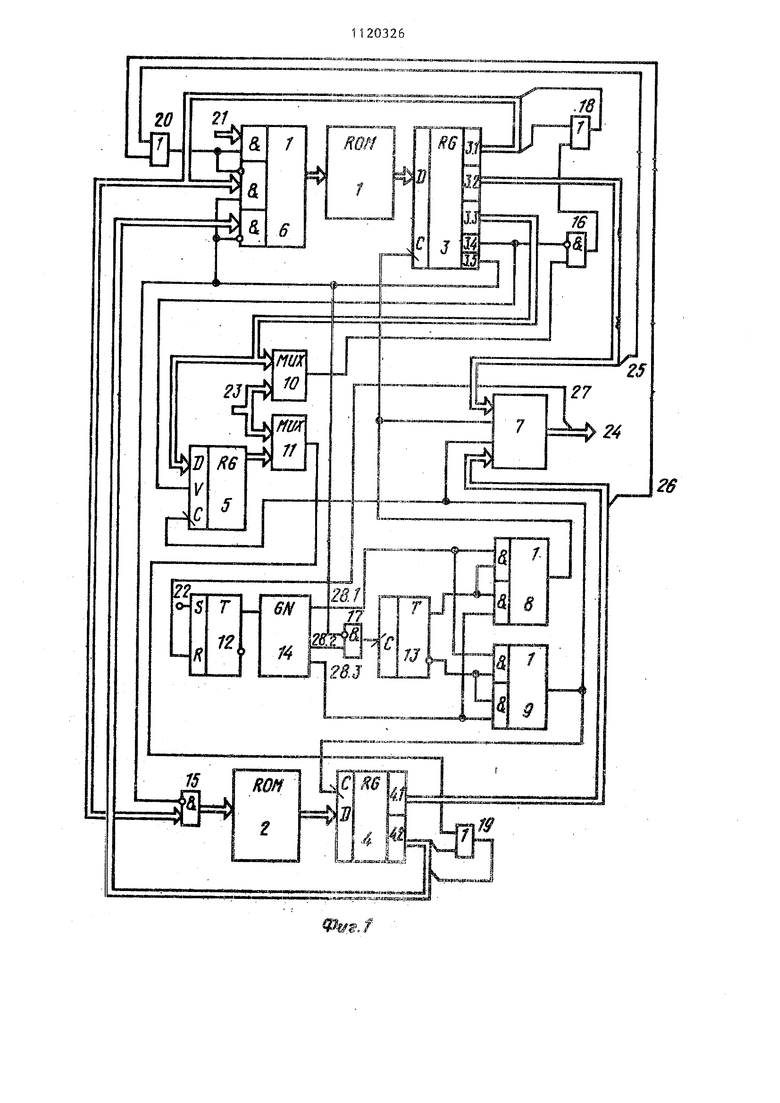

МИКРОПРОГРАМ-гаОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры микрокоманд, блок синхронизации, коммутатор адреса, триггер пуска, триггер управления, первый и второй элементы И, причем первая группа информационных входов коммутатора адреса является группой входов кода команды устройства, выход коммутатора адреса соединен с адресным входом первого блока памяти микрокоманд, выход которого соединен с информационным входом первого регистра микрокоманд, j выходов ( j 1, 2, ,,,, h -1, где п- разрядность кода адреса) немодифицируемых разрядов кода адреса следующей микрокоманды которого соединены с j информационными взводами второй группы ко о татора адреса, j информационных входов третьей группы которого соединены с выходами немодифицируемых разрядов кода адреса следукяцей микрокоманды второго регистра микрокоманд, информационный вход второго регистра микрокоманд соединен с выходом второго блока памяти микрокоманд, вход установки в 1 триггера пуска является входом пуска устройства, выход которого соединен с входом запуска блока синхронизации, отличающееся тем, что, с целью сокращения оборудования, оно содержит регистр кодов логических условий, первый и второй коммутаторы синхроимпульсов, первый и второй мультиплексоры, блок элементов И, первьй второй и третий элементы ИЛИ и коммутатор микроопераций, причем К выходов (К 1,2, m-1 , где т- разрядность кода операций) кода операции первого и второго регистров микрокоманд соединены соответственно с Ik информационными входами первой и рой групп комм -таторамикроопераций, k выходов которого являются управляющими выходами устройства,т-и выход коммутатора микроопераций соединен с входом установки в О, триггера пуска, первый управляющий вход кoм ryтaтoра микроопераций соединен с входом синхронизации первого регистра микрокоманд и с выходом первого коммутатора синхроимпульсов, второй управляющий вход коммутатора микроопераций соединен с входами синхронизации, второго регистра микрокоманд и регистра кодов логических сигналов и с выходом второго коммутатора синхроимпульсов, первьй информационный вход которого соединен с первым информационным входом первого коммутатора синхроимпульсов и с первым выходом блока синхронизации, второй выход которого соединен с вторыми информационными входами первого и второго коммутаторов синхроимпульсов, управляющие входы которых соединены соответственно

Изобретение относится к вычислительной технике и может быть использовано при разработке микропрограммных управляющих устройств для ЗШМ и других систем.

Известно микропрограммное устройство управления, содержащее два блока памяти, два регистра адреса, два триггера, два элемента И и два блока проверки логических условий Г

Недостатком устройства является большой объем оборудования, обусловленный хранением кодов логических условий в первом и втором блоках памяти.

Известно также микропрогра -(мное устройство управления, содержащее первый и второй запоминающие блоки, регистр адреса, триггер, блок проверки условий первый и второй элементы И 2.

Недостатками указанного устройства являются низкое быстродействие,

вызванное большим временем; цикла формирования и выдачи микрокоманд, а также низкая экoнo ичнocть, обусловленная необходимостью хранения в обоих блоках памяти кодов логических условий.

Наиболее близким к изобретению по технической сущности и достигаемому положительному эффекту является микропрограммное устройство управления, содержащее два блока памяти микрокоманд два регистра микрокоманд, два регистра адреса, два триггера два элемента И, два коммутатора, блок синхронизации, причем выходы микроопераций первого и второго блоков па1-1яти микрокоманд являются nepebnt и вторьв выходами микроопераций устройства соответственно, управлякшще вькоды первого и второго блоков паt«5TH микрокоманд соединены со входами соответственно первого и второго триггеров, единичные вькоды которых соединены с первыми входами соответственно первого и второго элементов И, выходы которых соединены с управляющими входами соответственно пер вого и второг о блоков памяти, первьй и второй выходы блока синхронизации соединены соответственно с вторым входом первого элемента И, первым управляющим входом первого коммутатора и вторым входом второго элемента И, nepBbiM управляющим входом второго ком мутатора, выходы первого и второго коммутаторов соединены с первыми входами соответственно первого и второго регистров адреса, первые выходы которых соединены соответственно с входами адреса первого и второго блоков памяти микрокоманд, выходы адреса первого и второго блоков памяти соединен с вторьми входами соответственно первого и второго регистров адреса, вторые выходы которых соединены с информационными входами соответственно первого и второго коммутаторов, вторые управляющие входы которых соединены с нулевыми выходами первого и второго триггеров соответственно Сз 3. Недостатками известного устройств являются большой объем блоков памяти и низкий коэффициент использования оборудования вследствие неэффективного размещения в них кодов логических условий. Микрокоманды, хранимые в первом и втором блоках памяти, содержат пол микроопераций разрядностью tn,, поле адреса разрядностью и и поле кода логических условий разрядностью m. Поскольку поле кода логических условий используется только в микрокомандах ветвления, число которых Ng значительно меньше общего числа микрокоманд N,To каждьй из блоков памяти имеет ,)m избыточных ячеZ 41 л ек, незаполненных полезной информацией. Поскольку на практике обычно выполняется неравенство N.2Ng , то, следовательно, существует возможность исключения поля кода логических условий в одном из блоков памяти В известном устройстве возможность связания всех кодов логических условий в один блок памяти и дальней шего использования с соответствующей принадлежностью микрокомандам из раз личных блоков памяти не реализована Это обуславливает большую избыточность оборудования. Избыточный объем блока памяти ведет к увеличению затрат на производство микропрограммных устройств, так как основные затраты оборудования (до 90%) приходятся на блок памяти. Целью изобретения является сокращение оборудования за счет увеличения коэффициента использования памяти микрокоманд. Указанная цель достигается тем, что в микропрограммное устройство управления, содержащее первый и второй блоки памяти микрокоманд, первьй и второй регистры микрокоманд, блок синхронизации, коммутатор адреса, триггер пуска, триггер управления, первый и второй элементы И, причем первая группа информационных входов коммутатора адреса является группой входов кода команды устройства, выход коммутаторов адреса соединен с адресным входом первого блока памяти, микрокоманд, выход которого соединен с информационным входом первого регистра микрокоманд, j выходов (j 1,2,...,п-1, где п - разрядность кода адреса) немодифицируемых разрядов кода адреса следующей микрокоманды которого соединены с j информационными входами второй группы коммутатора адреса, j информационных входов третьей группы которого соединень с выходами немодифицируемых разрядов кода адреса следуклцей микрокоманды второго регистра микрокоманд, информационный вход второго регистра микрокоманд соединен с выходом второго блока памяти микрокоманд, вход установки в 1 триггера пуска является входом пуска устройства, выход которого соединен с входом запуска блока синхронизации, введены регистр кодов логических условий, первый и второй коммутаторы синхроимпульсов, первьй и второй мультиплексоры, блок элементов И, первый, второй и третий элементы ИЛИ и коммутатор микроопераций, причем k выходов (1 1,2, т-1, где т- разрядность кода операции) кода операции первого и второго регистров микрокоманд соединены соответственно с 1 информационными входами первой и второй групп коммутаторов микроопераций, 1 выходов которого являются управляющими выходами устройства, m-и выход коммутатора микроопераций соединен с входом установки в О триггера пуска, первый управляющий вход коммутатора мик роопераций соединен с входом синхронизации первого регистра микрокоманд и с выходом первого коммутатора синх роимпульсов, второй управляющий вход коммутатора микроопераций соединен с входами синхронизации, второго регистра микрокоманд и регистра кодов логических сигналов и с выходом второго коммутатора синхроимпульсов,, первьй информационньш вход которого соединен с первьм информационным вхо дом первого коммутатора синхроимпуль сов и с первым выходом блока синхронизации, второй выход которого соеди нен с вторьими информационными выходами первого и второго коммутаторов синхроимпульсов, управляющие входы которых соединены соответственно с единичным и нулевым выходами триггера управления, счетный вход которо;го соединен с выходом первого элемента И, прямой вход которого соединен с третьим выходом блока синхронизации, инверсный Вход первого элемента И соединен с инверсным входом блока элементов И, с первым управляющим входом коммутатора адреса и с первым управляющим выходом первого регистра микрокоманд, второй управляющий выход которого соединен с входом чтения-записи регистра кодов логических условий и с инверсным входом второго элемента И, прямой вход которого соединен е выходом пер вого мультиплексора,, группа управляющих входов которого соединена с гру пой вькодов кода логических условий первого регистра микрокоманд и с гру , -. ПОИ информационных входов регистра кодов логических условий, группа выходов которого соединена с группой управляющих входов второго мультиплексора, группа информационных вхо дов которого соединена с группой информационных входов первого мультиплексора и является группой входов логических условий устройства, выход второго мультиплексора соединен с первым входом первого элемента И1М, ВТО1ЮЙ вход которого соединен с выходом модифицируемого разряда адреса с;ледукяцей микрокоманды второго регистра микрокоманда выход первого элемента ИЛИ соединен с гч-м информационным входом третьей грзшпь коммутатора адреса, .п-и информационньй вход второй группы которого соединен с выходом Еторого элемента ИЛИ, пер-: вый вход которого coe.ди.ea с зькодом модифицируемого разряда адреса следующей ми:крокоманды первого регистра Ф1Крококанд5 второй вход второго элемента ИЛИ соединен с выходом второго элемента И, второй управляющий вход коммутатрра адреса соединен с выходом третьего элемента ИЛИ, первый и второй входы которого соединены соответственно с т-ми выходами кеда операции первого и второго регистров микрокоманд, выходы модифицируемого и немодифицируемых разрядов адреса следующей микрокоманды первого регистра микрокоманд соединен с прямыми входами блока элементов И. Сущность изобретения состоит в повьппении экономичности и коэффициента использования оборудования устройства путем хранения кодов логических условий в одном (первом) блоке памяти микрокоманд, заблаговременного считывания (за-один такт дс проверки) кода логических условий для микрокоманда хранящихся во втором блоке памяти и введения меток для микрокоманд, образ тощих короткие линейные последовательности (т,е-, последовательностИ; содержащие одну микрокоманду), с це.пьш повторного обращения к первому блоку памяти. Рассмотрим сущность предлагаемого изобретения на np.vmepe выполнения фрагмента микропрограммы, описываемого следующей логической схемой алгоритма„..A .tЛ .... ;. -1 1-.-1 i-i-1 J 1+3 J-f-. ..S XT л. ft. i + 2 1+3 микрокомандгз,; хранимые ;,,ii-3. 3 первом блоке памяти. , ,.с.77ГТ микрокоманды, хранимые г-1 f ь 1,113 во втором блоке памяти, -и ( )-е лог -гческие J условия, Код логического условия Х; , проверяемого в микрокоманде А,,,, , написанный во втором блоке памяти, хранится в свободном поле кода логических условий г-дакрокомакды А, записанного в кервом блоке памяти Благоаря этовд исключается поле кода логических условий во втором блоке памяти, снижается объем первого блока памяти, не заполненный полезной нформацией; и повышается козСгфициент использования оборудования устройст ва в целом. Введение регистра логических условий и обусловленных им связей поз воляет запоминать на один такт код логических условий для микрокоманды из второго блока памяти, в котором поле логических условий отсутствует Введение коммутаторов синхроимпульсов и обусловленных ими связей позволяет осуществлять перетактовку синхроимпульсов при считывании нескольких микрокоманд последовательно из первого блока памяти. Использование группы элементов И обеспечивает управление передачей кода адреса следующей микрокоманды во второй блок памяти. Введение первого и второго мультиплексоров, первого и второго элемента ИЛИ и обусловленных ими связей позволяет осуществлять модифика цию адреса в зависимости от значени проверяемого логического условия. Введение новых связей для первог и второго элементов И позволяет упр лять подачей импульсов в триггер управления и передачей значения про веряемого логического условия от пе вого мультиплексора на второй элемент ИЛИ соответственно. Введение третьего элемента ИЛИ и обусловленных им связей позволяет формировать сигнал конца команды дл управления подачей кода очередной операци. Таким образом, введение новых эл ментов и связей позволяет повысить экономичность и коэффициент использования оборудования устройства за |счет группирования информации о кодах логических условий в одном блок памяти. На фиг. 1 представлена функциона ная схема микропрограммного устройства управленияi на фиг. 2 - функци ональная схема коммутатора микроопе раций; на фиг. 3 - функциональная схема блока синхронизации, на фиг. 4 и 5 - временные диаграммы работы бл ка синхронизации и микропрограммного устройства соответственно. Устройство содержит первый 1 и второй 2 блоки памяти ьоткрокоманд, первый 3 и второй 4 регистры микрокоманд, регистр 5 кодов логических условий, коммутаторы 6 и 7 адреса микроопераций, первый 8 и второй 9 KOMf-iyTaTopb синхроимпульсов, первый 10 и второй 11 мультиплексоры, триггер 12 пуска, триггер 13 управления, блок 14 синхронизации, блок элементов И 15, второй 16 и первый 17 элементы, второй 18, первьй 19 и третий 20 элементы ИЛИ, группу входов 21 кода команды устройства, вход 22 пуска устройства, группу входов 23 логических условий устройства, управляющие выходы 24 устройства, выходы 25 и 26 микрооперации конца команды первого 3 и второго 4 регистров , выход 27 микрооперации кон- ца работы устройства, выходы 28, 28 и 28j генаратора 14. Коммутатор 7 микроопераций (фиг.2) содержит первый 29 и второй 30 блоки элементов И, блок элементов ИЛИ 31,.. первьй 32 и второй 33 элементы задержки. Блок 14 синхронизации (фиг. 3) содержит генератор 34 импульсов, первьй 35 и второй 36 триггеры, первьй 37, второй 38 и третий 39 элементы И. Блок 1 памяти микрокоманд предназначен для хранения адресных и операционных частей микрокоманд, всех кодов логических условий, а также меток М1 и М2, управляющих работой устройства. Блок 2 памяти микрокоманд пред- назначен для хранения адресных и операционных частей микрокоманд, а регистры 3 и 4 микрокоманд - для записи и хранения микрокоманд, считываемых из блоков 1 и 2 памяти соответственно. Регистр 3 содержит поле 3 , в котором записьшается адрес следующей микрокоманды из блока 2 или 1 памяти, поле 32, где содержится код операционной части микрокоманды, поле 3, в котором находятся коды логических условий, поле 3, которое содержит метку Ml, равную единице, если в поле 3-, записан код логических условий для микрокоманд, хранимых во втором блоке 2 памяти микрокоманд, поле 3g , которое содержит метку М2, равную единице, если следующая микрокоманда считывается из первого блока 1 памяти микрокоманд. Регистр 4 содержит поле 4, в котором записывается операционная часть микрокоманды, и поле 4д,в котором задается адрес следующей микрокоманды из блока 1 памяти.

Регистр 5 логических условий предназначен для считывания на один такт по метке Ml кода логических услов яй из блока 1 памяти.

Коммутатор 6 предназначен для передачи в устройство кода операции с входа 21 или адреса очередной микрокоманды из блока 2 или 1 памяти,,

Коммутатор 7 служит для управления вьщачей устройством кодов микроопераций, поступающих из блока 1 или 2 памяти, и осуществляет вьщачу сигналов микрооперацийi проходящих через блоки элементов И 29 и 30 и блок элемештов ИЛИ в соответствие с синхроимпульсами, поступающими с выходов коммутаторов 8 и 9.

Элементы задержки предназначены для задержки синхроимпульсов на время занесения информации в регистры 3 и 4, а коммутаторы 8 и 9 - для перекоммутации синхронизирующих импульсов, считывающих микрокоманды из блока 1 или 2 памяти при необходимости повторного обращения к первому блоку 1 памяти микрокоманд.

Мультиплексоры 1Ои 11 служат для вьщеления значений логических условий, поступающих на группу входов 23 устройства, в соответствии с кодом логических условий, поступающим на управляющие входы мультиплексоров с выхода поля логических условий 3 для мультиплексора 10 или с выхода регистра 5 логических условий для мультиплексора 11.

Мультиплексоры 10 и 11 реализуют логические функции следующего вида:

.,.Я.хДс...сС..о г з- п-где значения i-го логического

условия-,

at-- значения j-ro разряда двоичного кода номера логического условия, . ( J - число логи-чес

ких условий)о

Триггер 12 служит для управления пуском и остановом устройства, а триггер 13 - для формирования сигналов, управляющих работой коммутаторов 8 :я 9.

Блох 14 (фиг. 3) синхронизирует р&боту устройства по тактовым импульсам f Jr Г с выходов 28, 28,g, j28. соответственно.

На триггерах 35 и 36 собран двухразрядный счетчик, который управачет

0326 0

элементами И 37-39. Триггеры 35 и 36 срабатьвают по заднему фронту импульса. Импульсы последовательно появляются из, выходах генератора.

Группа элементов И 15 предназначена для управления поступлением адреса следующей микрокоманды в блок 2 памяти из блока 1 памяти { регистра 3)„ Элемент И 16 служит для управления передачей значений логических условий, поступающих с выхода -г/льтиплексора tO в соответствии со значением метки Ml , а элемент И 17 - для осуществления перетактовки триггера 13 по управляющей метке М2,

Элемент ИЛИ 18 предназначен для модификации младшего адресного разряда в микрокоманде ветвления, из блойа 1 памяти, элемент ИЛИ 19 Q модификации аналогичного разряда в микрокоманде ветвления из блока 2 памяти, а. элемент ИЛИ 20 - для формирования сигнала Конец команды.

Устройство работает следующим 5 образом,

В исходном состоянии все элементы памяти обнулены. При этом триггер 13, а также один из триггеров, формирующих сигналь; на выходах 25 или 26 регистров 3 и 4, дложны быть в единичном состоянии о С входа 21 на коммзтатор 6 поступает код операции (начальный адрес микрокоманды). После прихода, сигнала Пуск - с входа 22 триггер 12 разрешает работу генера гора 14, Тогда тактовый импульс ц через коммз.Т.атор S поступает ка синхровход регистра 3 микрокоманд и разрешает считывание первой микрокоманда; из блока I памяти После этого адрес следующей микрокоманды из блока 2 поступает на входы блока элементов И 15. При разрешающем сигнале на их втором входе адрес поступает на вход блока 2 памяти. По управллющег гз импульсу f триггер 13 ycтaнaвJтавaeтcя в нулевое положение. По следующему за ним импульсу -Т, 5 который через коммутатор 9 поступав на. синхровход ре гкстра 4 р/шкрокоманд., происходит считывание следуюш;ей микрокоманды.,

Затек вновь появляется синхрош пус и® вьш:оде 282 (фиг. 5), который устанавливаем триггер 13 в 5 едикичное состояние. Следующий за иш.{ синхроимпульс проходит че.рез коммутатор 8 и заносит в регистр 3 очередную микрокоманду кз блока 1 памяти в соответствии с адресом, поступающим из поля 4„ регистра 4 через коммутатор 6. Далее работа устрочст|ва продолжается аналогичным образом. Выдача микрооперационных частей на вькоды 24 осуществляется регистоя.ми 3 и 4 в соответствии с управляющими сигналами от коммутаторов 8 и 9. Если в процессе ньшолнения микропрограммы необходимо дважды обратиться к блоку 1 памяти, то в поле 3, считывается метка М2 1, Тогда адрес следующей микрокоманда из поля 3 по разрешающему сигналу, подава емому с поля 3g регистра 3 микрокоманд, поступает на вход блока 1 памяти. Поскольку по импульсу fj три гер 13 своего состояния (нулевого) не изменяет (элемент И 17 закрыт), то по следующему за ним импульсу происходит считьшание микрокоманды в регистр 3 из блока 1 памяти. При необходимости реализации микрокоманды ветвления из блока 1 памяти код номеров проверяемых логических условий с поля 3 регистра 3 пос тупает на первые входы мультиплексора 10, на вторые его входы 23 поступает код значений логических условий после чего по разрешающему нулевому сигналу метки Ml с поля 3. регистра 3 на элементе ИЛИ 18 происходит м дификация младшего разряда адреса сл дующей микрокоманды. В этой микрокоманде в младшем р.аз ряде адреса записан нуль и, если логическое условие равно единице, в младшем разряде исполнительного адре са также формируется единица. При реализации микрокоманды ветвления из блока 1 памяти код номеров проверяемых логических условий задается в формате предыдущей микрокоман ды из блока 1 памяти. На входы 23 мультиплексора 11 подается код логических условий. По тактовому импуль су Г (или 1Г) из блока 2 памяти счихъшается очередная микрокоманда. В регистр 5 по единичному значению мет ки Ml очередным тактовым импульсом ti (С) заносится код проверяемых логических условий, после чего он поступает на управляющий вход мультиплексора 11. Сигнал с выхода мультиплексора 11 на элементе ИЛИ 19 модифицирует младший разряд адреса очередной микрокоманды, которая записывается в регистр 4 по тому же тактовому импульсу. При необходимости реализации нескольких микроконмад ветвеления из блока 1 памяти, метка М2 с поля Зг- блокирует через элемент И 17 триггер 13 и входа блока 2 памяти, разрешая при этом поступление адреса очередной микрокоманды с выхода поля 3 регистра микрокоманд через коммутатор 6 на вход блока 1 памяти. По тактовым импульсамL исХ считы ваются микрокоманды из блока 1 памяти до тех пор, пока метка М2 не разблокирует триггер 13, после чего устройство функционирует как описано выше. Обнуление содержимого регистра 5 происходит в случае отсутствия метки М1 очередным тактовым и шульсом. Это происходит вследствие того, что при подаче нулевого сигнала rta .Vвход регистра блокируется подача информации на D-ВХОДЫ и очередным импульсом в триггер регистра 5 записывается нулевой код. Переход к выполнению очередного кода операции осуществляе тся после появления сигналов на одном из выходов 25 или 26. По этой микрооперации элемент ИЛИ 20 разрешает прохождение кода операции через коммутатор 6. Для того, чтобы не фиксировать микрооперацию конца команды за определенным блоком памяти, при считывании последней микрокоманды микропрограммы из блока 1 памяти в поле 3 записывается единица, по которой осуществляется перетактовка работы устройства. По окончании работы с выхода 27 на R-вход триггера 12 поступает сигнал конца работы, блокирующий генератор 14. Таким образом, в предлагаемом устройстве за счет увеличения коэффициента использования памяти микрокоманд уменьшается объем оборудования по сравнению с известным устрой-ством.

Фиг.2

5 J7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1972 |

|

SU437072A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-23—Публикация

1983-06-03—Подача