Риг. 1

Изобретение относится к автоматике и вычислительной технике и предназначено для управления ферментационными установками для культивирова- , ния бактериальных культур с обеспечением заданных технологических параметров в лабораторных и промышленных условиях.

Целью изобретения является повы- JQ шение надежности системы управления.

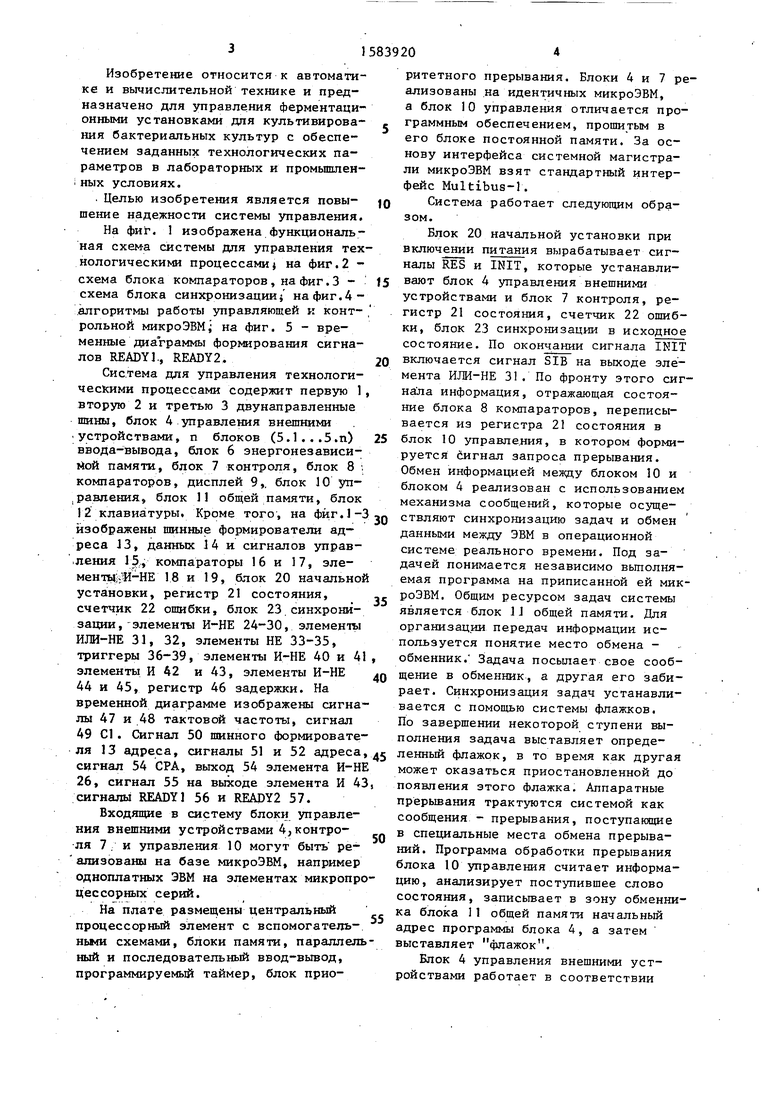

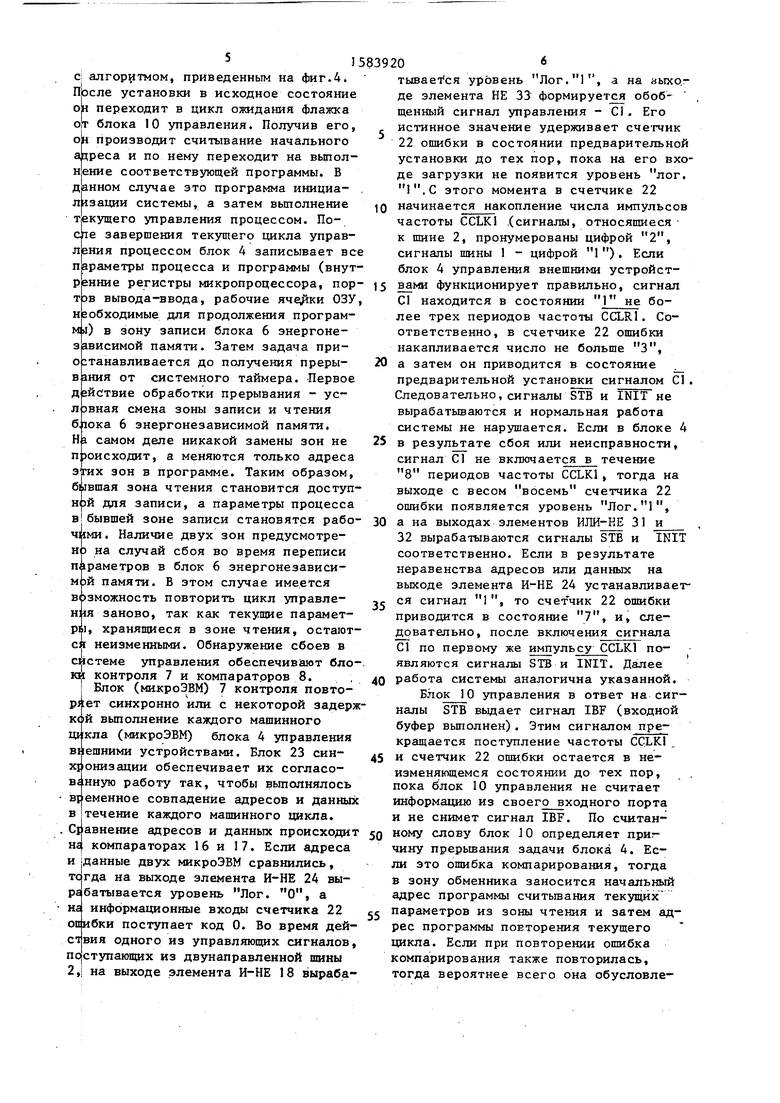

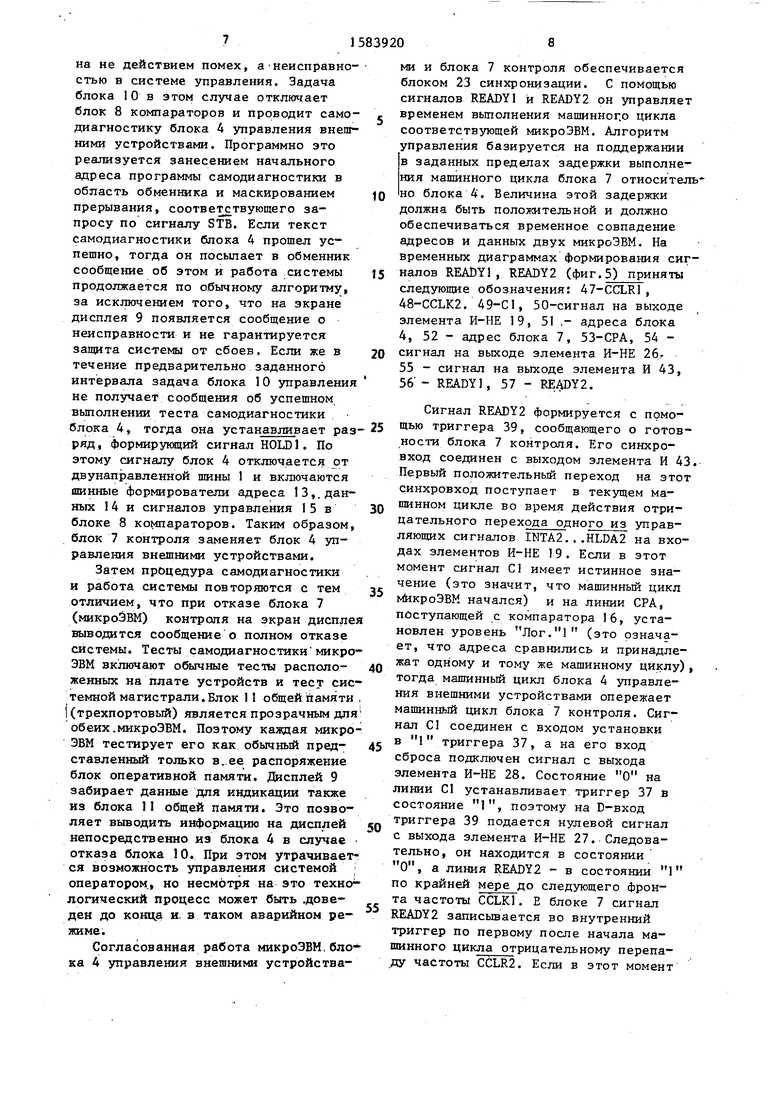

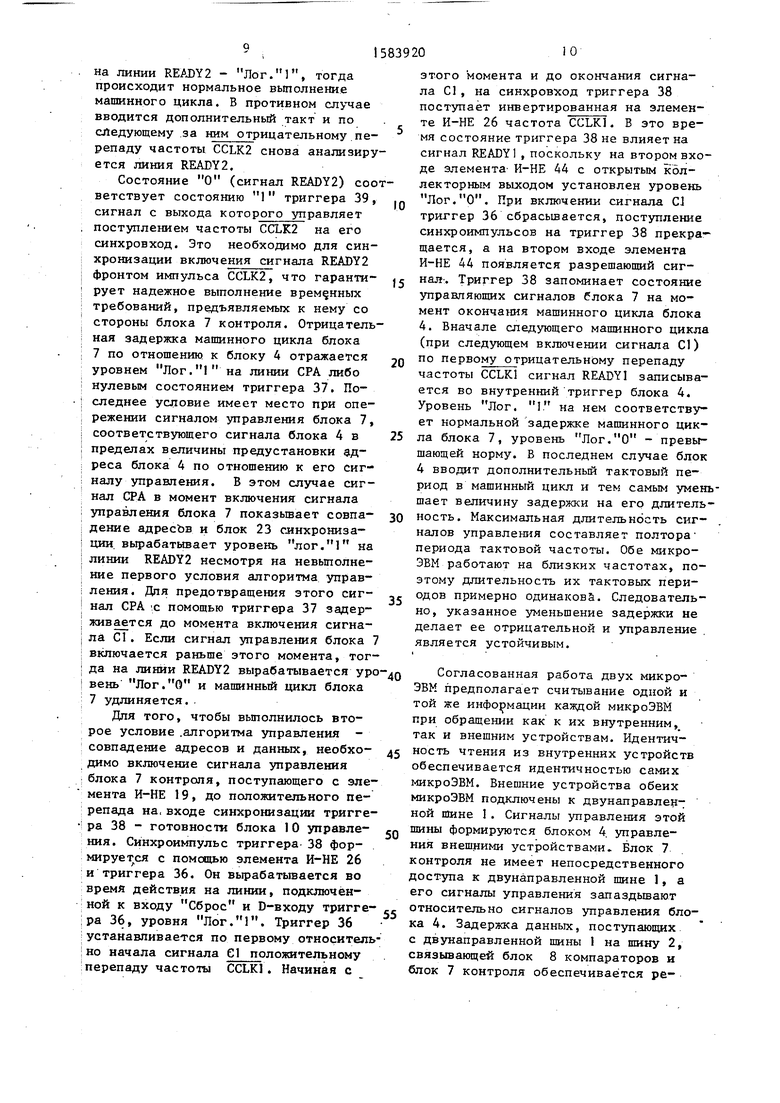

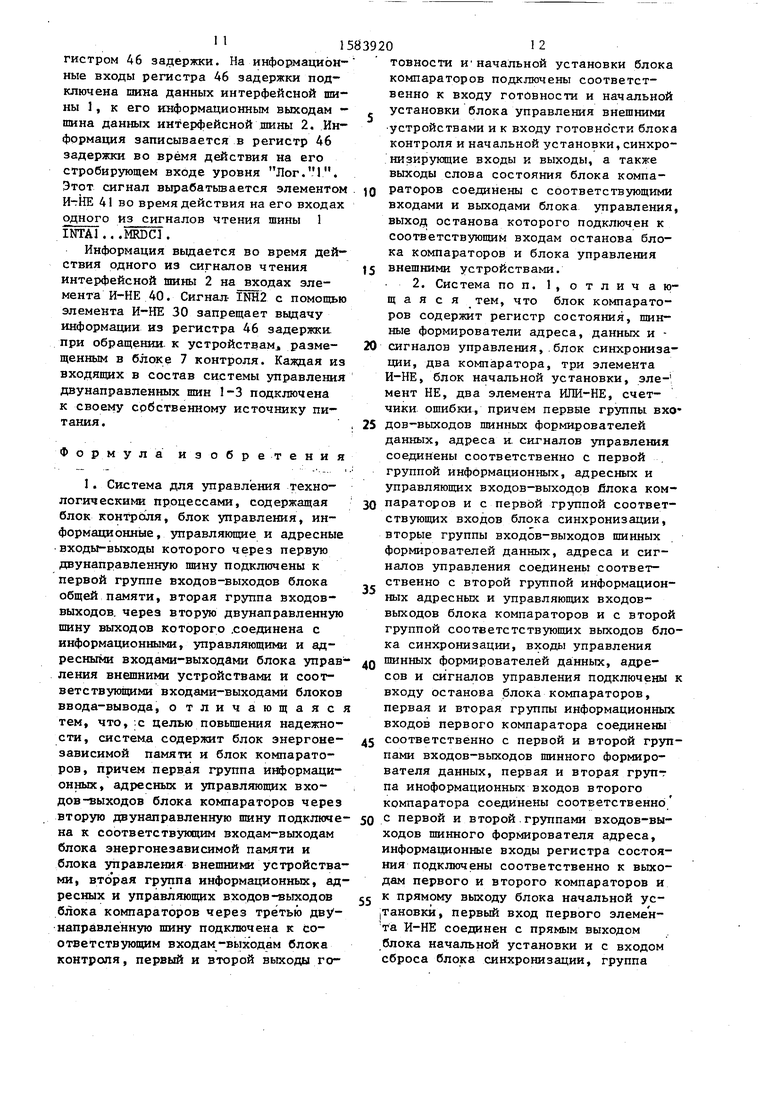

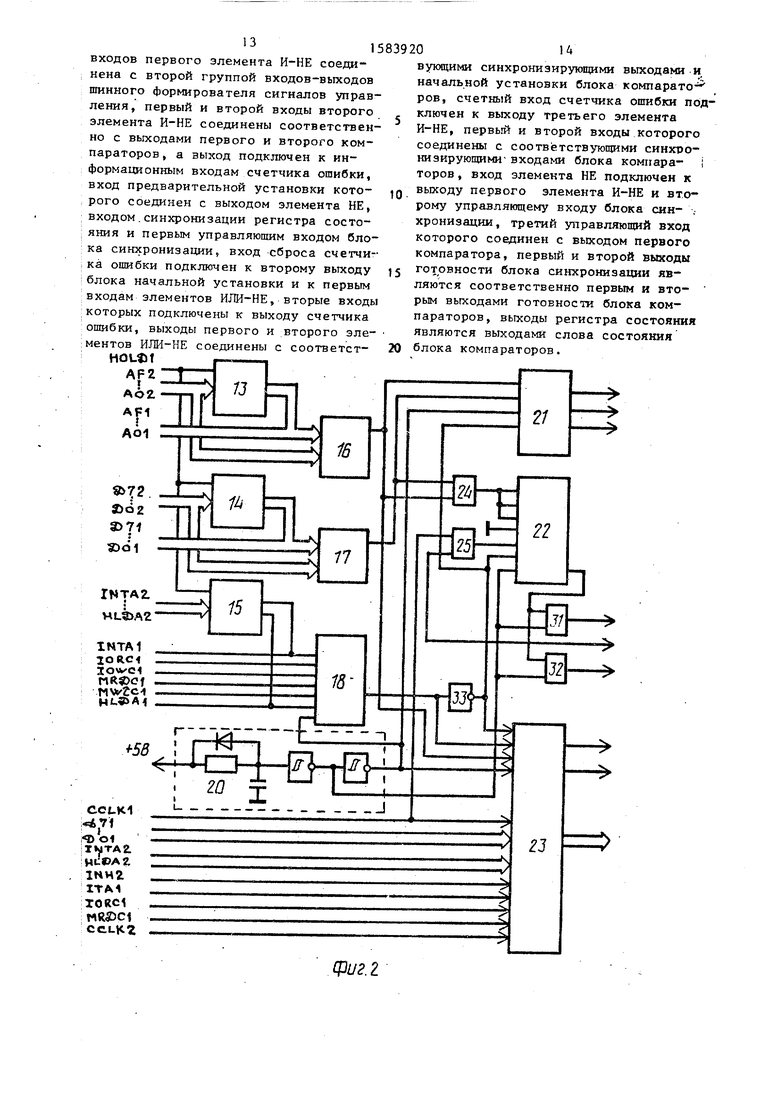

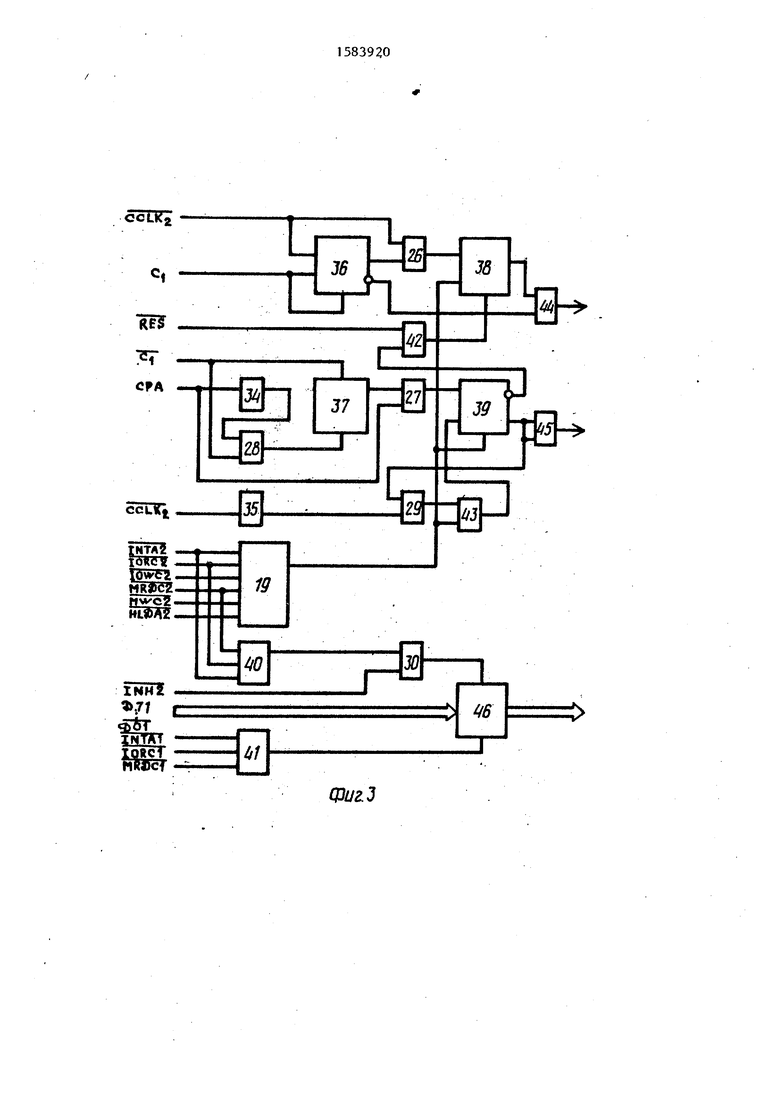

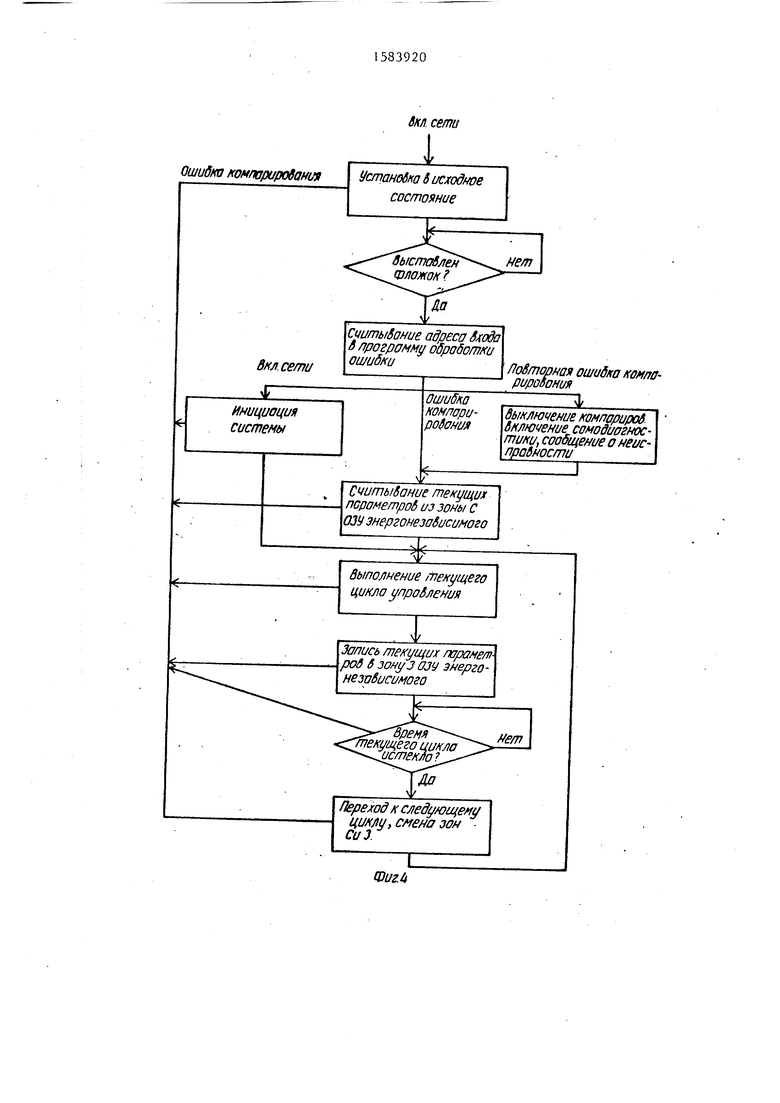

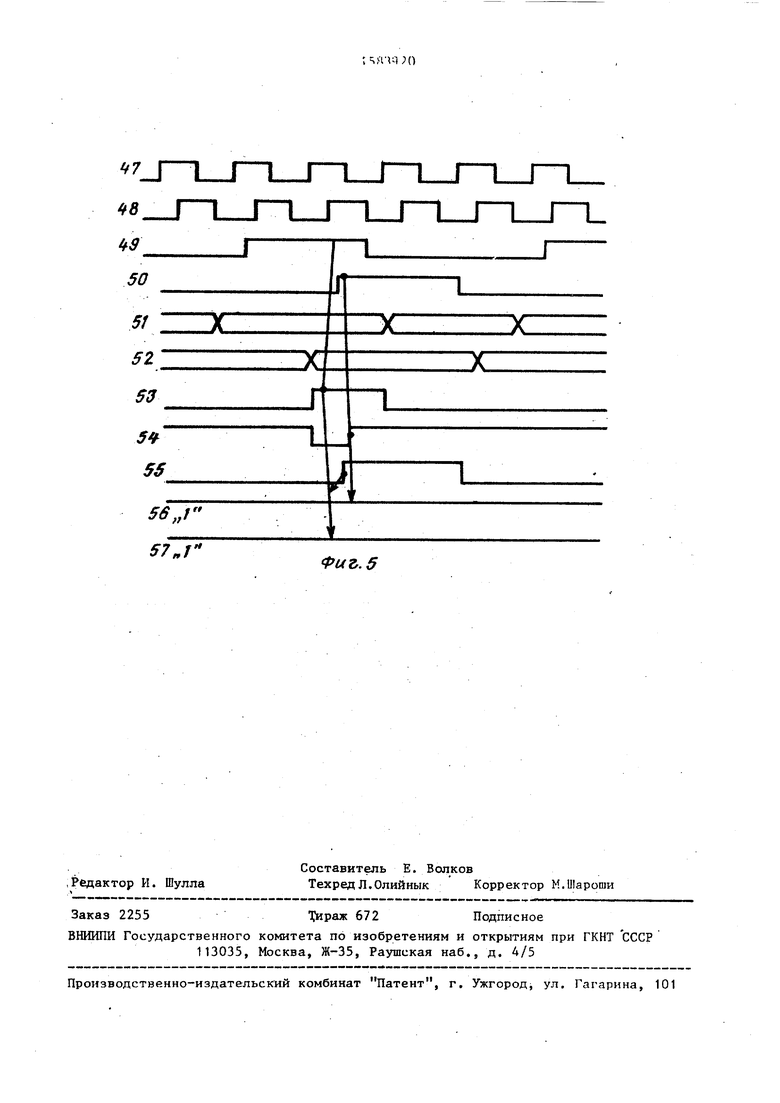

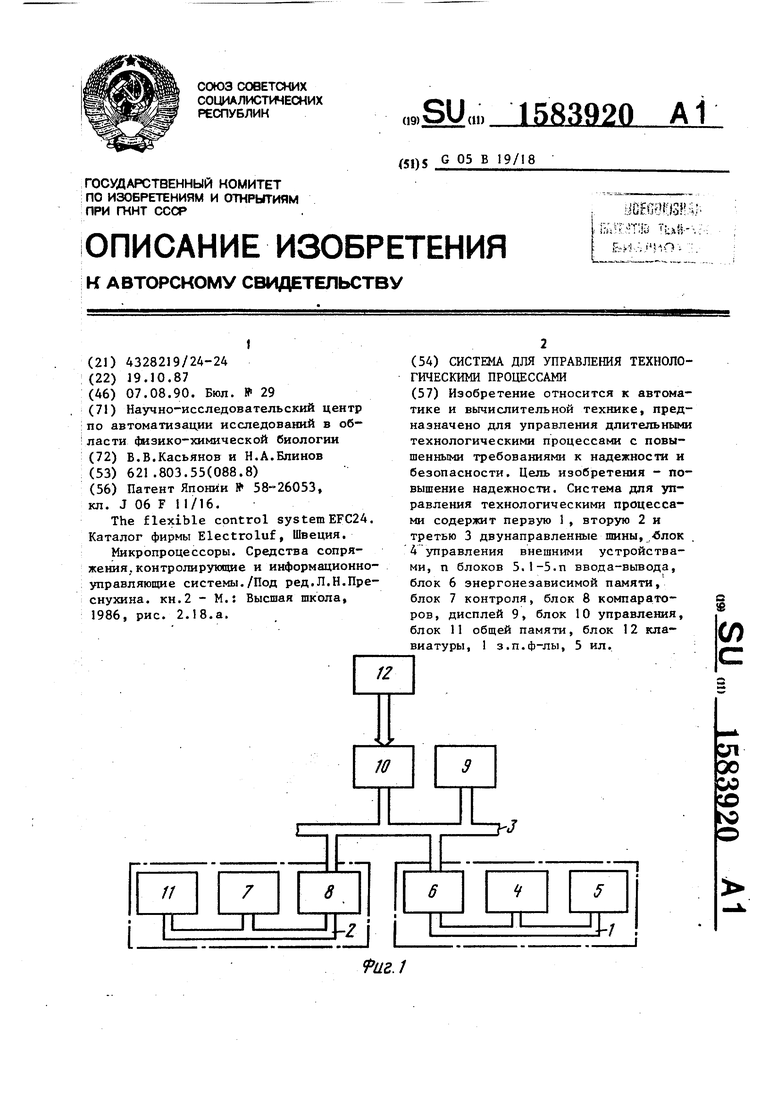

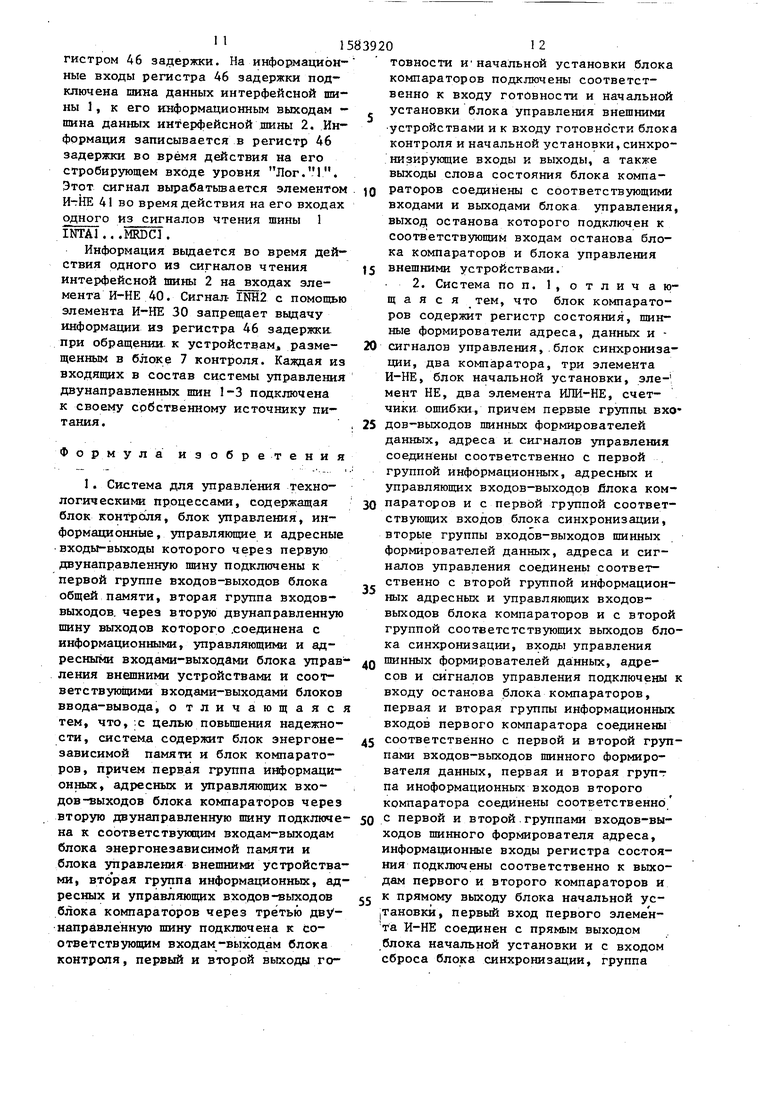

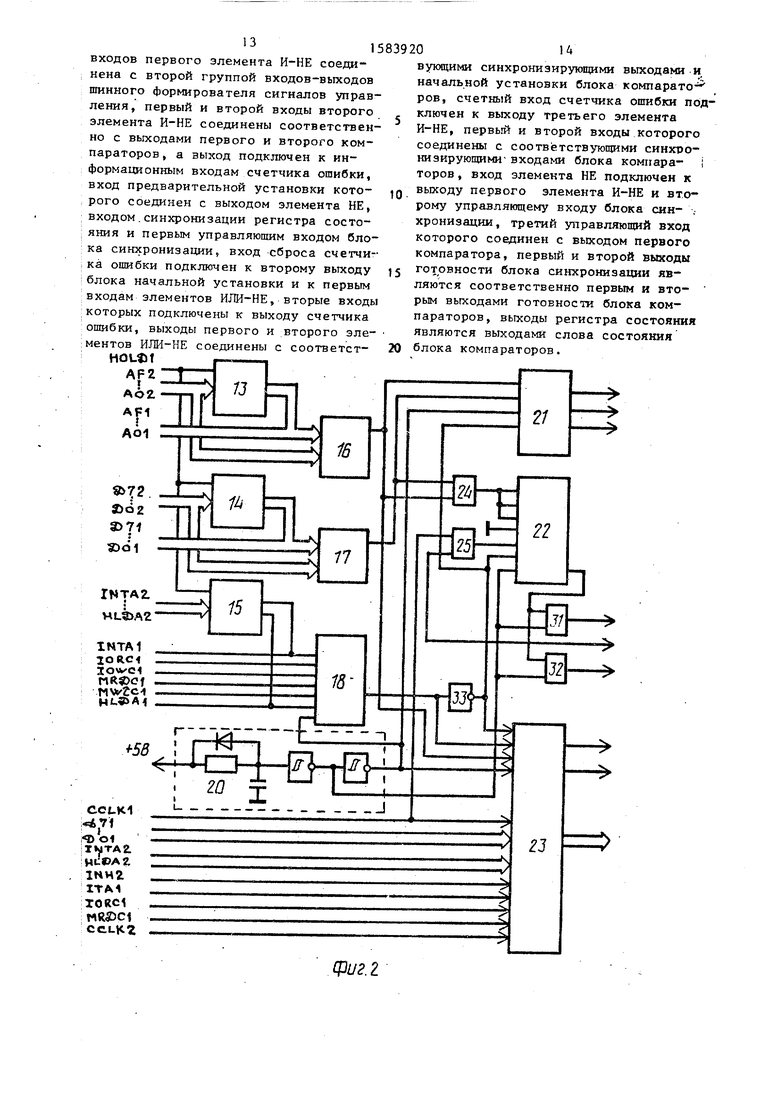

На фиг. 1 изображена функциональная схема системы для управления технологическими процессамиj на фиг.2 - схема блока компараторов, на фиг.3 - 15 схема блока синхронизации; на фиг.4- алгоритмы работы управляющей к контрольной микроЭВМ; на фиг. 5 - временные диаграммы формирования сигналов READY, READY2.20

Система для управления технологическими процессами содержит первую 1, вторую 2 и третью 3 двунаправленные шины, блок 4 управления внешними устройствами, п блоков (5.1...5.п) 25 ввода-вывода, блок 6 энергонезависимой памяти, блок 7 контроля, блок 8 компараторов, дисплей 9, блок 10 управления, блок 11 общей памяти, блок 12 клавиатуры, Кроме того, на фиг.1-3зд изображены шинные формирователи адреса 13, данных 14 и сигналов управления 15, компараторы 16 и 17, элементы Л5-НЕ 18 и 19, блок 20 начальной установки, регистр 21 состояния,„

счетчик 22 ошибки, блок 23 синхронизации, элементы И-НЕ 24-30, элементы ИЛИ-НЕ 31, 32, элементы НЕ 33-35, триггеры 36-39, элементы И-НЕ 40 и 41, элементы И 42 и 43, элементы И-НЕ дд 44 и 45, регистр 46 задержки. На временной диаграмме изображены сигналы 47 и 48 тактовой частоты, сигнал 49 С1. Сигнал 50 шинного формирователя 13 адреса, сигналы 51 и 52 адреса, сигнал 54 СРА, выход 54 элемента И-НЕ 26, сигнал 55 на выходе элемента И 43, сигналы READY 1 56 и READY2 57.

Входящие в систему блоки управления внешними устройствами 4,контро- ля 7 и управления 10 могут быть ре- ализованы на базе микроЭВМ, например одноплатных ЭВМ на элементах микропроцессорных серий.

На плате размещены центральный процессорный элемент с вспомогательными схемами, блоки памяти, параллель ный и последовательный ввод-вывод, программируемый таймер, блок прио,- 55

, JQ

15 20

25 зд „

, дд ,

55

ритетного прерывания. Блоки 4 и 7 реализованы на идентичных микроЭВМ, а блок 10 управления отличается программным обеспечением, прошитым в его блоке постоянной памяти. За основу интерфейса системной магистрали микроЭВМ взят стандартный интерфейс Multibus-1.

Система работает следующим образом.

Блок 20 начальной установки при включении питания вырабатывает сигналы RES и INIT, которые устанавливают блок 4 управления внешними устройствами и блок 7 контроля, регистр 21 состояния, счетчик 22 ошибки, блок 23 синхронизации в исходное состояние. По окончании сигнала INIT включается сигнал SIB на выходе элемента ИЛИ-НЕ 31. По фронту этого сигнала информация, отражающая состояние блока 8 компараторов, переписывается из регистра 21 состояния в блок 10 управления, в котором формируется бигнал запроса прерывания. Обмен информацией между блоком 10 и блоком 4 реализован с использованием механизма сообщений, которые осуществляют синхронизацию задач и обмен данными между ЭВМ в операционной системе реального времени. Под задачей понимается независимо выполняемая программа на приписанной ей микроЭВМ. Общим ресурсом задач системы является блок 11 общей памяти. Для организации передач информации используется понятие место обмена - обменник. Задача посылает свое сообщение в обменник, а другая его забирает. Синхронизация задач устанавливается с помощью системы флажков. По завершении некоторой ступени выполнения задача выставляет определенный флажок, в то время как другая может оказаться приостановленной до появления этого флажка. Аппаратные прерывания трактуются системой как сообщения - прерывания, поступающие в специальные места обмена прерываний. Программа обработки прерывания блока 10 управления считает информацию, анализирует поступившее слово состояния, записывает в зону обменни- ка блока 11 общей памяти начальный адрес программы блока 4, а затем выставляет флажок.

Блок 4 управления внешними устройствами работает в соответствии

с алгоритмом, приведенным на фиг.4. ПЬсле установки в исходное состояние oh переходит в цикл ожидания флажка блока 10 управления. Получив его, oh производит считывание начального адреса и по нему переходит на выполнение соответствующей программы. В данном случае это программа инициализации системы, а затем выполнение текущего управления процессом. По- спе завершения текущего цикла управления процессом блок 4 записывает все параметры процесса и программы (внутренние регистры микропроцессора, пор- тэв вывода-ввода, рабочие ячейки ОЗУ, необходимые для продолжения программа) в зону записи блока 6 энергонезависимой памяти. Затем задача приостанавливается до получения прерывания от системного таймера. Первое действие обработки прерывания - ус- лэвная смена зоны записи и чтения блока 6 энергонезависимой памяти. Н1 самом деле никакой замены зон не пэоисходит, а меняются только адреса эгих зон в программе. Таким образом, бывшая зона чтения становится доступной для записи, а параметры процесса в бывшей зоне записи становятся рабочими. Наличие двух зон предусмотрено на случай сбоя во время переписи параметров в блок 6 энергонезависимой памяти. В этом случае имеется возможность повторить цикл управления заново, так как текущие параметры, хранящиеся в зоне чтения, остаются неизменными. Обнаружение сбоев в системе управления обеспечивают блоки контроля 7 и компараторов 8.

Блок (микроЭВМ) 7 контроля повто- рАет синхронно или с некоторой задержкой выполнение каждого машинного вдкла (микроЭВМ) блока 4 управления внешними устройствами. Блок 23 синхронизации обеспечивает их согласованную работу так, чтобы выполнялось

BJ еменное совпадение адресов и данных в течение каждого машинного цикла.

Сравнение адресов и данных происходит н4 компараторах 16 и 17. Если адреса и данные двух микроЭВМ сравнились, тогда на выходе элемента И-НЕ 24 вы- ра

на

опибки поступает код 0. Во время действия одного из управляющих сигналов, поступающих из двунаправленной шины 2, на выходе элемента И-НЕ 18 вырабабатывается уровень Лог. О, а информационные входы счетчика 22

тываетЪя уровень Лог. М, а на dbixo- де элемента НЕ 33 формируется обобщенный сигнал управления - С1. Его истинное значение удерживает счетчик 22 ошибки в состоянии предварительной установки до тех пор, пока на его входе загрузки не появится уровень лог. 1,С этого момента в счетчике 22 начинается накопление числа импульсов

частоты CCLK1 (сигналы, относящиеся к шине 2, пронумерованы цифрой 2, сигналы шины 1 - цифрой 1). Если блок 4 управления внешними устройст5 вами функционирует правильно, сигнал С1 находится в состоянии 1 не более трех периодов частоты CCLR1. Соответственно, в счетчике 22 ошибки накапливается число не больше 3,

0 а затем он приводится в состояние

предварительной установки сигналом С1. Следовательно, сигналы STB и INIT не вырабатываются и нормальная работа системы не нарушается. Если в блоке 4

5 в результате сбоя или неисправности, сигнал С1 не включается в течение 8 периодов частоты CCLK1, тогда на

выходе с весом восемь счетчика 22 ошибки появляется уровень Лог.1,

а на выходах элементов ИЛИ-КЕ 31 н

32 вырабатываются сигналы STB и INIT соответственно. Если в результате неравенства адресов или данных на выходе элемента И-НЕ 24 устанавливает- ся сигнал 1 , то счетчик 22 ошибки приводится в состояние 7, и, следовательно, после включения сигнала С1 по первому же импульсу CCLK1 появляются сигналы STB и INIT. Далее работа системы аналогична указанной.

Блок 10 управления в ответ на сигналы STB выдает сигнал IBF (входной буфер выполнен). Этим сигналом пре- кращается поступление частоты CCLK1 и счетчик 22 ошибки остается в неизменяющемся состоянии до тех пор, пока блок 10 управления не считает информацию из своего входного порта и не снимет сигнал IBF. По считанному слову блок 10 определяет причину прерывания задачи блока 4. Если это ошибка компарирования, тогда в зону обменника заносится начальный адрес программы считывания текущих параметров из зоны чтения и затем адрес программы повторения текущего цикла. Если при повторении ошибка компарирования также повторилась, тогда вероятнее всего она обусловлена не действием помех, а неисправностью в системе управления. Задача блока 10 в этом случае отключает блок 8 компараторов и проводит само- диагностику блока 4 управления внешними устройствами. Программно это реализуется занесением начального адреса программы самодиагностики в область обменника и маскированием прерывания, соответствующего запросу по сигналу STB. Если текст самодиагностики блока 4 прошел успешно, тогда он посылает в обменник сообщение об этом и работа системы продолжается по обычному алгоритму, за исключением того, что на экране дисплея 9 появляется сообщение о неисправности и не гарантируется защита системы от сбоев. Если же в течение предварительно заданного интервала задача блока 10 управления не получает сообщения об успешном выполнении теста самодиагностики блока 4, тогда она устанавливает раз ряд, формирующий сигнал HOLD 1. По этому сигналу блок 4 отключается от двунаправленной шины 1 и включаются шинные формирователи адреса ..данных 14 и сигналов управления 15 в блоке 8 компараторов. Таким образом, блок 7 контроля заменяет блок 4 управления внешними устройствами.

Затем процедура самодиагностики и работа системы повторяются с тем отличием, что при отказе блока 7 (микроэвм) контроля на экран диспле выводится сообщение о полном отказе системы. Тесты самодиагностики микро ЭВМ включают обычные тесты располо- женных на плате устройств и тест системной магистрали. Блок 1 1 общей памяти I (трехпортовый) является прозрачным для обеих.микроЭВМ. Поэтому каждая микро ЭВМ тестирует его как обычный пред- ставленный только в.ее распоряжение блок оперативной памяти. Дисплей 9 забирает данные для индикации также из блока 11 общей памяти. Это позволяет выводить информацию на дисплей непосредственно из блока 4 в случае отказа блока 10. При этом утрачивается возможность управления системой оператором, но несмотря на это технсг логический процесс может быть .дове- ден до конца и- в таком аварийном режиме.

Согласованная работа микроЭВМ,блока 4 управления внешними устройствами и блока 7 контроля обеспечивается блоком 23 синхронизации. С помощью сигналов READYI и READY2 он управляет временем выполнения машинного цикла соответствующей микроЭВМ. Алгоритм управления базируется на поддержании в заданных пределах задержки выполнения машинного цикла блока 7 относително блока 4. Величина этой задержки должна быть положительной и должно обеспечиваться временное совпадение адресов и данных двух микроЭВМ. На временных диаграммах формирования сигналов REAbYl, READY2 (фиг.5) приняты следующие обозначения: 47-CCLR1, 48-CCLK2. 49-С1, 50-сигнал на выходе элемента И-НЕ 19, 51 ,- адреса блока 4, 52 - адрес блока 7, 53-СРА, 54 - сигнал на выходе элемента И-НЕ 26. 55 - сигнал на выходе элемента И 43, 56- READY1, 57 - READY2.

Сигнал READY2 формируется с помощью триггера 39, сообщающего о готовности блока 7 контроля. Его синхро- вход соединен с выходом элемента И 43 Первый положительный переход на этот синхровход поступает в текущем машинном цикле во время действия отрицательного перехода одного из управляющих сигналов INTA2...HLDA2 на входах элементов И-НЕ 19. Если в этот момент сигнал С1 имеет истинное значение (это значит, что машинный цикл микроЭВМ начался) и на линии СРА, поступающей с компаратора 16, установлен уровень Лог.1 (это означает, что адреса сравнились и принадлежат одному и тому же машинному циклу) тогда машинный цикл блока 4 управления внешними устройствами опережает машинный цикл блока 7 контроля. Сигнал С1 соединен с входом установки в 1 триггера 37, а на его вход сброса подключен сигнал с выхода элемента И-НЕ 28. Состояние О на линии С1 устанавливает триггер 37 в состояние 1, поэтому на D-вход триггера 39 подается нулевой сигнал с выхода элемента И-НЕ 27. Следовательно, он находится в состоянии О, а линия READY2 - в состоянии 1 по крайней мере до следующего фронта частоты CCLK1. Е блоке 7 сигнал READY2 записывается во внутренний триггер по первому после начала машинного цикла отрицательному перепаду частоты CCLR2. Если в этот момент

на линии READY2 - Лог.), тогда происходит нормальное выполнение машинного цикла. В противном случае вводится дополнительный такт и по следующему за ним отрицательному перепаду частоты CCLK2 снова анализируется линия READY2.

Состояние О (сигнал READY2) сооветствует состоянию 1 триггера 39, сигнал с выхода которого управляет поступлением частоты CCLK2 на его синхровход. Это необходимо для синхронизации включения сигнала READY2 фронтом импульса CCLK2, что гарантирует надежное выполнение временных требований, предъявляемых к нему со стороны блока 7 контроля. Отрицательная задержка машинного цикла блока 7 по отношению к блоку 4 отражается уровнем Лог.1 на линии СРА либо нулевым состоянием триггера 37. Последнее условие имеет место при опережении сигналом управления блока 7, соответствующего сигнала блока 4 в пределах величины предустановки адреса блока 4 по отношению к его сигналу управления. В этом случае сигнал СРА в момент включения сигнала управления блока 7 показывает совпадение адресов и блок 23 синхронизации вырабатывает уровень лог. М на линии READY2 несмотря на невыполнение первого условия алгоритма управления. Для предотвращения этого сигнал СРА с помощью триггера 37 задерживается до момента включения сигнала С1. Если сигнал управления блока включается раньше этого момента, тогда на линии READY2 вырабатывается урвень Лог.О и машинный цикл блока 7 удлиняется.

Для того, чтобы выполнилось второе условие .алгоритма управления - совпадение адресов и данных, необходимо включение сигнала управления блока 7 контроля, поступающего с элемента И-НЕ 19, до положительного перепада на,входе синхронизации триггера 38 - готовности блока 10 управления. Синхроимпульс триггера 38 формируется с помощью элемента И-НЕ 26 и триггера 36. Он вырабатывается во время действия на линии, подключенной к входу Сброс и D-входу триггера 36, уровня Лог. Ч. Триггер 36 устанавливается по первому относително начала сигнала С1 положительному перепаду частоты CCLK1. Начиная с

0

5

0

5

0

5

0

5

0

5

этого момента и до окончания сигнала С1, на синхровход триггера 38 поступает инвертированная на элементе И-НЕ 26 частота CCLK. В это время состояние триггера 38 не влияет на сигнал READY , поскольку на втором входе элемента И-НЕ 44 с открытым кол- лек торным выходом установлен уровень Лог.О. При включении сигнала С1 триггер 36 сбрасывается, поступление синхроимпульсов на триггер 38 прекращается, а на втором входе элемента И-НЕ 44 появляется разрешающий сигнал. Триггер 38 запоминает состояние управляющих сигналов блока 7 на момент окончания машинного цикла блока 4. Вначале следующего машинного цикла (при следующем включении сигнала С1) по первому отрицательному перепаду частоты CCLK1 сигнал READY1 записывается во внутренний триггер блока 4. Уровень Лог. I на нем соответствует нормальной задержке машинного цикла блока 7, уровень Лог.О - превышающей норму. В последнем случае блок 4 вводит дополнительный тактовый период в машинный цикл и тем самым уменьшает величину задержки на его длительность. Максимальная длительность сигналов управления составляет полтора периода тактовой частоты. Обе микро- ЭВМ работают на близких частотах, поэтому длительность их тактовых периодов примерно одинакова. Следовательно, указанное уменьшение задержки не делает ее отрицательной и управление является устойчивым.

Согласованная работа двух микро- ЭВМ предполагает считывание одной и той же информации каждой микроЭВМ при обращении как к их внутренним, так и внешним устройствам. Идентичность чтения из внутренних устройств обеспечивается идентичностью самих микроЭВМ. Внешние устройства обеих микроЭВМ подключены к двунаправленной шине 1. Сигналы управления этой шины формируются блоком 4 управления внешними устройствами. Блок 7 контроля не имеет непосредственного доступа к двунаправленной шине , а его сигналы управления запаздывают относительно сигналов управления блока 4. Задержка данных, поступающих с двунаправленной шины 1 на шину 2, связывающей блок 8 компараторов и блок 7 контроля обеспечивается регистром 46 задержки. На информационные входы регистра 46 задержки подключена шина данных интерфейсной шины 1 , к его информационным выходам - шина данных интерфейсной шины 2. Информация записывается в регистр 46 задержки во время действия на его стробирующем входе уровня Лог. М. Этот сигнал вырабатывается элементом И-НЕ 41 во время действия на его входах одного из сигналов чтения шины 1 INTA1...MRDC.

Информация выдается во время действия одного из сигналов чтения интерфейсной шины 2 на входах элемента И-НЕ 40. Сигнал INH2 с помощью элемента И-НЕ 30 запрещает выдачу информации из регистра 46 задержки, при обращении к устройствам., размещенным в блоке 7 контроля. Каждая из входящих в состав системы управления двунаправленных шин 1-3 подключена к своему собственному источнику питания.

Формула изобретения

1. Система для управления технологическими процессами, содержащая блок контроля, блок управления, информационные, управляющие и адресные входы-выходы которого через первую двунаправленную шину подключены к первой группе входов-выходов блока общей памяти, вторая группа входов- выходов через вторую двунаправленную шину выходов которого .соединена с информационными, управляющими и адресными входами-выходами блока управления внешними устройствами и соответствующими входами-выходами блоков ввода-вывода, о тличающаяс тем, что, с целью повышения надежности, система содержит блок энергонезависимой памяти и блок компараторов, причем первая группа информационных, адресных и управляющих входов-выходов блока компараторов через вторую двунаправленную шину подключена к соответствующим входам-выходам блока энергонезависимой памяти и блока управления внешними устройствами, вто рая группа информационных, адресных и управляющих входов-выходов блока компараторов через третью двунаправленную шину подключена к соответствующим входам-выходам блока контроля, первый и второй выходы го

0

5

товности и1начальной установки блока компараторов подключены соответственно к входу готовности и начальной установки блока управления внешними устройствами и к входу готовности блока контроля и начальной установки, синхронизирующие входы к выходы, а также выходы слова состояния блока компараторов соединены с соответствующими входами и выходами блока управления, выход останова которого подключен к соответствующим входам останова блока компараторов и блока управления внешними устройствами.

1

о т л и ч а ю0

2. Система по п.

щ а я с я тем, что блок компараторов содержит регистр состояния, шинные формирователи адреса, данных и - сигналов управления, блок синхронизации, два компаратора, три элемента И-НЕ, блок начальной установки, эле- мент НЕ, два элемента ИЛИ-НЕ, счетчики ошибки, причем первые группы вхо 5 дов-выходов шинных формирователей данных, адреса и. сигналов управления соединены соответственно с первой группой информационных, адресных и управляющих входов-выходов .блока компараторов и с первой группой соответствующих входов блока синхронизации, вторые группы входов-выходов шинных формирователей данных, адреса и сигналов управления соединены соответственно с второй группой информационных адресных и управляющих входов- выходов блока компараторов и с второй группой соответстствуюших выходов блока синхронизации, входы управления шинных формирователей данных, адресов и сигналов управления подключены к входу останова блока компараторов, первая и вторая группы информационных входов первого компаратора соединены соответственно с первой и второй группами входов-выходов шинного формирователя данных, первая и вторая группа информационных входов второго компаратора соединены соответственно с первой и второй группами входов-выходов шинного формирователя адреса, информационные входы регистра состояния подключены соответственно к выходам первого и второго компараторов и к прямому выходу блока начальной установки, первый вход первого элемента И-НЕ соединен с прямым выходом блока начальной установки и с входом сброса блока синхронизации, группа

5

0

5

0

входов первого элемента И-НЕ соединена с второй группой входов-выходов шинного формирователя сигналов управления, первый и второй входы второго элемента И-НЕ соединены соответственно с выходами первого и второго компараторов, а выход подключен к информационным входам счетчика ошибки, вход предварительной установки кото- рого соединен с выходом элемента НЕ, входом.синхронизации регистра состояния и первым управляющим входом блока синхронизации, вход сброса счетчи-- ка ошибки подключен к второму выходу блока начальной установки и к первым входам элементов ИЛИ-НЕ, вторые входы которых подключены к выходу счетчика ошибки, выходы первого и второго эле- ментов ИЛИ-НЕ соединены с соответст-

вующими синхронизирующими выходами и начальной установки блока компарато-15 ров, счетный вход счетчика ошибки подключен к выходу третьего элемента И-НЕ, первый и второй входы которого соединены с соответствующими синхронизирующими входами блока компара- | торов, вход элемента НЕ подключен к выходу первого элемента И-НЕ и второму управляющему входу блока сил- . хронизации, третий управляющий вход которого соединен с выходом первого компаратора, первый и второй выходы готовности блока синхронизации являются соответственно первым и вто- рым выходами готовности блока компараторов, выходы регистра состояния являются выходами слова состояния блока компараторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Устройство для сопряжения однородной вычислительной структуры | 1987 |

|

SU1474682A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для отсчета времени | 1990 |

|

SU1784959A1 |

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1363212A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

Изобретение относится к автоматике и вычислительной технике,предназначено для управления длительными технологическими процессами с повышенными требованиями к надежности и безопасности. Цель изобретения - повышение надежности. Система для управления технологическими процессами содержит первую 1, вторую 2 и третью 3 двунаправленные шины, блок 4 управления внешними устройствами, N блоков 5.1-5.N, ввода-вывода, блок 6 энергонезависимой памяти, блок 7 контроля, блок 8 компараторов, дисплей 9, блок 10 управления, блок 11 общей памяти, блок 12 клавиатуры. 1 з.п.ф-лы, 5 ил.

Фиг. 2

CCLK2

ФшЗ

Ошибка компарированил

6мсети

Инициация системы

6м сети

1

Установка 6исходное состояние

Повторная ошибка компа- риробония

тики, сообщение о неисправности

Считыбание текущих псрометроб из зоны С ОЗУ энергонезависимого

Выполнение текущего цикла улро&ления

Запись текущих лораме/п роб 6 javyJ Ojy энерго- незябисимого

Переход к следующему циму, смена зон СиЗ

I Фиги

51 5Z

57 Г

Фиъ.5

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| Каталог фирмы Electroluf, Швеция | |||

| Микропроцессоры | |||

| Средства сопряжения, контролирующие и информационно- управляющие системы./Под ред.Л.Н.Пре- снухина | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1990-08-07—Публикация

1987-10-19—Подача