Изобретение относится к специализированным средствам цифровой вычислительной техники, предназначенным для выполнения процедуры дискретного преобразования Фурье (ДПФ), и может быть использовано в системах цифровой обработки сигналов в реальном масштабе времени.

Целью изобретения является повышение быстродействия.

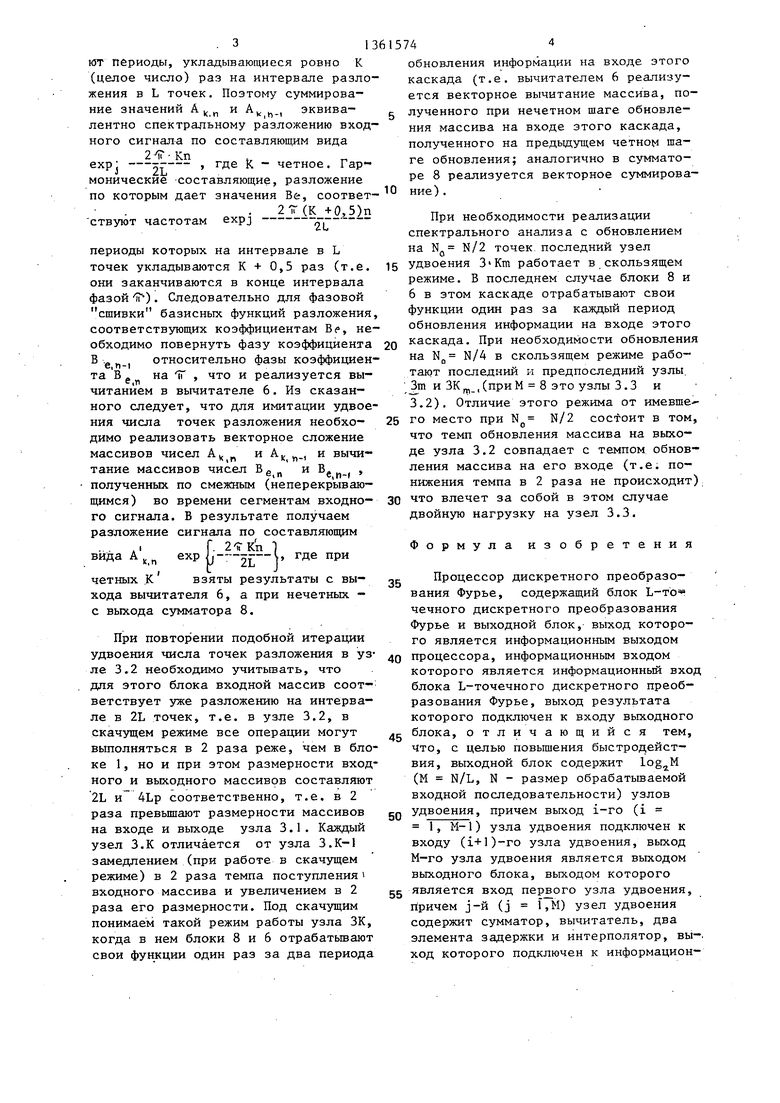

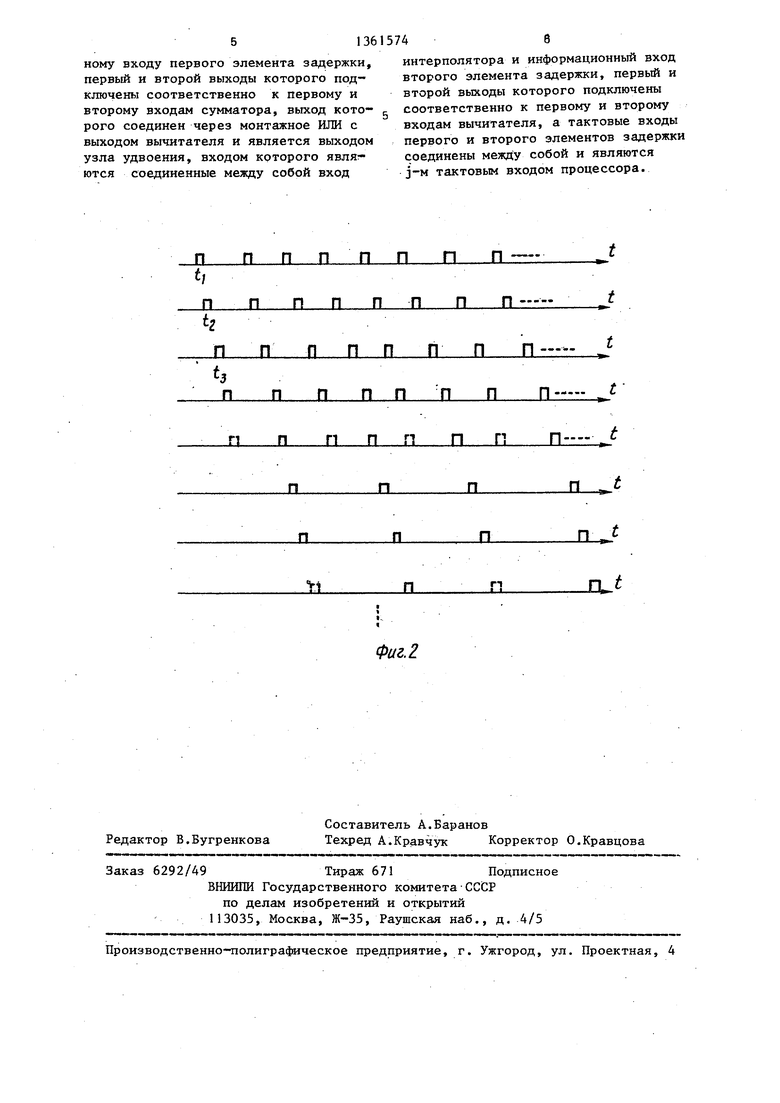

На фиг.1 представлена схема процессора; на фиг.2 - временные диаграммы его рабо ты.

Процессор дискретного преобразования Фурье (фиг.1) содержит блок L-точечного дискретного преобразования Фурье (ДПФ) 1, выходной блок 2, узлы удвоения (спектрального разрешения) 3.1-З.М, каждый из которых содержит интердолятор 4, элемент 5 задержки, вычитатель 6, элемент 7 задержки и сумматор 8.

Устройство работает следующим образом.

Входной массив из L комплексных выборок 1-го сегмента анализируемого сигнала параллельно подается в течение интервала времени 0-(Ъ-1)Д на вход блока 1. Далее в течение интервала времени Ьй-(2Ь-1)д на вход блока 1 подается массив из L выборок 2-го сегмента и т.д.

Подобная динамика обновления входного массива может быть рбеспе- чена, например, включением перед входом блока 1 буферного запоминающего устройства (ЗУ), имеющего входной коммутатор, два многоразрядных регистра сдвига и выходной коммутатор. Входной коммутатор подключает к входу буферного ЗУ вход 1-гр (2-го) регистра сдвига при подаче управляющего импульса на его 1-й (соответственно 2-й) управляющий вход. Выходг ной коммутатор подключает к выходу буферного ЗУ выход 1-го (2-го) регистра сдвига при подаче управляющего импульса на его 1-и (соответственно 2-й) управляющий вход. Разноимен ные управлякнцне входы коммутаторов попарно объединены и образуют 1-й и 2-и управляющие входы буферного ЗУ. Входы тактирования (сдвига) 1-го и 2-го регистров сдвига являются соответственно 3-м и 4-м входами тактирования буферного ЗУ. С момента включения входной коммутатор в течение L тактов работы подключает к входу буферного ЗУ вход 1-го регистра сдвига, выполняющего в этот период времени функцию 1-й линии задержки с отводами (под входом регистра подразумевается входная шина последовательного кода в каждом разряде кода последовательности обрабатываемых выборок). По завершении (L-l)-ro

такта осуществляется подключение выходным коммутатором на период времени Ьд -(2L-1)& выходной шины параллельного кода 1-го регистра сдвига (в каждом, разряде), т.е. отводов 1-й

линии задержки к векторному входу блока 1; при этом на указанный период времени 1-й регистр выполняет i функцию совокупности из L многоразрядных регистров хранения, а входным

коммутатором осуществляется подключение к входу буферного ЗУ входа 2-го регистра сдвига, которьШ р этот период времени выполняет функцию 2-й линии задержки с отводами. Таким

образом, путем поочередного изменения функций двух регистров обеспечивается поочередная подача на вход блока 1 массивов входных выборок . В процессе функционирования буферного

ЗУ реализуется подача синхроимпульсов с частотой на вход УЗ того из регистров сдвига, который в данной фазе работы выполняет функцию линии задержки с отводами.

Принцип действия .процессора состоит в следующем. Пусть, например, М 8 и Ng N L.-M. В этом случае все узлы удвоения спектрального разрешения работают в скачущем режиме. В

момент времени t, на вход блока 1 поступает совокупность лыборок 1-го сегмента отрабатываемого сигнала. В момент t на выходе блока 1 форми-: руются результаты ДПФ 1-го входного

массива. В момент t- на выходе блока 1 формируются результаты ДПФ 1-го входного массива. В момент t на выходе интерполятора 4 формируется LP интерполированных коэффициентов

Be, соответствующих L-точечному разложению входного сигнала по гармоническим составляющим, частоты которых расположены в серединах частотных интервалов между частотами, соответствующими коэффициентам ДПФ А,.

Гармонические составляющие, соответствующие ДПФ (А expj ----- ) имеLJ

Н5Т периоды, укладывающиеся ровно К (целое число) раз на интервале разложения в L точек. Поэтому суммирование значений А и А эквивалентно спектральному разложению входного сигнала по составляющим вида Кп

ехр;

2L

, где К - четное. Гармонические составляющие, разложение по которым дает значения Be, соответ

27(К +0,5)п ствуют частотам expj--

периоды которых на интервале в L точек укладываются К + 0,5 раз (т.е. они заканчиваются в конце интервала фазой 1). Следовательно для фазовой сшивки базисных функций разложения соответствующих коэффициентам Вр, необходимо повернуть фазу коэффициента В .g | относительно фазы коэффициента В на ТГ , что и реализуется вычитанием в вычитателе 6. Из сказанного следует, что для имитации удвоения числа точек разложения необхо- димо реализовать векторное сложение массивов чисел А и А, ., и вычитание массивов чисел Bg, и В j , полученных по смежным (неперекрывающимся) во времени сегментам входно- го сигнала. В результате получаем разложение сигнала по составляющим

7Кп

вида А

ехр

t2L

, где при

к.п

четных к взяты результаты с вы- хода вычитателя 6, а при нечетных - с выхода сумматора 8.

При повторении подобной итерации удвоения числа точек разложения в уз ле 3.2 необходимо учитьшать, что для этого блока входной массив соответствует уже разложению на интервале в 2L точек, т.е. в узле 3.2, в скачущем режиме все операции могут выполняться в 2 раза реже, чем в блоке 1, но и при этом размерности входного и выходного массивов составляют 2L и 4Lp соответственно, т.е. в 2 раза превьппают размерности массивов на входе и выходе узла 3.1. Каждый узел З.К отличается от узла З.К-1 замедлением (при работе в скачущем режиме) в 2 раза темпа поступления входного массива и увеличением в 2 раза его размерности. Под скачущим понимаем такой режим работы узла ЗК, когда в нем блоки 8 и 6 отрабатьшают свои функции один раз за два периода

обновления информации на входе этого каскада (т.е. вычитателем 6 реализуется векторное вычитание массива, полученного при нечетном шаге обновления массива на входе этого каскада, полученного на предьщущем четном шаге обновления; аналогично в сумматоре 8 реализуется векторное суммирование) .

При необходимости реализации спектрального анализа с обновлением на N N/2 точек, последний узел удвоения З Кт работает в,скользящем режиме. В последнем случае блоки 8 и 6 в этом каскаде отрабатывают свои функции один раз за каждый период обновления информации на входе этого каскада. При необходимости обновлени на Кд N/4 в скользящем режиме работают последний и предпоследний узлы. и ЗК„,,(приМ 8 это узлы 3.3 и 3.2). Отличие этого режима от имевше го место при Np N/2 состоит в том что темп обновления массива на выходе узла 3.2 совпадает с темпом обновления массива на его входе (т.е; понижения темпа в 2 раза не происходит что влечет за собой в этом случае двойную нагрузку на узел 3.3.

Формула изобретения

Процессор дискретного преобразования Фурье, содержащий блок L-TO чечного дискретного преобразования Фурье и выходной блок, выход которого является информационным выходом процессора, информационным входом которого является информационный вхо блока L-точечного дискретного преобразования Фурье, выход результата которого подключен к входу выходного блока, отличающийся тем, Что, с целью повышения быстродействия, выходной блок содержит (М N/L, N - размер обрабатьшаемой входной последовательности) узлов удвоения, причем выход i-ro (i 1, М-1) узла удвоения подключен к входу (i+l)-ro узла удвоения, выход М-го узла удвоения является выходом выходного блока, выходом которого является вход первого узла удвоения, причем j-й (J Г,М) узел удвоения содержит сумматор, вычитатель, два элемента задержки и интерполятор, вы ход которого подключен к информацион5136

ному входу первого элемента задержки, первьй и второй выходы которого подключены соответственно к первому и второму входам сумматора, выход кото рого соединен через монтажное ИЛИ с выходом вычитателя и является выходом узла удвоения, входом которого являг- ются соединенные между собой вход

Г1

П

п п п

п

п

Jrl

Редактор В.Бугренкова

Составитель А.Баранов

Техред А.Кравчзтс Корректор О.Кравцова

Заказ 6292/49Тираж 671Подписное

ВШШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

15746

интерполятора и информационный вход второго элемента задержки, первый и второй выходы которого подключены соответственно к первому и второму входам вычитателя, а тактовые входы первого и второго элементов задержки соединены между собой и являются J-M тактовым входом процессора.

п

п

п-

п

п

п t

JL

П

гг

Г1

П

rLt

Фаг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ФИЛЬТР | 1997 |

|

RU2123758C1 |

| Устройство для измерения относительной задержки импульсных сигналов | 1982 |

|

SU1068886A1 |

| РАДИОМОДЕМ | 2010 |

|

RU2460215C1 |

| Цифровой анализатор спектра | 1987 |

|

SU1413545A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Устройство для трехточечного быстрого преобразования Фурье | 1983 |

|

SU1107132A1 |

| Цифровой спектроанализатор | 1982 |

|

SU1092518A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1278886A1 |

| Анализатор спектра | 1987 |

|

SU1552117A1 |

Изобретение относится к специализированным средствам цифровой вы-: числительной техники, предназначенным для выполнения процедуры дискрет- - ного преобразования Фурье, и может быть использовано в системах цифровой обработки сигналов в реальном масштабе времени. Цель изобретения - повышение быстродействия. Поставленная цель достигается за счет того, что в состав процессора входят блок L-точечного дискретного преобразования Фурье 1, выходной блок 2, узел удвоения 3, интерполятор 4, элемент задержки 5, вычитатель 6, элемент задержки 7 и сумматор 8. 2 ил.

| Рабинер Л., Гоулд Б | |||

| Теория и применение цифровой обработки сигналов.- М.: Мир, 1978 | |||

| Кочемасов В.Н | |||

| и др | |||

| Комбинированные Фурье -.процессоры.- Зарубежная радиоэлектроника, 1985, № 2, с | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-12-23—Публикация

1986-07-25—Подача