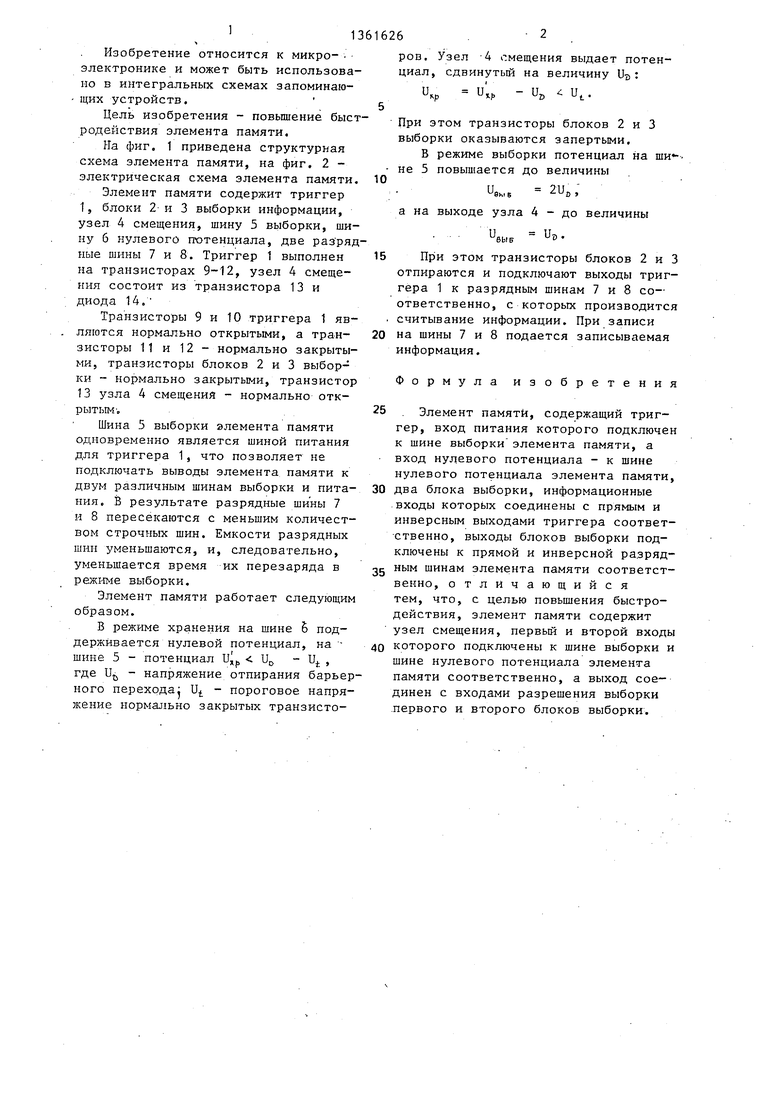

Фиг.1

Изобретение относится к микро- электронике и может быть использовано в интегральных схемах запоминаю- щих устройств, 5

Цель изобретения - повышение быстродействия элемента памяти.

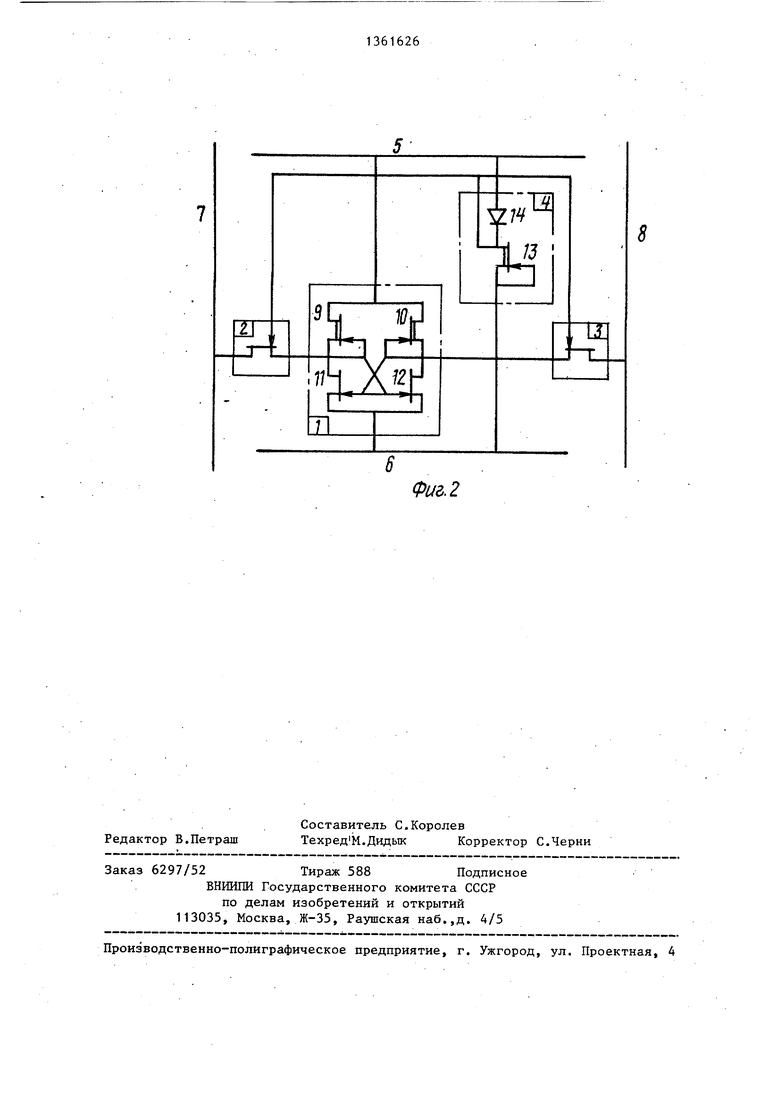

На фиг. 1 приведена структурная схема элемента памяти, на фиг. 2 - электрическая схема элемента памяти, 10

Элемент памяти содержит триггер 1, блоки 2- и 3 выборки информации, узел 4 смещения, шину 5 выборки, шину б нулевого тзтенциала, две раз ряд- ные шины 7 и 8, Триггер 1 выполнен 15 на транзисторах 9-12, узел 4 смещения состоит из транзистора 13 и диода 14.

Транзисторы 9 и 10 триггера 1 являются нормально открытыми, а тран- 20 зисторы 11 и 12 - нормально закрытыми, транзисторы блоков 2 и 3 выборки - нормально закрытыми, транзистор 13 узла 4 смещения - нормально открытым-.

Шина 5 выборки элемента памяти одновременно является шиной питания для триггера 1, что позволяет не подключать выводы элемента памяти к двум различным шинам выборки и пита- 30 НИН, В результате разрядные шины 7 и 8 пересекаются с меньшим количеством строчных шин. Емкости разрядных шип уменьшаются, и уменьшается время режиме выборки.

Элемент памяти работает следующим образом,

В режиме хранения на шине S поддерживается нулевой потенциал, на 40 шине 5 - потенциал U,jj U - U , где U - напряжение отпирания барьерного перехода; U - пороговое напряжение нормально закрытых транзисто, следовательно, их перезаряда в

25

35

5

1361626 . .

ров. Узел -4 смещения выдает потенциал, сдвинутый на величину UB:

и.

и

- Uz и,,

При этом транзисторы блоков 2 и 3 выборки оказываются запертыми,

В режиме выборки потенциал на не 5 повышается до величины

Usb,. 2U., а на выходе узла 4 - до величины

и

бЬШ

и.

При этом транзисторы блоков 2 и 3 отпираются и подключают выходы триггера 1 к разрядным шинам 7 и 8 соответственно, с которых производится считывание информации. При записи на шины 7 и 8 подается записываемая информация.

Формула изобретения

. Элемент памяти, содержащий триггер, вход питания которого подключен к шине выборки элемента памяти, а вход нулевого потенциала - к шине нулевого потенциала элемента памяти, два блока выборки, информационные входы которых соединены с прямым и инверсным выходами триггера соответственно, выходы блоков выборки подключены к прямой и инверсной разрядным шинам элемента памяти соответственно, отличающийся тем, что, с целью повьш1ения быстродействия, элемент памяти содержит узел смещения, первый и второй входы которого подключены к шине выборки и шине нулевого потенциала элемента памяти соответственно, а выход соединен с входами разрешения выборки .первого и второго блоков выборки.

Редактор В.Петраш

Составитель С.Королев

Техред М.Дидык Корректор С.Черни

Заказ 6297/52Тираж 588 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.,д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг., 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти (его варианты) | 1983 |

|

SU1164787A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Матричный накопитель | 1986 |

|

SU1343443A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1809466A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| Дешифратор на МДП-транзисторах | 1983 |

|

SU1455362A1 |

Изобретение относится к микроэлектронике и может быть использовано в интегральных схемах запоминающих устройств. Целью изобретения является повьшение быстродействия элемента памяти. Поставленная цель достигается за счет введения узла смещения 4, подключенного к шинам 5, 6 и блокам 2, 3 выборки информации. Шина 5 одновременно является шиной питания триггера, что позволяет не подключать выводы элемента памяти к двум различным шинам выборки и питания. В результате разрядные шины 7, 8 пересекаются с меньшим количеством строчных шин. Емкости разрядных шин уменьшаются, и,следовательно,уменьшается время их перезаряда в режиме выборки. 2 ил. с

| Ohwada К | |||

| et all | |||

| Ножевой прибор к валичной кардочесальной машине | 1923 |

|

SU256A1 |

| - Electron | |||

| Letters, 1982, V | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| Ino M | |||

| et all. | |||

| Estimation of GaAs Static RAM Perfomance | |||

| - IEEE trans, 1982, v | |||

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1987-12-23—Публикация

1986-01-07—Подача